这次的教程是如何为kv260构建硬件和软件组件,kv260作为一款自带fpga部分的som开发板来说,我们可以根据自己的需求,自由的修改fpga上面的硬件部分,来适配新的应用程序。

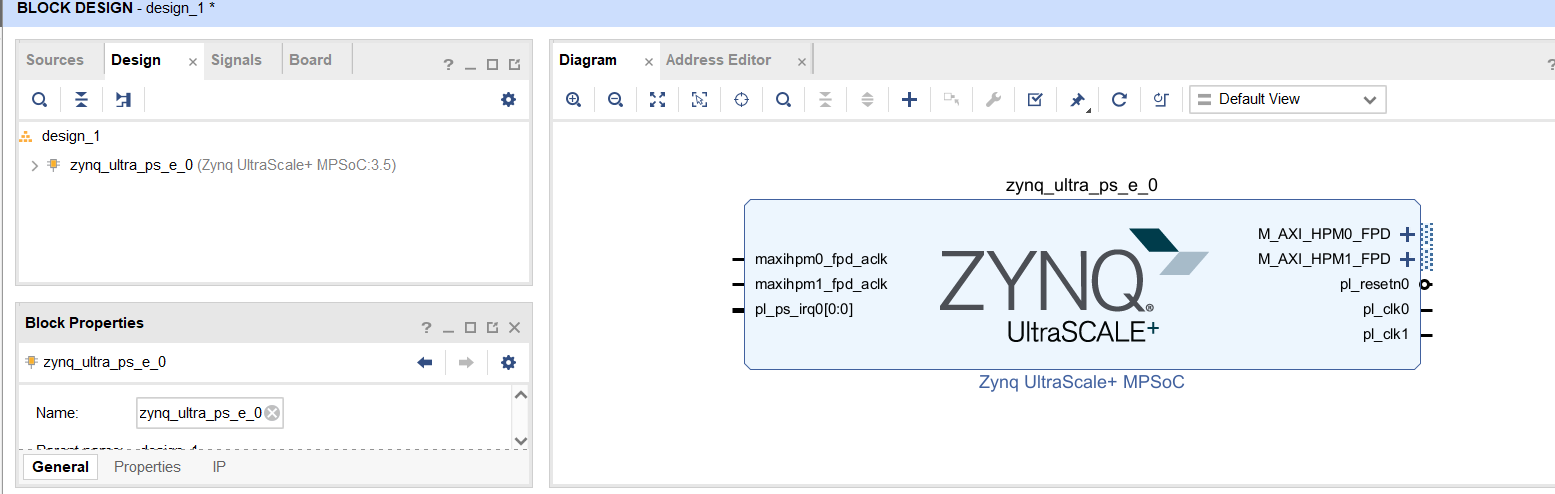

一.Vivado和kv260连接

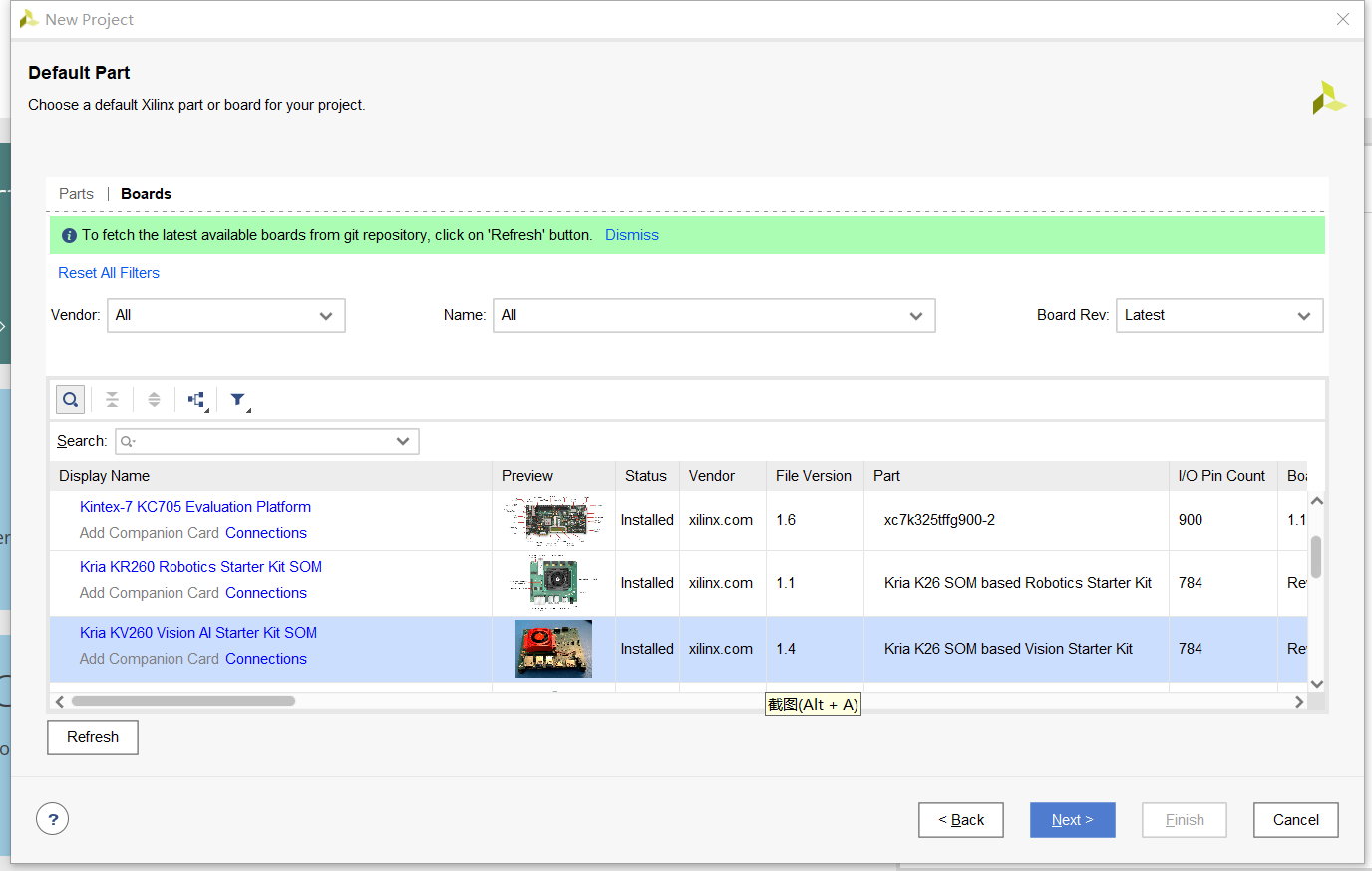

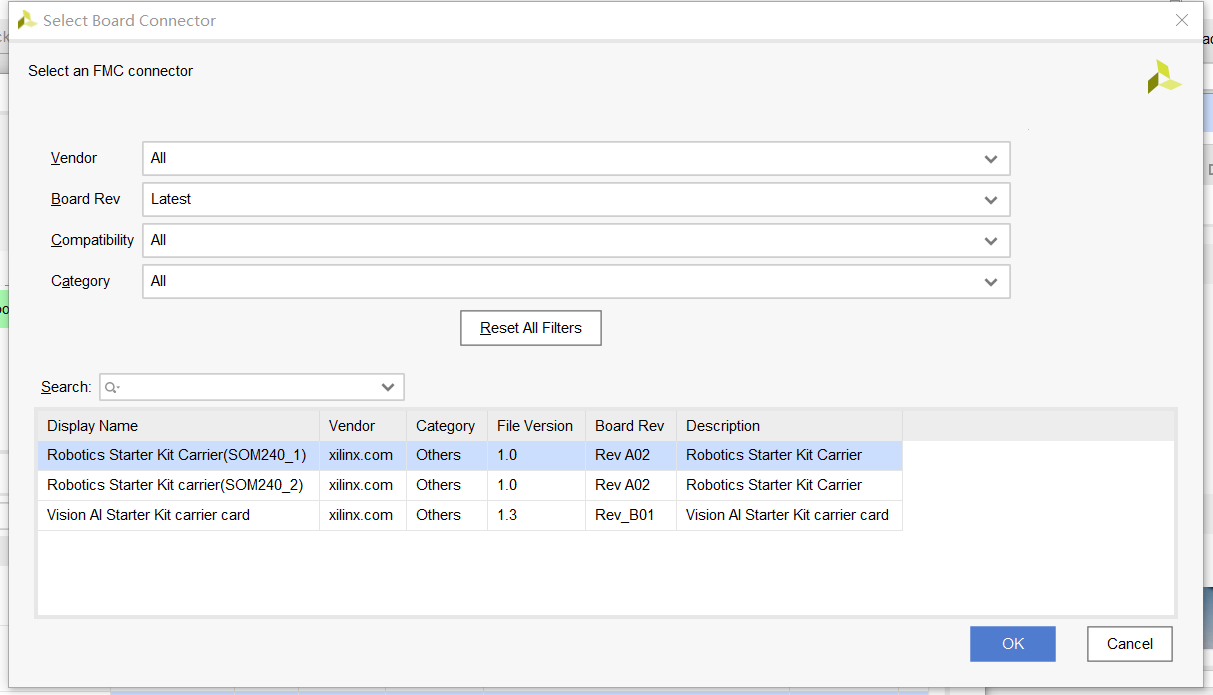

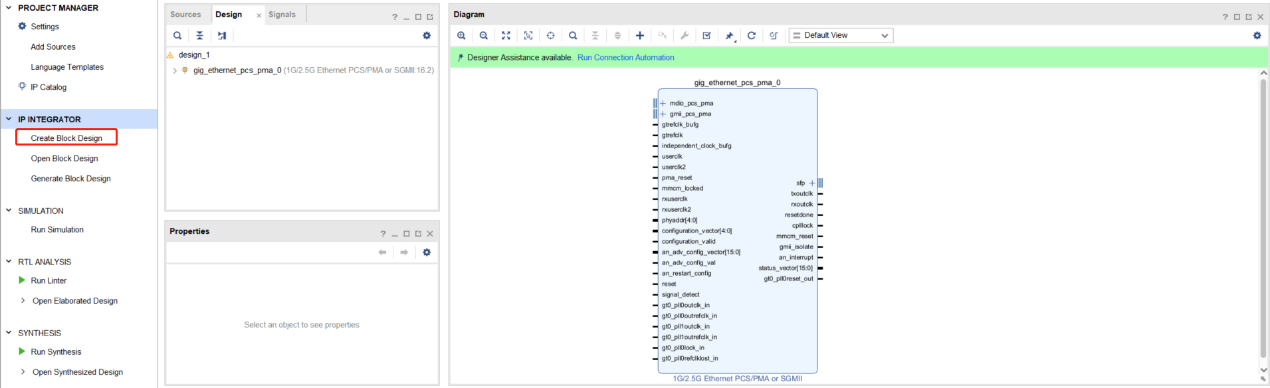

在vivado平台中找到kv260开发板的支持包后,新建项目,并连接。

二.如何在Vivado上修改硬件电路部分

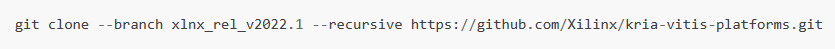

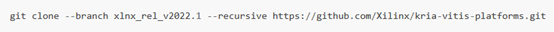

可以选择是否参考现有的硬件设计,首先将官方的仓库克隆一份。

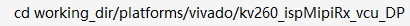

首先到我们使用的平台程序

在vivado中打开项目,点击设计IP模块,可以新建一个集成模块,如果要启用拼接加速器的平台,在平台设置中启用时钟、主AXI、从AXI以及中断就可以使用了,验证之后,运行合成。

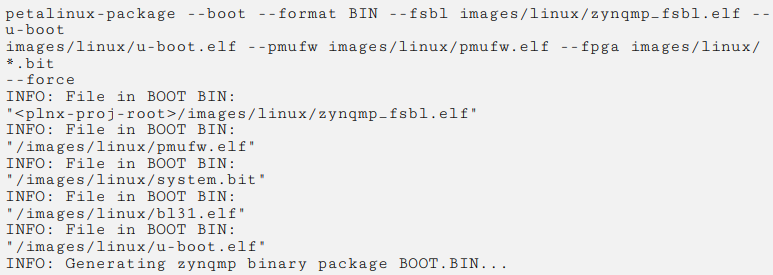

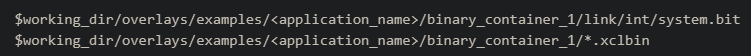

再生成XSA文件,生成硬件信息后,就可以在vitis中使用,并且还要编译叠加层,调用makefile构建.bin和.xcbin文件,最后使用vivado design suite导出硬件描述文件。

三.从petalinux中创建linux启动镜像

打开我们已经创建的petalinux工程目录,将已经生成的dsa文件导入,然后运行petalinux-build,构建系统镜像。

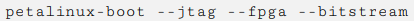

将镜像通过jtag下载到开发板中。

基于UG1393将叠加(加速器功能)集成到 Vitis 可扩展平台中

参考:

1.加载工作目录:

cd$working_dir/

2.运行以下命令:

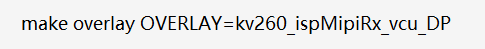

make overlay OVERLAY=<application_name>

Makefile 调用较低级别的 Makefile 来运行 Vitis。如果平台尚不可用,它也会构建该平台。用以实现对于kv260_ispMipiRx_vcu_DP Aibox-reidkv260_vcuDecode_vmixDP,NLP_ispmiprix_dp的支持,针对NLP-智能视觉和缺陷检测功能进行功能加速。

基于UG1393使用Vtis软件平台加速数据中心应用的一些方法:

补充说明:此内容侧重于数据中心应用和基于PCe®的加速卡,但此处确立的概念一般同样适用于嵌入式应用。

在第一阶段,开发者制定出有关应用架构的关键决策,包括决定应映射到器件内核的软件函数、所需的并行度及其交付方式。

在第二阶段,开发者实现内核。这主要涉及构建源代码并应用所需的编译器编译指示来创建所需的内核架构并满足性能目标。

应用架构

C/C++加速器开发

1.设定性能基线并确立目标

2.按加载计算-存储模式

3.对代码进行分区

4.识别要加速的函数

5.将计算块划分为小函数

6.识别FPGA器件并行化需求

7.识别要最优化的循环

8.识别软件应用并行化需求

9.改善循环时延

10.优化架构细节

11.改善循环吞吐量

补充说明:使用阵列所需代码更改更少,在分解过程中,这通常是取得进展的最快方法。但是,使用h1s::stream对象可能会导致设计使用的存储器资源减少并缩短时延。它还有助于开发者了解数据如何在内核中移动,在最优化吞吐量时这始终是需要掌握的重要信息。

如果通过减少循环次数来改善循环时延仍不足够,请尝试缩短启动时间间隔()的方法。循环III是两次循环迭代开始之间的时钟周期计数。Vitis HLS编译器将始终尝试对循环进行流水打拍、最大程度降低III,并尽早开始循环迭代,理想情况是每个时钟周期(III=1)启动新的迭代。有两个主要因素会导致III受限:I/o争用循环进位依赖关系HLSSchedule Viewer会自动高亮限制I的循环依赖关系。在改善循环I时,它是一个非常有用的可视化工具。

|  /9

/9