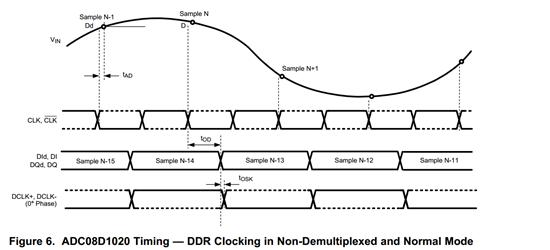

ADC08D1020是一款8位模拟/数字转换器(ADC),通常用于将模拟信号转换为数字信号。在DDR Clocking in Non-Demultiplexed and Normal Mode模式下,DCLK的相位为0°,这意味着DI(数据输入)和DQ(数据输出)在DCLK的边沿发生变化。

在这种模式下,您可以直接利用DCLK的上升沿和下降沿来读取数据。以下是读取数据的步骤:

1. 在DCLK的上升沿,将模拟信号输入到ADC08D1020的模拟输入端。

2. 在DCLK的下降沿,从DI端读取数据。此时,DI端的数据将保持稳定,直到下一个DCLK的上升沿。

3. 在下一个DCLK的上升沿,将新的模拟信号输入到ADC08D1020的模拟输入端。

4. 在下一个DCLK的下降沿,从DI端读取新的数据。

通过这种方式,您可以在DCLK的上升沿和下降沿读取数据。但是,请注意,这种模式下的数据传输速率取决于DCLK的频率。如果DCLK的频率较低,数据传输速率也会降低。因此,在设计系统时,请确保DCLK的频率足够高,以满足您的数据传输速率要求。

ADC08D1020是一款8位模拟/数字转换器(ADC),通常用于将模拟信号转换为数字信号。在DDR Clocking in Non-Demultiplexed and Normal Mode模式下,DCLK的相位为0°,这意味着DI(数据输入)和DQ(数据输出)在DCLK的边沿发生变化。

在这种模式下,您可以直接利用DCLK的上升沿和下降沿来读取数据。以下是读取数据的步骤:

1. 在DCLK的上升沿,将模拟信号输入到ADC08D1020的模拟输入端。

2. 在DCLK的下降沿,从DI端读取数据。此时,DI端的数据将保持稳定,直到下一个DCLK的上升沿。

3. 在下一个DCLK的上升沿,将新的模拟信号输入到ADC08D1020的模拟输入端。

4. 在下一个DCLK的下降沿,从DI端读取新的数据。

通过这种方式,您可以在DCLK的上升沿和下降沿读取数据。但是,请注意,这种模式下的数据传输速率取决于DCLK的频率。如果DCLK的频率较低,数据传输速率也会降低。因此,在设计系统时,请确保DCLK的频率足够高,以满足您的数据传输速率要求。

举报

举报

举报

举报

举报

举报