ADC12DJ3200是一款高速模数转换器(ADC),支持JESD204B接口。JESD204B是一种高速串行接口标准,用于连接ADC和FPGA/ASIC等数字设备。lane rate是JESD204B接口的一个重要参数,表示每个lane的数据传输速率。

要计算lane rate,我们需要考虑以下几个因素:

1. DAC时钟频率(DAC CLK):这是数字模拟转换器(DAC)的时钟频率,用于驱动ADC的采样。

2. 采样率(Sample Rate):这是ADC采样模拟信号的速率。

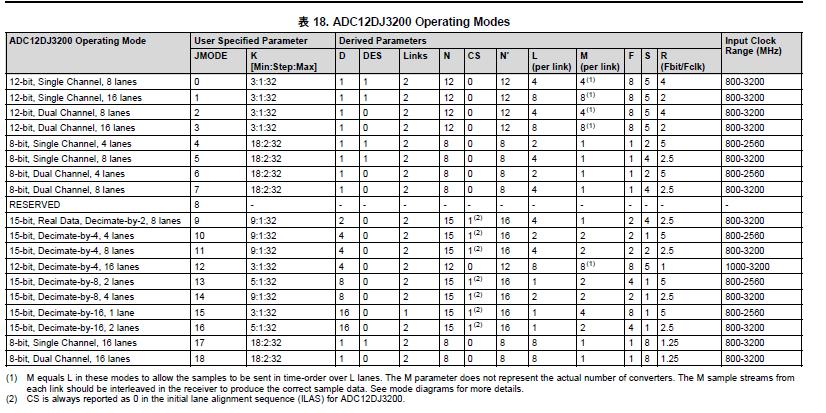

3. JESD204B模式(JMODE):这是JESD204B接口的工作模式,影响数据传输的效率。

根据您提供的信息,DAC CLK为2GHz,采样率为4GHz,采用JMODE0。我们可以根据这些信息计算lane rate。

首先,我们需要了解JMODE0的工作方式。在JMODE0下,每个lane的数据传输速率等于采样率除以8(因为JESD204B接口支持8b/10b编码)。所以,lane rate = 采样率 / 8。

将您提供的采样率代入公式,我们得到:

lane rate = 4GHz / 8 = 0.5GHz

所以,在这种情况下,ADC12DJ3200的lane rate为0.5GHz。

需要注意的是,这个计算结果仅供参考,实际应用中可能会受到其他因素的影响,如信号完整性、时钟同步等。建议您在实际应用中与TI的技术支持团队联系,以获取更准确的lane rate计算方法。

ADC12DJ3200是一款高速模数转换器(ADC),支持JESD204B接口。JESD204B是一种高速串行接口标准,用于连接ADC和FPGA/ASIC等数字设备。lane rate是JESD204B接口的一个重要参数,表示每个lane的数据传输速率。

要计算lane rate,我们需要考虑以下几个因素:

1. DAC时钟频率(DAC CLK):这是数字模拟转换器(DAC)的时钟频率,用于驱动ADC的采样。

2. 采样率(Sample Rate):这是ADC采样模拟信号的速率。

3. JESD204B模式(JMODE):这是JESD204B接口的工作模式,影响数据传输的效率。

根据您提供的信息,DAC CLK为2GHz,采样率为4GHz,采用JMODE0。我们可以根据这些信息计算lane rate。

首先,我们需要了解JMODE0的工作方式。在JMODE0下,每个lane的数据传输速率等于采样率除以8(因为JESD204B接口支持8b/10b编码)。所以,lane rate = 采样率 / 8。

将您提供的采样率代入公式,我们得到:

lane rate = 4GHz / 8 = 0.5GHz

所以,在这种情况下,ADC12DJ3200的lane rate为0.5GHz。

需要注意的是,这个计算结果仅供参考,实际应用中可能会受到其他因素的影响,如信号完整性、时钟同步等。建议您在实际应用中与TI的技术支持团队联系,以获取更准确的lane rate计算方法。

举报

举报

举报

举报

举报

举报