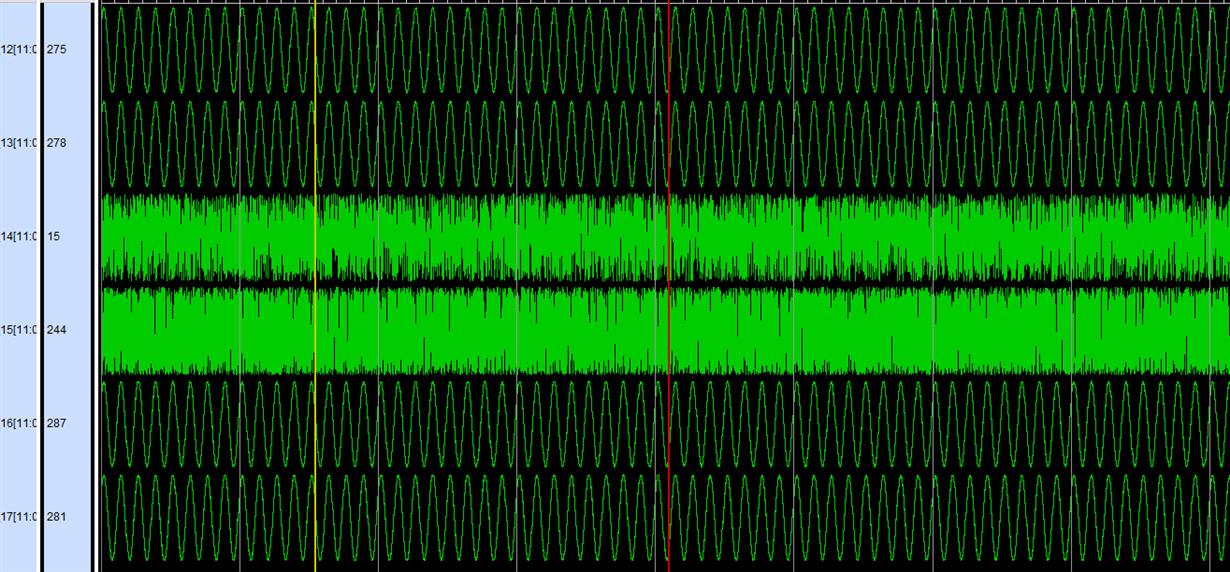

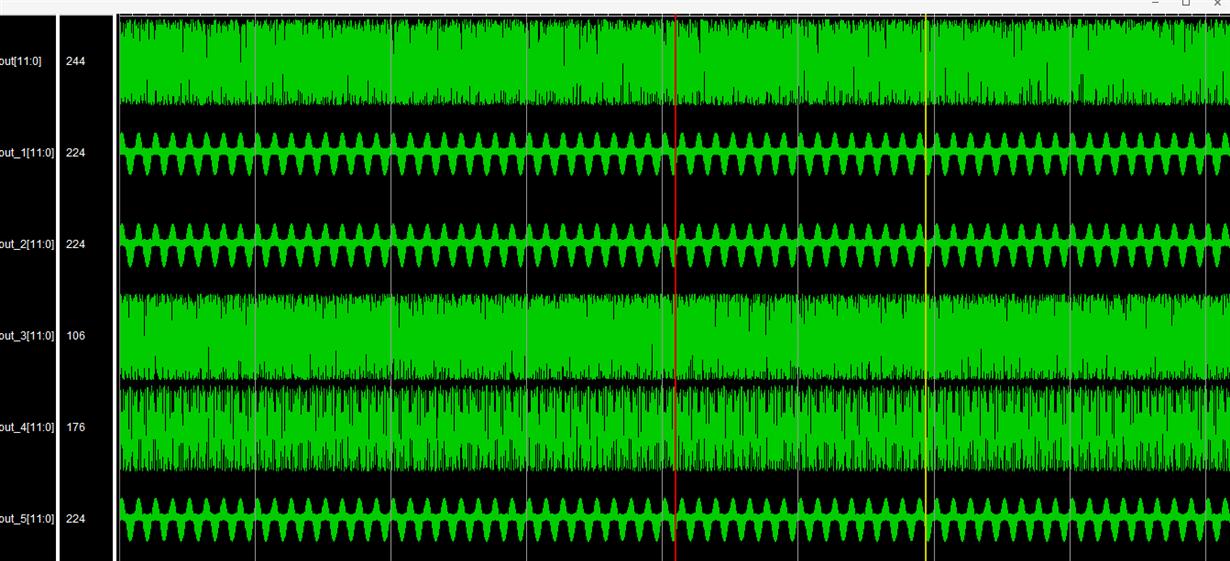

根据您的描述,您在使用ADC12DJ3200时遇到了一个问题,即在正常模式下只有四路数据是正确的,其他数据都不正确。以下是一些建议和可能的原因:

1. 检查硬件连接:请确保所有硬件连接都正确无误,包括电源、时钟、数据和控制信号。任何连接问题都可能导致数据错误。

2. 检查FPGA配置:请检查您的FPGA配置是否正确。确保您已经正确配置了ADC12DJ3200的接口和寄存器。错误的配置可能导致数据错误。

3. 检查采样率和位宽:您提到采样率为5G,位宽为12bit。请确保这些参数与您的ADC12DJ3200和FPGA兼容。不兼容的参数可能导致数据错误。

4. 检查模拟输入信号:您提到模拟端输入数据是1M,-3dBm。请确保这些信号在ADC12DJ3200的输入范围内。超出范围的信号可能导致数据错误。

5. 检查正常模式和斜坡测试模式的差异:您提到在斜坡测试模式下FPGA输出数据是正确的。请检查正常模式和斜坡测试模式之间的差异,看看是否有任何设置或配置不同。这些差异可能导致数据错误。

6. 检查FPGA代码:请检查您的FPGA代码,确保在正常模式下正确处理ADC12DJ3200的数据。错误的代码可能导致数据错误。

7. 检查时钟同步:请确保您的FPGA和ADC12DJ3200之间的时钟同步正确。时钟不同步可能导致数据错误。

8. 检查电源:请检查您的电源是否稳定,电压和电流是否在ADC12DJ3200的规格范围内。不稳定的电源可能导致数据错误。

综上所述,您需要逐步检查硬件连接、FPGA配置、参数设置、模拟输入信号、模式差异、FPGA代码、时钟同步和电源等方面,以找到导致数据错误的原因。希望这些建议能帮助您解决问题。

根据您的描述,您在使用ADC12DJ3200时遇到了一个问题,即在正常模式下只有四路数据是正确的,其他数据都不正确。以下是一些建议和可能的原因:

1. 检查硬件连接:请确保所有硬件连接都正确无误,包括电源、时钟、数据和控制信号。任何连接问题都可能导致数据错误。

2. 检查FPGA配置:请检查您的FPGA配置是否正确。确保您已经正确配置了ADC12DJ3200的接口和寄存器。错误的配置可能导致数据错误。

3. 检查采样率和位宽:您提到采样率为5G,位宽为12bit。请确保这些参数与您的ADC12DJ3200和FPGA兼容。不兼容的参数可能导致数据错误。

4. 检查模拟输入信号:您提到模拟端输入数据是1M,-3dBm。请确保这些信号在ADC12DJ3200的输入范围内。超出范围的信号可能导致数据错误。

5. 检查正常模式和斜坡测试模式的差异:您提到在斜坡测试模式下FPGA输出数据是正确的。请检查正常模式和斜坡测试模式之间的差异,看看是否有任何设置或配置不同。这些差异可能导致数据错误。

6. 检查FPGA代码:请检查您的FPGA代码,确保在正常模式下正确处理ADC12DJ3200的数据。错误的代码可能导致数据错误。

7. 检查时钟同步:请确保您的FPGA和ADC12DJ3200之间的时钟同步正确。时钟不同步可能导致数据错误。

8. 检查电源:请检查您的电源是否稳定,电压和电流是否在ADC12DJ3200的规格范围内。不稳定的电源可能导致数据错误。

综上所述,您需要逐步检查硬件连接、FPGA配置、参数设置、模拟输入信号、模式差异、FPGA代码、时钟同步和电源等方面,以找到导致数据错误的原因。希望这些建议能帮助您解决问题。

举报

举报

举报

举报

举报

举报

举报

举报