您好!针对您在使用DAC37J84时遇到的问题,我为您提供以下解决方案:

1. 检查硬件连接:确保所有硬件连接正确无误,包括电源、时钟、数据接口等。检查是否有松动或损坏的连接。

2. 检查时钟源:确保时钟源稳定且符合DAC37J84的要求。时钟源的不稳定可能导致JESD204B协议建立失败。

3. 调整采样率:尝试在500MSPS以下的采样率中逐步降低采样率,观察协议建立是否成功。这有助于确定问题是否与特定的采样率有关。

4. 检查FPGA配置:确保FPGA配置正确,包括JESD204B协议的配置参数。错误的配置可能导致协议建立失败。

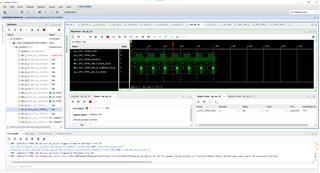

5. 检查同步信号:观察同步信号(sync)的行为,确保其在数据传输阶段稳定。如果同步信号不稳定,可能导致协议建立失败。

6. 软件调试:检查您的软件代码,确保JESD204B协议的实现正确。错误的代码可能导致协议建立失败。

7. 参考DAC37J84的数据手册:仔细阅读DAC37J84的数据手册,了解其在不同采样率下的性能和要求。这有助于您更好地理解问题所在。

8. 寻求技术支持:如果以上方法都无法解决问题,建议您联系DAC37J84的制造商或技术支持团队,寻求专业的帮助。

希望以上建议能帮助您解决问题。如有其他疑问,请随时提问。

您好!针对您在使用DAC37J84时遇到的问题,我为您提供以下解决方案:

1. 检查硬件连接:确保所有硬件连接正确无误,包括电源、时钟、数据接口等。检查是否有松动或损坏的连接。

2. 检查时钟源:确保时钟源稳定且符合DAC37J84的要求。时钟源的不稳定可能导致JESD204B协议建立失败。

3. 调整采样率:尝试在500MSPS以下的采样率中逐步降低采样率,观察协议建立是否成功。这有助于确定问题是否与特定的采样率有关。

4. 检查FPGA配置:确保FPGA配置正确,包括JESD204B协议的配置参数。错误的配置可能导致协议建立失败。

5. 检查同步信号:观察同步信号(sync)的行为,确保其在数据传输阶段稳定。如果同步信号不稳定,可能导致协议建立失败。

6. 软件调试:检查您的软件代码,确保JESD204B协议的实现正确。错误的代码可能导致协议建立失败。

7. 参考DAC37J84的数据手册:仔细阅读DAC37J84的数据手册,了解其在不同采样率下的性能和要求。这有助于您更好地理解问题所在。

8. 寻求技术支持:如果以上方法都无法解决问题,建议您联系DAC37J84的制造商或技术支持团队,寻求专业的帮助。

希望以上建议能帮助您解决问题。如有其他疑问,请随时提问。

举报

举报

举报

举报