你好,根据你描述的情况,我们可以逐步分析可能的原因:

1. 斜坡测试码模式下,JESD204B核输出的rx_sync信号会出现短时间拉低:这可能是由于斜坡测试码模式下,信号的稳定性较差,导致rx_sync信号出现短暂的不稳定。

2. rx_sync信号短时间拉低时,JESD204B不会重新建链:这可能是因为JESD204B核在设计时,对于短暂的rx_sync信号拉低,没有设置重新建链的机制。

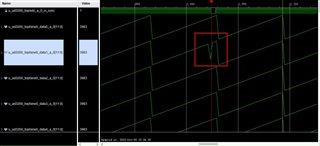

3. 抓取相关信号时,发现rx_sync信号拉低时,rx_frame_error信号会提示字节错误:这说明在rx_sync信号拉低时,数据传输出现了错误,导致rx_frame_error信号触发。

4. 在采样率不变的情况下,将JMODE0改为JMODE1,相当于线速率降低到6Gbps后,不会出现上述情况:这可能是因为在较低的线速率下,信号的稳定性更好,不容易出现rx_sync信号拉低的情况。

综合以上分析,可能的原因有以下几点:

1. GTX物理链路问题:可能是由于GTX物理链路的稳定性较差,导致在高线速率下容易出现rx_sync信号拉低的情况。可以尝试检查GTX物理链路的连接和配置,确保其稳定性。

2. JESD204B核配置问题:可能是由于JESD204B核的配置不当,导致在高线速率下容易出现rx_sync信号拉低的情况。可以尝试检查JESD204B核的配置,确保其正确性。

3. 斜坡测试码模式下信号稳定性问题:可能是由于斜坡测试码模式下信号稳定性较差,导致rx_sync信号出现短暂的不稳定。可以尝试优化斜坡测试码模式下的信号稳定性,或者在测试时避免使用斜坡测试码模式。

4. ADC12DJ3200芯片问题:可能是由于ADC12DJ3200芯片本身的问题,导致在高线速率下容易出现rx_sync信号拉低的情况。可以尝试更换其他ADC12DJ3200芯片进行测试,看是否还会出现类似的问题。

希望以上分析能帮助你找到问题的原因,如果还有其他问题,请随时提问。

你好,根据你描述的情况,我们可以逐步分析可能的原因:

1. 斜坡测试码模式下,JESD204B核输出的rx_sync信号会出现短时间拉低:这可能是由于斜坡测试码模式下,信号的稳定性较差,导致rx_sync信号出现短暂的不稳定。

2. rx_sync信号短时间拉低时,JESD204B不会重新建链:这可能是因为JESD204B核在设计时,对于短暂的rx_sync信号拉低,没有设置重新建链的机制。

3. 抓取相关信号时,发现rx_sync信号拉低时,rx_frame_error信号会提示字节错误:这说明在rx_sync信号拉低时,数据传输出现了错误,导致rx_frame_error信号触发。

4. 在采样率不变的情况下,将JMODE0改为JMODE1,相当于线速率降低到6Gbps后,不会出现上述情况:这可能是因为在较低的线速率下,信号的稳定性更好,不容易出现rx_sync信号拉低的情况。

综合以上分析,可能的原因有以下几点:

1. GTX物理链路问题:可能是由于GTX物理链路的稳定性较差,导致在高线速率下容易出现rx_sync信号拉低的情况。可以尝试检查GTX物理链路的连接和配置,确保其稳定性。

2. JESD204B核配置问题:可能是由于JESD204B核的配置不当,导致在高线速率下容易出现rx_sync信号拉低的情况。可以尝试检查JESD204B核的配置,确保其正确性。

3. 斜坡测试码模式下信号稳定性问题:可能是由于斜坡测试码模式下信号稳定性较差,导致rx_sync信号出现短暂的不稳定。可以尝试优化斜坡测试码模式下的信号稳定性,或者在测试时避免使用斜坡测试码模式。

4. ADC12DJ3200芯片问题:可能是由于ADC12DJ3200芯片本身的问题,导致在高线速率下容易出现rx_sync信号拉低的情况。可以尝试更换其他ADC12DJ3200芯片进行测试,看是否还会出现类似的问题。

希望以上分析能帮助你找到问题的原因,如果还有其他问题,请随时提问。

举报

举报

举报

举报