根据您的描述,我理解您在使用TLV5610 DAC芯片时遇到了一些问题。首先,我们来分析为什么在初始化时将LOAD引脚和片选FS引脚拉低会导致DAC芯片没有输出。

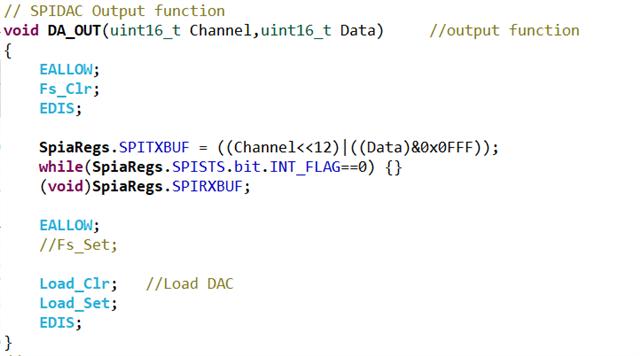

1. 当您在初始化时将LOAD引脚和片选FS引脚拉低,可能会导致DAC芯片处于非工作状态。LOAD引脚通常用于加载DAC寄存器的值,而FS引脚用于片选。如果这两个引脚在初始化时就被拉低,可能会导致DAC芯片无法正确接收数据和工作。

2. 为了解决这个问题,您需要确保在初始化时正确配置LOAD引脚和FS引脚。通常,LOAD引脚应该在数据写入后被拉高,以使DAC寄存器的值更新。FS引脚应该在数据传输过程中保持低电平,以选中DAC芯片。

接下来,我们来讨论如何在使用DMA和FIFO模式的SPI时配置FS和LOAD引脚。

1. 在使用DMA和FIFO模式的SPI时,您需要确保FS和LOAD引脚的控制与DMA传输相匹配。这意味着您需要在DMA传输开始前将FS引脚拉低,以选中DAC芯片。在DMA传输过程中,FS引脚应保持低电平。在DMA传输完成后,您可以将FS引脚拉高,以取消选中DAC芯片。

2. 对于LOAD引脚,您可以在每次DMA传输完成后将其拉高,以更新DAC寄存器的值。这样可以确保DAC芯片在每次传输后都能接收到新的数据。

3. 由于您使用的是DMA和FIFO模式,您需要确保在DMA传输过程中不会占用过多的CPU资源。您可以通过优化代码和使用中断来实现这一点。例如,您可以在DMA传输完成后使用中断来更新LOAD引脚的状态,而不是在主循环中进行。

总之,在使用DMA和FIFO模式的SPI时,您需要确保FS和LOAD引脚的控制与DMA传输相匹配,并优化代码以减少CPU资源占用。希望这些建议能帮助您解决问题。

根据您的描述,我理解您在使用TLV5610 DAC芯片时遇到了一些问题。首先,我们来分析为什么在初始化时将LOAD引脚和片选FS引脚拉低会导致DAC芯片没有输出。

1. 当您在初始化时将LOAD引脚和片选FS引脚拉低,可能会导致DAC芯片处于非工作状态。LOAD引脚通常用于加载DAC寄存器的值,而FS引脚用于片选。如果这两个引脚在初始化时就被拉低,可能会导致DAC芯片无法正确接收数据和工作。

2. 为了解决这个问题,您需要确保在初始化时正确配置LOAD引脚和FS引脚。通常,LOAD引脚应该在数据写入后被拉高,以使DAC寄存器的值更新。FS引脚应该在数据传输过程中保持低电平,以选中DAC芯片。

接下来,我们来讨论如何在使用DMA和FIFO模式的SPI时配置FS和LOAD引脚。

1. 在使用DMA和FIFO模式的SPI时,您需要确保FS和LOAD引脚的控制与DMA传输相匹配。这意味着您需要在DMA传输开始前将FS引脚拉低,以选中DAC芯片。在DMA传输过程中,FS引脚应保持低电平。在DMA传输完成后,您可以将FS引脚拉高,以取消选中DAC芯片。

2. 对于LOAD引脚,您可以在每次DMA传输完成后将其拉高,以更新DAC寄存器的值。这样可以确保DAC芯片在每次传输后都能接收到新的数据。

3. 由于您使用的是DMA和FIFO模式,您需要确保在DMA传输过程中不会占用过多的CPU资源。您可以通过优化代码和使用中断来实现这一点。例如,您可以在DMA传输完成后使用中断来更新LOAD引脚的状态,而不是在主循环中进行。

总之,在使用DMA和FIFO模式的SPI时,您需要确保FS和LOAD引脚的控制与DMA传输相匹配,并优化代码以减少CPU资源占用。希望这些建议能帮助您解决问题。

举报

举报

举报

举报

举报

举报