在您描述的情况下,EOC(End of Conversion)信号在ADC转换启动后立即从高电平变为低电平,且没有观察到预期的延迟时间(Teoc)。这种情况可能与以下几个因素有关:

1. **ADC时钟频率**:您提到ADC的时钟频率为28KHz。ADC的转换时间(Teoc)通常与时钟频率有关。较低的时钟频率可能导致较长的转换时间,但这通常意味着EOC信号在转换完成后才会改变状态,而不是立即改变。

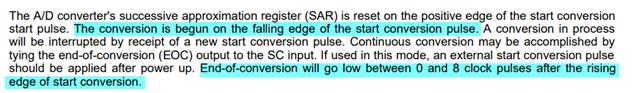

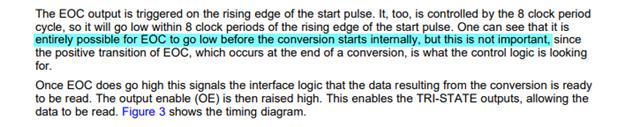

2. **ADC启动和EOC逻辑**:在某些ADC设计中,EOC信号可能在ADC启动时立即改变状态,以指示转换已经开始。这可能与ADC的具体实现有关,而不是与时钟频率直接相关。

3. **硬件连接**:您提到START和ALE(Address Latch Enable)信号连接到同一个管脚。如果这两个信号在逻辑上没有正确隔离或同步,可能会导致意外的信号行为。

4. **STC89C52控制逻辑**:STC89C52的编程和控制逻辑可能影响ADC的行为。如果程序中没有正确处理ADC的启动和EOC信号,可能会导致观察到的现象。

5. **手册描述的延迟时间**:手册中描述的延迟时间可能是指在理想条件下的典型值,实际应用中可能会因硬件设计、电路板布局、信号完整性等因素而有所不同。

为了解决这个问题,您可以尝试以下步骤:

- **检查硬件连接**:确保START和ALE信号没有短路或错误的连接。

- **检查控制逻辑**:在STC89C52中检查和调试控制ADC的代码,确保正确处理ADC的启动和EOC信号。

- **测量时序**:使用示波器测量START信号和EOC信号的时序,以确认信号的实际行为。

- **参考数据手册**:仔细阅读ADC的数据手册,查看是否有关于EOC行为的特定说明或条件。

- **调整时钟频率**:如果可能,尝试调整ADC的时钟频率,看看是否影响EOC信号的行为。

如果问题仍然存在,可能需要更详细的硬件和软件调试来确定具体原因。

在您描述的情况下,EOC(End of Conversion)信号在ADC转换启动后立即从高电平变为低电平,且没有观察到预期的延迟时间(Teoc)。这种情况可能与以下几个因素有关:

1. **ADC时钟频率**:您提到ADC的时钟频率为28KHz。ADC的转换时间(Teoc)通常与时钟频率有关。较低的时钟频率可能导致较长的转换时间,但这通常意味着EOC信号在转换完成后才会改变状态,而不是立即改变。

2. **ADC启动和EOC逻辑**:在某些ADC设计中,EOC信号可能在ADC启动时立即改变状态,以指示转换已经开始。这可能与ADC的具体实现有关,而不是与时钟频率直接相关。

3. **硬件连接**:您提到START和ALE(Address Latch Enable)信号连接到同一个管脚。如果这两个信号在逻辑上没有正确隔离或同步,可能会导致意外的信号行为。

4. **STC89C52控制逻辑**:STC89C52的编程和控制逻辑可能影响ADC的行为。如果程序中没有正确处理ADC的启动和EOC信号,可能会导致观察到的现象。

5. **手册描述的延迟时间**:手册中描述的延迟时间可能是指在理想条件下的典型值,实际应用中可能会因硬件设计、电路板布局、信号完整性等因素而有所不同。

为了解决这个问题,您可以尝试以下步骤:

- **检查硬件连接**:确保START和ALE信号没有短路或错误的连接。

- **检查控制逻辑**:在STC89C52中检查和调试控制ADC的代码,确保正确处理ADC的启动和EOC信号。

- **测量时序**:使用示波器测量START信号和EOC信号的时序,以确认信号的实际行为。

- **参考数据手册**:仔细阅读ADC的数据手册,查看是否有关于EOC行为的特定说明或条件。

- **调整时钟频率**:如果可能,尝试调整ADC的时钟频率,看看是否影响EOC信号的行为。

如果问题仍然存在,可能需要更详细的硬件和软件调试来确定具体原因。

举报

举报

举报

举报

举报

举报