您好!关于您的问题,我将逐一解答:

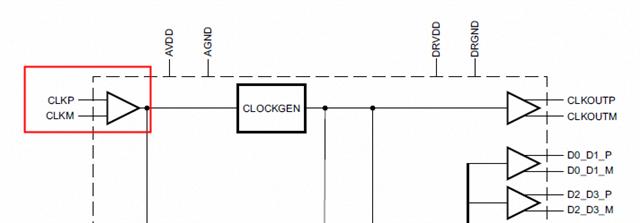

1. 两个高速ADC的CLK时钟如何做到同步无相位差,两个ADC使用同一个时钟发生器是否可以满足同步问题?

要实现两个高速ADC的CLK时钟同步无相位差,您需要确保两个ADC使用同一个时钟源。使用同一个时钟发生器可以满足同步问题,因为这样可以确保两个ADC的采样时钟相位完全一致。您可以使用一个时钟发生器,然后将输出分配给两个ADC的CLK输入端。

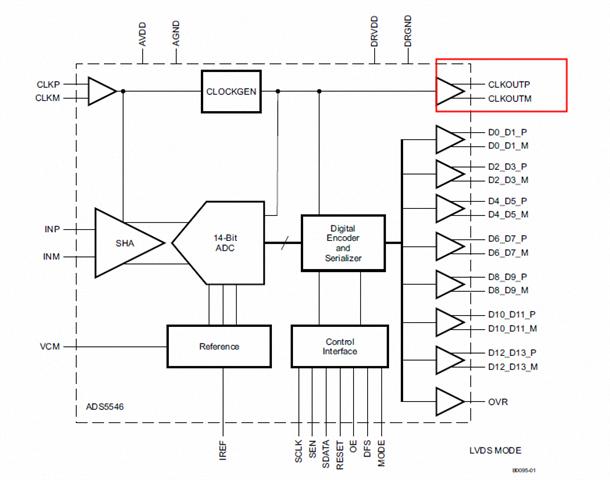

2. 两个高速ADC的CLKOUT是否存在时延,如果存在那相位差是多少?我再规格书中没有看到CLKOUT引脚关于这方面的描述。如果是同步的不存在相位差,那依据是什么?或者CLKOUT是不是依据CLK来的,我只要保证两个ADC的CLK准确同步就可以?

关于CLKOUT引脚的时延问题,您需要查阅ADS5546的数据手册。通常,数据手册会提供关于CLKOUT引脚的详细信息,包括时延和相位差。如果数据手册中没有提供这些信息,您可以尝试联系制造商获取更多详细信息。

如果两个ADC的CLK输入端已经同步,那么CLKOUT引脚的输出也应该同步。这是因为CLKOUT引脚的输出是根据CLK输入端的时钟信号产生的。只要两个ADC的CLK输入端准确同步,CLKOUT引脚的输出也应该同步。

总之,要实现两个高速ADC的CLK时钟同步无相位差,您需要确保它们使用同一个时钟源。关于CLKOUT引脚的时延和相位差问题,您需要查阅数据手册或联系制造商获取更多信息。只要两个ADC的CLK输入端同步,CLKOUT引脚的输出也应该同步。

您好!关于您的问题,我将逐一解答:

1. 两个高速ADC的CLK时钟如何做到同步无相位差,两个ADC使用同一个时钟发生器是否可以满足同步问题?

要实现两个高速ADC的CLK时钟同步无相位差,您需要确保两个ADC使用同一个时钟源。使用同一个时钟发生器可以满足同步问题,因为这样可以确保两个ADC的采样时钟相位完全一致。您可以使用一个时钟发生器,然后将输出分配给两个ADC的CLK输入端。

2. 两个高速ADC的CLKOUT是否存在时延,如果存在那相位差是多少?我再规格书中没有看到CLKOUT引脚关于这方面的描述。如果是同步的不存在相位差,那依据是什么?或者CLKOUT是不是依据CLK来的,我只要保证两个ADC的CLK准确同步就可以?

关于CLKOUT引脚的时延问题,您需要查阅ADS5546的数据手册。通常,数据手册会提供关于CLKOUT引脚的详细信息,包括时延和相位差。如果数据手册中没有提供这些信息,您可以尝试联系制造商获取更多详细信息。

如果两个ADC的CLK输入端已经同步,那么CLKOUT引脚的输出也应该同步。这是因为CLKOUT引脚的输出是根据CLK输入端的时钟信号产生的。只要两个ADC的CLK输入端准确同步,CLKOUT引脚的输出也应该同步。

总之,要实现两个高速ADC的CLK时钟同步无相位差,您需要确保它们使用同一个时钟源。关于CLKOUT引脚的时延和相位差问题,您需要查阅数据手册或联系制造商获取更多信息。只要两个ADC的CLK输入端同步,CLKOUT引脚的输出也应该同步。

举报

举报

举报

举报