根据您提供的信息,您在使用CDCE62005时遇到了一些问题,包括无输出和PLL_LOCK始终为低电平。以下是一些可能的原因和解决方案:

1. 时钟输入问题:请确保输入时钟信号的幅度、相位和频率符合CDCE62005的要求。您提到输入时钟为25MHz,但CDCE62005的输入时钟范围为10MHz至300MHz。请检查输入时钟信号是否在该范围内。

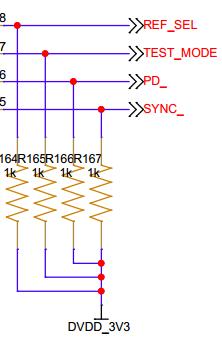

2. 引脚配置问题:请仔细检查外部配置引脚的设置是否正确。您提到引脚均设为高电平,但请确保这些引脚的设置符合CDCE62005的数据手册要求。如果引脚设置不正确,可能会导致PLL_LOCK始终为低电平。

3. 芯片寄存器配置问题:您提到芯片寄存器为默认设置,但请确保这些设置符合CDCE62005的数据手册要求。如果寄存器设置不正确,可能会导致无输出。

4. 电源问题:虽然您提到芯片供电正常,但请确保电源电压和电流符合CDCE62005的要求。如果电源不稳定或不足,可能会导致芯片无法正常工作。

5. 芯片损坏:如果以上问题都排除了,那么可能是芯片本身存在问题。您可以尝试更换一个芯片进行测试。

建议您按照以下步骤进行排查:

1. 检查输入时钟信号是否符合CDCE62005的要求。

2. 仔细检查外部配置引脚的设置是否正确。

3. 检查芯片寄存器的设置是否符合CDCE62005的数据手册要求。

4. 确保电源电压和电流符合CDCE62005的要求。

5. 如果以上问题都排除了,尝试更换一个芯片进行测试。

希望以上信息能帮助您解决问题。如有其他疑问,请随时提问。

根据您提供的信息,您在使用CDCE62005时遇到了一些问题,包括无输出和PLL_LOCK始终为低电平。以下是一些可能的原因和解决方案:

1. 时钟输入问题:请确保输入时钟信号的幅度、相位和频率符合CDCE62005的要求。您提到输入时钟为25MHz,但CDCE62005的输入时钟范围为10MHz至300MHz。请检查输入时钟信号是否在该范围内。

2. 引脚配置问题:请仔细检查外部配置引脚的设置是否正确。您提到引脚均设为高电平,但请确保这些引脚的设置符合CDCE62005的数据手册要求。如果引脚设置不正确,可能会导致PLL_LOCK始终为低电平。

3. 芯片寄存器配置问题:您提到芯片寄存器为默认设置,但请确保这些设置符合CDCE62005的数据手册要求。如果寄存器设置不正确,可能会导致无输出。

4. 电源问题:虽然您提到芯片供电正常,但请确保电源电压和电流符合CDCE62005的要求。如果电源不稳定或不足,可能会导致芯片无法正常工作。

5. 芯片损坏:如果以上问题都排除了,那么可能是芯片本身存在问题。您可以尝试更换一个芯片进行测试。

建议您按照以下步骤进行排查:

1. 检查输入时钟信号是否符合CDCE62005的要求。

2. 仔细检查外部配置引脚的设置是否正确。

3. 检查芯片寄存器的设置是否符合CDCE62005的数据手册要求。

4. 确保电源电压和电流符合CDCE62005的要求。

5. 如果以上问题都排除了,尝试更换一个芯片进行测试。

希望以上信息能帮助您解决问题。如有其他疑问,请随时提问。

举报

举报

举报

举报