要实现多颗LMK04828输出信号相位稳定的目的,使用参考时钟和10Hz同步信号的方案是可行的。以下是一些关键点和步骤,以确保多颗LMK04828的输出时钟相位稳定:

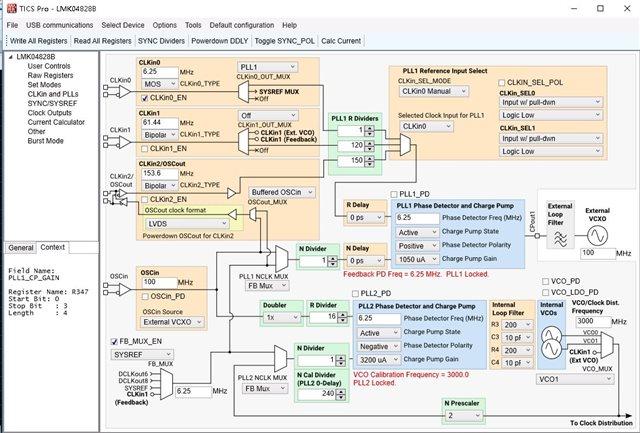

1. **参考时钟同步**:

- 确保所有LMK04828的100MHz时钟输入(CLKIN0)来自同一个Buffer芯片,这样可以保证所有芯片接收到的时钟信号是相同的,从而实现时钟同步。

- 由于100MHz时钟信号频率可调节,确保所有芯片的时钟频率保持一致。

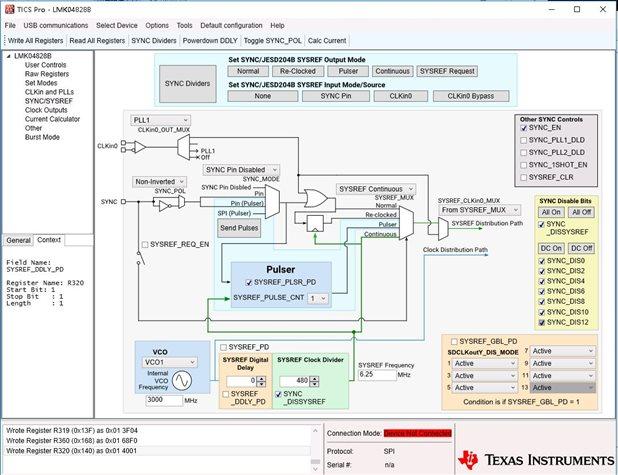

2. **低频同步信号**:

- 所有LMK04828的SYNC输入应接收来自同一个LMK00105扇出的多路10Hz低频同步信号。这样可以确保所有芯片在相同的时间点接收到同步信号,实现同步。

- 10Hz信号直接输入到Sync Pin,确保所有芯片的SYNC输入相位一致。

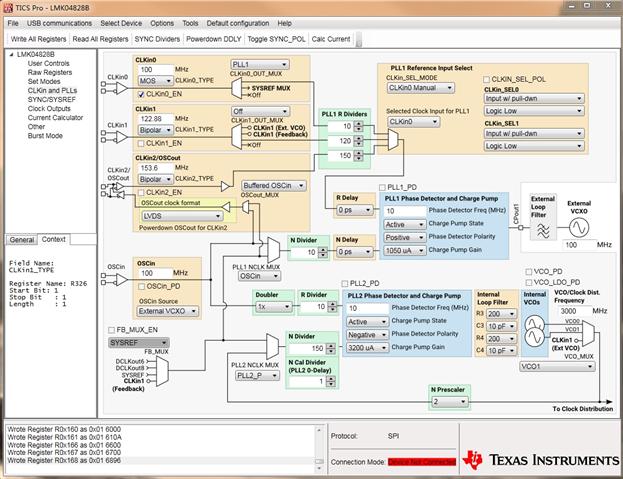

3. **PLL配置**:

- 所有LMK04828的两级PLL配置应保持一致,以确保VCO工作在相同的频率(3000MHz)。

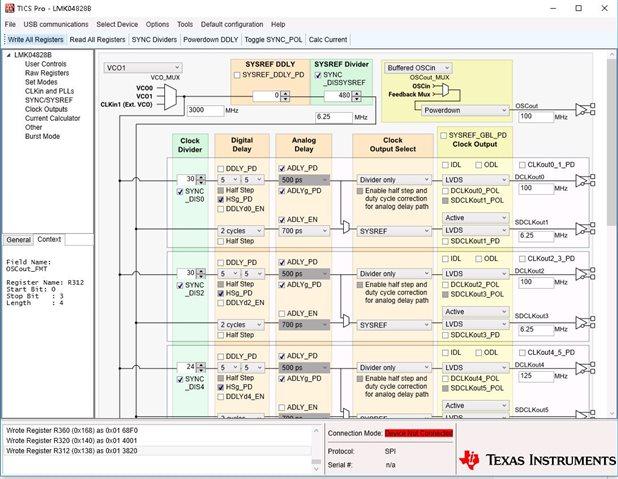

- 输出端多路输出100MHz、125MHz,并配合SYSREF输出6.25MHz信号,确保所有芯片的输出频率和相位关系固定。

4. **SYSREF相位关系**:

- 由于SYSREF输出依赖于10Hz同步信号,确保所有LMK04828的SYSREF输出相位关系固定,需要保证10Hz同步信号的相位一致性。

5. **DCLKout0输出相位关系**:

- DCLKout0的输出相位关系稳定依赖于100MHz时钟输入和10Hz同步信号的相位一致性。由于所有芯片的这两个输入信号都是同步的,DCLKout0的输出相位关系也将是稳定的。

6. **测试和验证**:

- 在实际应用中,需要对多颗LMK04828的输出信号进行测试和验证,确保相位关系符合预期。

- 使用相位分析仪或其他测试设备来测量和验证SYSREF和DCLKout0的相位稳定性。

通过以上步骤,可以确保多颗LMK04828输出的SYSREF相位关系固定,DCLKout0输出相位关系稳定,从而实现后级RFSOC-AD/DA的同步。

要实现多颗LMK04828输出信号相位稳定的目的,使用参考时钟和10Hz同步信号的方案是可行的。以下是一些关键点和步骤,以确保多颗LMK04828的输出时钟相位稳定:

1. **参考时钟同步**:

- 确保所有LMK04828的100MHz时钟输入(CLKIN0)来自同一个Buffer芯片,这样可以保证所有芯片接收到的时钟信号是相同的,从而实现时钟同步。

- 由于100MHz时钟信号频率可调节,确保所有芯片的时钟频率保持一致。

2. **低频同步信号**:

- 所有LMK04828的SYNC输入应接收来自同一个LMK00105扇出的多路10Hz低频同步信号。这样可以确保所有芯片在相同的时间点接收到同步信号,实现同步。

- 10Hz信号直接输入到Sync Pin,确保所有芯片的SYNC输入相位一致。

3. **PLL配置**:

- 所有LMK04828的两级PLL配置应保持一致,以确保VCO工作在相同的频率(3000MHz)。

- 输出端多路输出100MHz、125MHz,并配合SYSREF输出6.25MHz信号,确保所有芯片的输出频率和相位关系固定。

4. **SYSREF相位关系**:

- 由于SYSREF输出依赖于10Hz同步信号,确保所有LMK04828的SYSREF输出相位关系固定,需要保证10Hz同步信号的相位一致性。

5. **DCLKout0输出相位关系**:

- DCLKout0的输出相位关系稳定依赖于100MHz时钟输入和10Hz同步信号的相位一致性。由于所有芯片的这两个输入信号都是同步的,DCLKout0的输出相位关系也将是稳定的。

6. **测试和验证**:

- 在实际应用中,需要对多颗LMK04828的输出信号进行测试和验证,确保相位关系符合预期。

- 使用相位分析仪或其他测试设备来测量和验证SYSREF和DCLKout0的相位稳定性。

通过以上步骤,可以确保多颗LMK04828输出的SYSREF相位关系固定,DCLKout0输出相位关系稳定,从而实现后级RFSOC-AD/DA的同步。

举报

举报

举报

举报