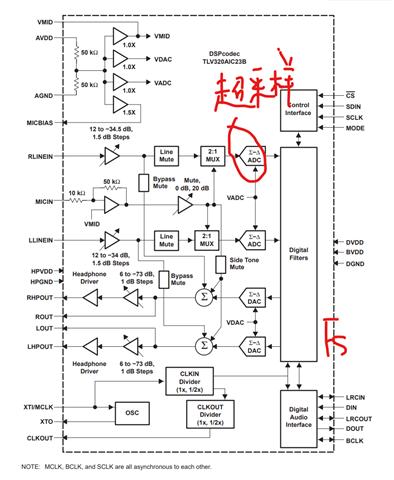

最高采样率到96KHZ,具体见数据表3.3.2 Audio Sampling Rates章节;

TLV320AIC23B内部集成的是Delta-Sigma ADC,主要包括Delta-Sigma 调制器和数字滤波器,Delta-Sigma 调制器以非常高的速率对输入信号进行采样,并转换成1bit位数据流,之后,数字滤波器使用该采样数据,将其转换成高分辨率低速数字代码。注意,这里的数字滤波器不是抗混叠滤波的目的。

任何超过采样频率一半的输入信号都会产生混叠信号,因此,抗混叠滤波器是加在信号输入端以滤除产生混叠信号的频率。

最高采样率到96KHZ,具体见数据表3.3.2 Audio Sampling Rates章节;

TLV320AIC23B内部集成的是Delta-Sigma ADC,主要包括Delta-Sigma 调制器和数字滤波器,Delta-Sigma 调制器以非常高的速率对输入信号进行采样,并转换成1bit位数据流,之后,数字滤波器使用该采样数据,将其转换成高分辨率低速数字代码。注意,这里的数字滤波器不是抗混叠滤波的目的。

任何超过采样频率一半的输入信号都会产生混叠信号,因此,抗混叠滤波器是加在信号输入端以滤除产生混叠信号的频率。

举报

举报

举报

举报

举报

举报

举报

举报