通常,活动状态下的操作将在每个时钟周期中执行,并在每个时钟边缘检查过渡条件。我的问题是,在一个时钟周期内,在执行数据传输操作(如IN_DATA或DR_DATA)之后,像 dma_rdy_thn 或 dma_wm_thn 这样的过渡触发器需要一些周期的延迟才能断言吗?

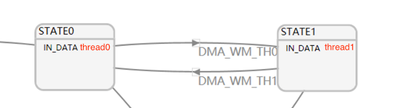

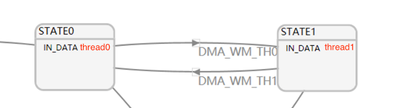

在我的实践中,DMA_WM_THN 触发器似乎有 1 个时钟周期延迟:

图像是我的状态机的一部分,数据总线是 32 位。 当水印设置为 1 个 4 字节字时,状态机运行良好。 在这种情况下,GPIF 可以连续将数据传输到 DMA,而不会丢失数据。

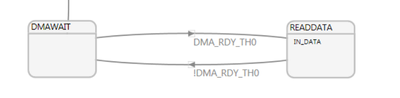

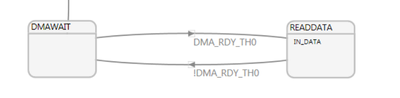

但是,为了解决这个问题,这意味着 Dma_rdy_THN 触发器有 1 个时钟周期的延迟。 也就是说,在执行 IN_DATA 操作后,线程 n 的主动 DMA 缓冲区的可用大小为 1 字的时钟周期中,必须在下一个时钟中断言 DMA_WM_THN。 只有在这种情况下,线程 n 的主动 DMA 缓冲区才会在状态转换/线程切换之前被完全填满。

虽然根据 TRM 文档第 7.11 节中的示例,dma_rdy_thn 触发器似乎没有延迟:

在 READDATA 状态下,如果存在断言 DMA_RDY_TH0 的时钟延迟,则线程 0 的 DMA 缓冲区将被超出。

举报

举报