各位技术支持:

目前在做项目中用到AD9653模数转换器。采样时钟80MHz,模拟输入端为 差分输入,输入信号源由信号发生器RIGOL DG4162生成两路差分信号,串行数据由

FPGA接收并解串,前期码流测试解串正常,

电路图如下:

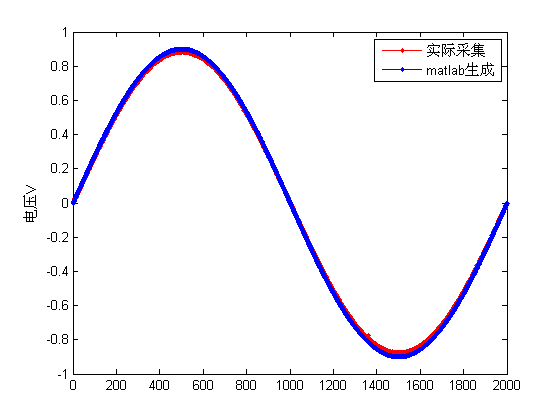

再用实际信号进行采集测试时(通过P1、 P2端子直接接入AD9653输入引脚),将采集到的数据和理想数据(

matlab生成)做对比,通过逐点作差的方法分析采集数据的质量,从而得到采样误差。实验过程中,发现:

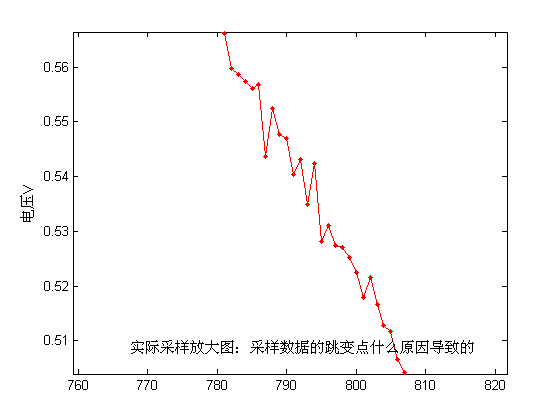

1:AD9653采样数据不稳定,采样波形中含较多噪声,见下图。

2:1.8VPP输入时,最大误差达到0.03v,见下图。

举报

举报