目 录

前 言 3

1 HLS 开发流程说明 5

1.1 HLS 工程导入 5

1.3 综合 8

1.4 IP 核封装 10

1.5 IP 核测试 14

前 言

本文主要介绍 HLS 案例的使用说明,适用开发环境: Windows 7/10 64bit、Xilinx Vivado

2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4。

Xilinx Vivado HLS (High-Level Synthesis,高层次综合) 工具支持将 C 、C++等语言转化

成硬件描述语言,同时支持基于 OpenCL 等框架对 Xilinx 可编程逻辑器件进行开发,可加

速算法开发的进程,缩短产品上市时间。

HLS 基本开发流程如下:

(1) HLS 工程新建/工程导入

(2) 编译与仿真

(3) 综合

(4) IP 核封装

(5) IP 核测试

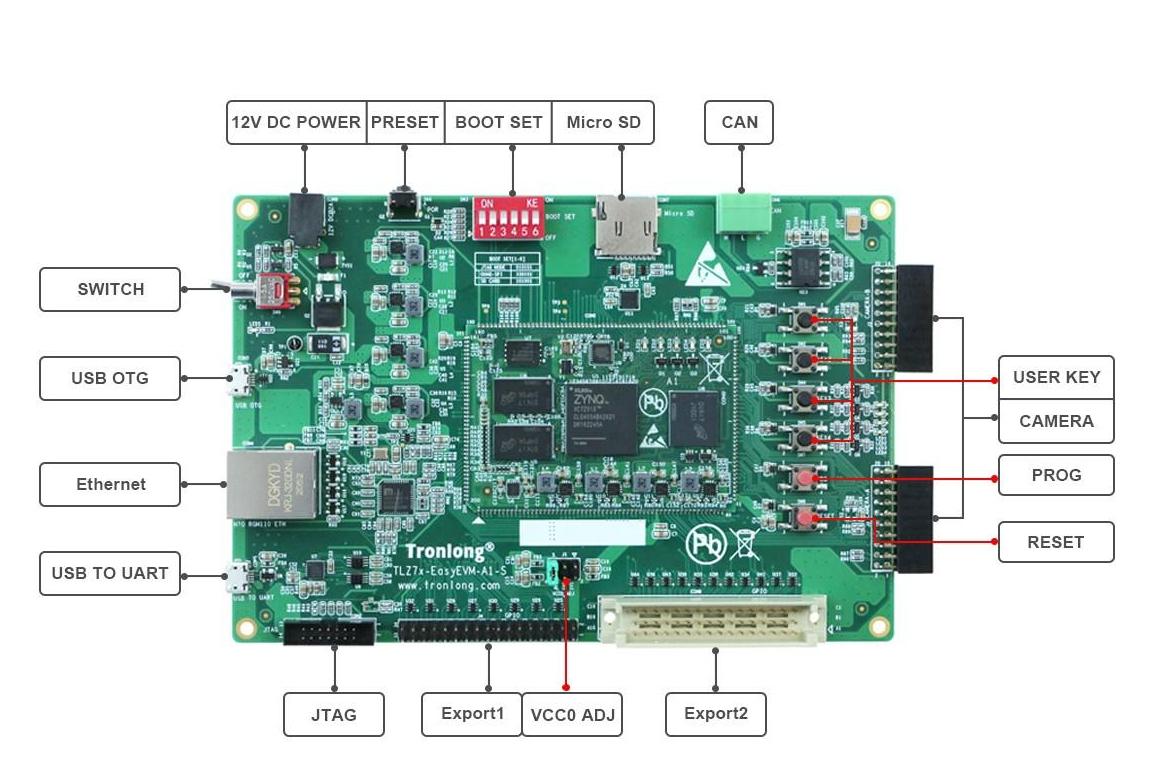

测试板卡是基于创龙科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗处理器设计的异构多核SoC工业级核心板。

HLS 案例位于产品资料“4-软件资料Demo

FPGA-HLS-demos”目录下, 案例目录详细

说明如下表。

表 1

目录 | 目录 | 文件/目录 | 说明 |

hls_ip_demo | bin 或 hw/bin | xxx_xc7z010.bin/xxx_xc7z010.bit | xc7z010 PL 端 IP 核测试可执行文件 |

xxx_xc7z020.bin/xxx_xc7z020.bit | xc7z020 PL 端 IP 核测试可执行文件 |

project 或 hw/project | xxx_xc7z010 | xc7z010 PL 端 IP 核测试 Vivado 工程 |

xxx_xc7z020 | xc7z020 PL 端 IP 核测试 Vivado 工程 |

sw | bin | PS 端 IP 核测试裸机可执行文件 |

project | PS 端 IP 核测试裸机工程 |

vivado_hls | ip_package | xxx.zip | IP 核 |

project | | 仿真方案 |

src | HLS 工程源码 |

test_bench | HLS 工程仿真程序或测试文件 |

vivado_hls.app | HLS 工程文件 |

HLS 详细开发说明可参考产品资料“6-开发参考资料Xilinx 官方参考文档”目录下

的如下文档。

(1) ug871-vivado-high-level-synthesis-tutorial.pdf

(2) ug902-vivado-high-level-synthesis.pdf

1 HLS 开发流程说明

本章节以产品资料“4-软件资料DemoFPGA-HLS-demos”目录下的 led_flash 案例为 例, 演示 HLS 开发流程。此案例的功能是由 PL 端控制评估底板的 LED2 进行闪烁。

在此之前, 请将对应案例目录拷贝至 Windows 非中文路径下。

备注: Windows 路径有长度限制,路径太长将会导致工程打开出错。

在进行本文如下操作前,请先按照调试工具安装文档安装 Xilinx Vivado 开发工具包。

本文默认使用创龙科技的 TL-DLC10 下载器进行操作演示。

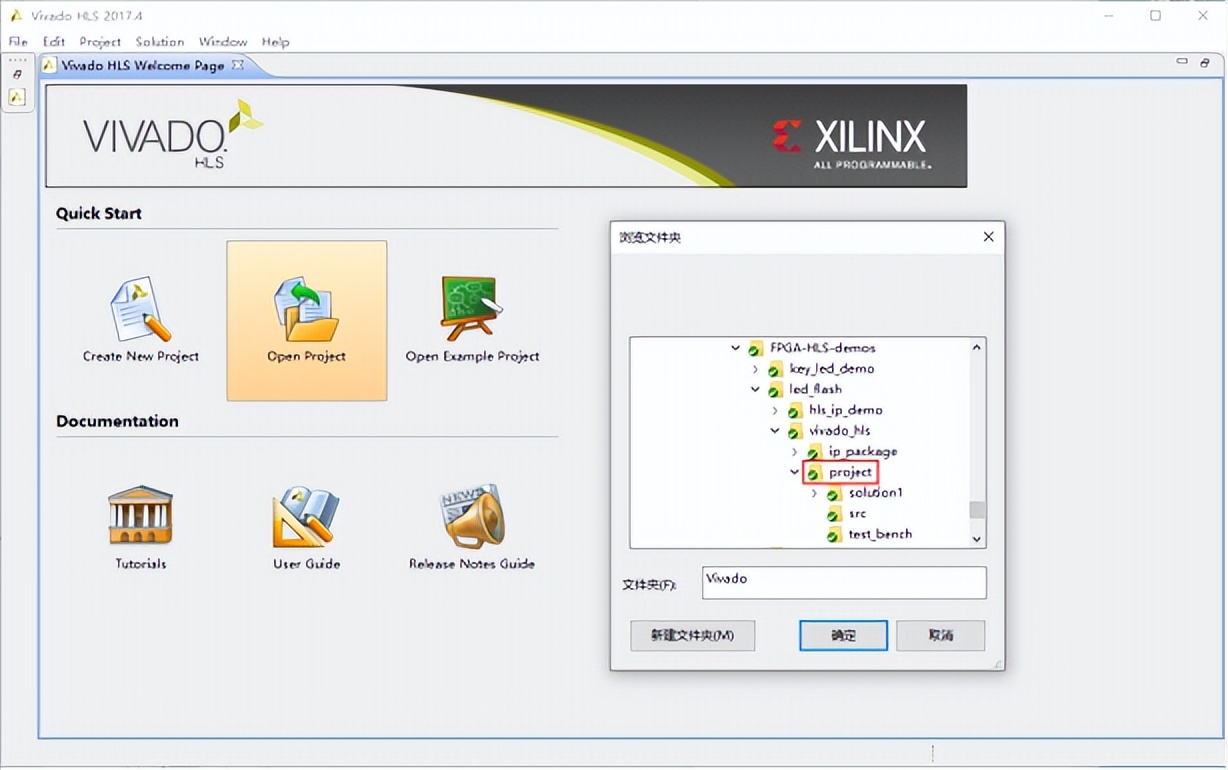

1.1 HLS 工程导入

双击桌面如下图标打开Xilinx Vivado HLS 2017.4,并在弹出的界面中点击“Open Project” 选择案例“vivado_hlsproject”目录,然后点击“确定”导入 HLS 工程。

图 1

图 2

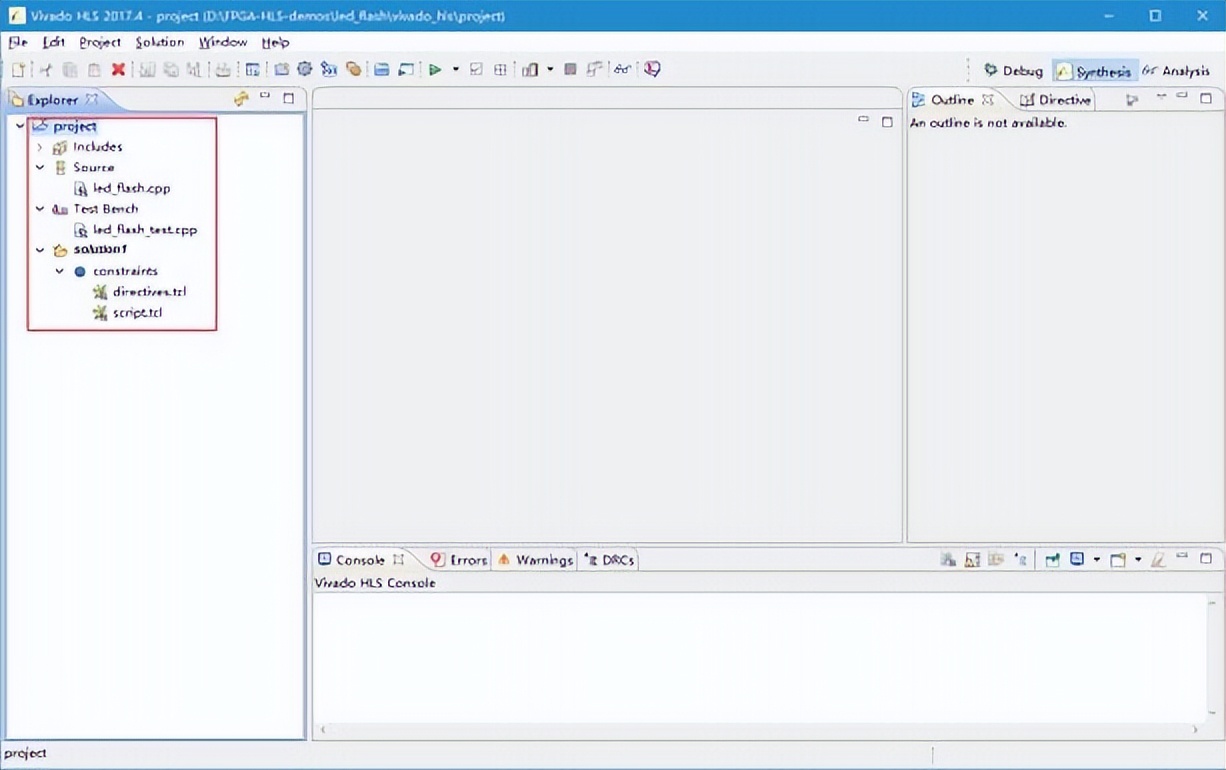

图 3

亦可新建 HLS 工程,并使用C/C++等语言进行程序编写。

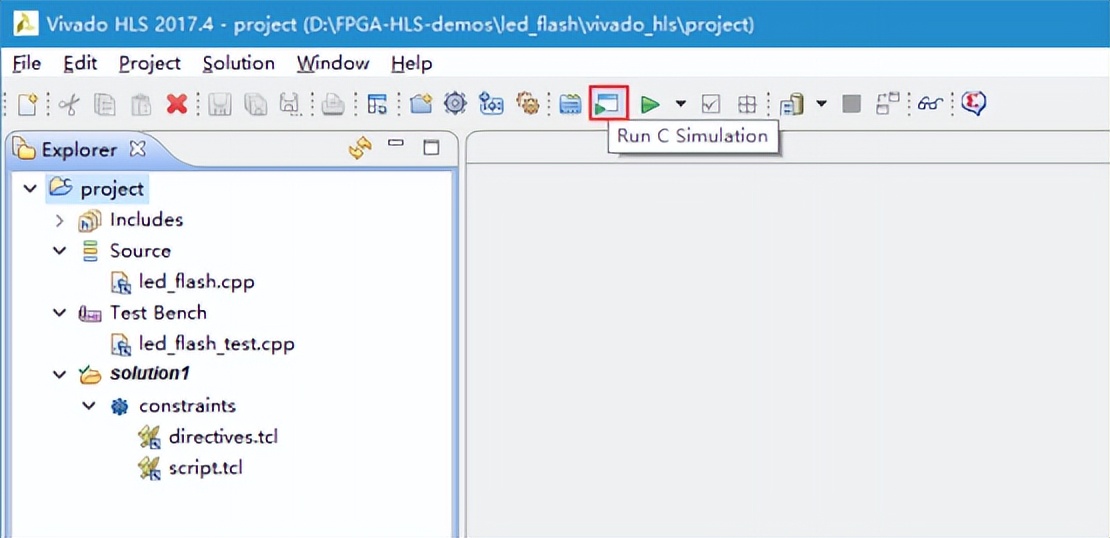

1.2 编译与仿真

仿真程序位于 Test Bench 目录下,用于验证Source 目录下的 HLS 工程源码。

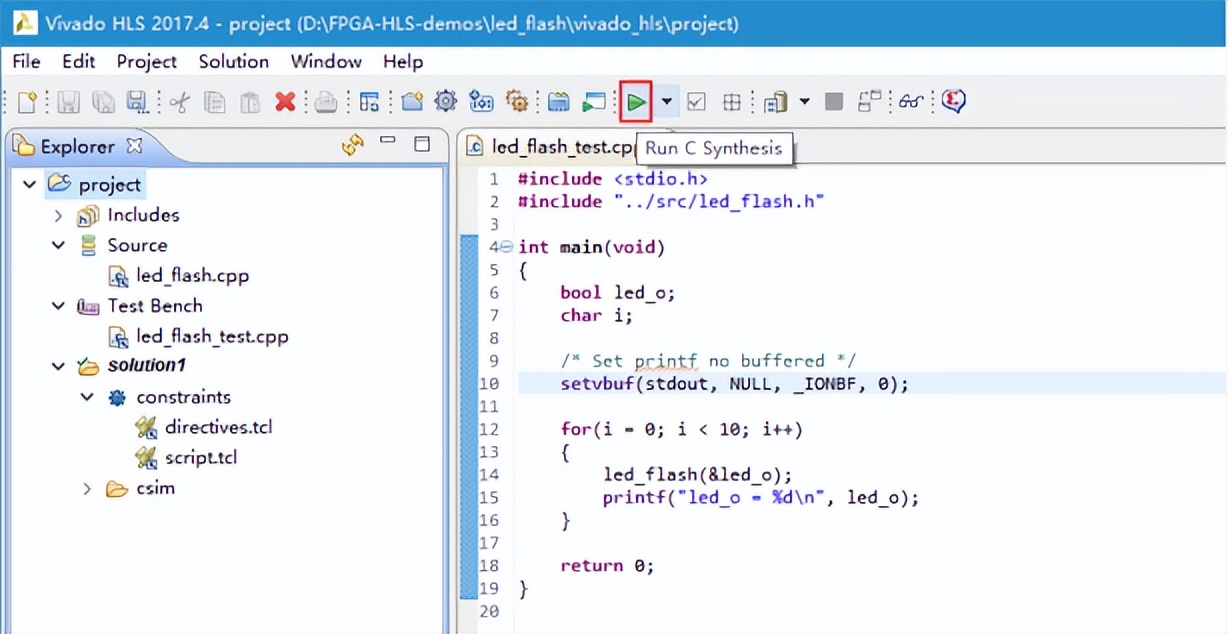

导入 HLS 工程后,点击 (Run C Simulation)进行编译与仿真。

图 4

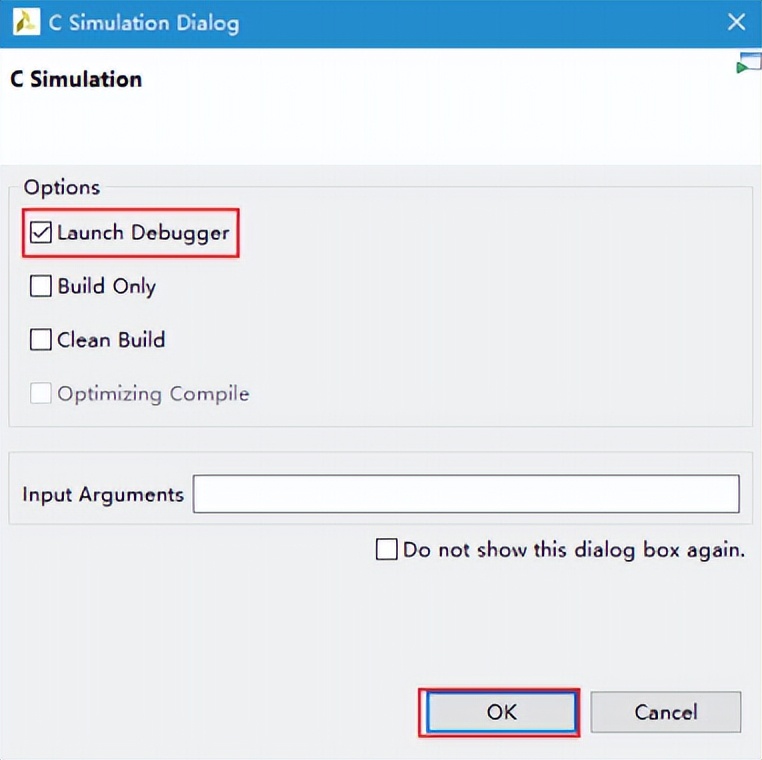

弹出如下界面, 勾选“Launch Debugger” ,并点击 OK。

图 5

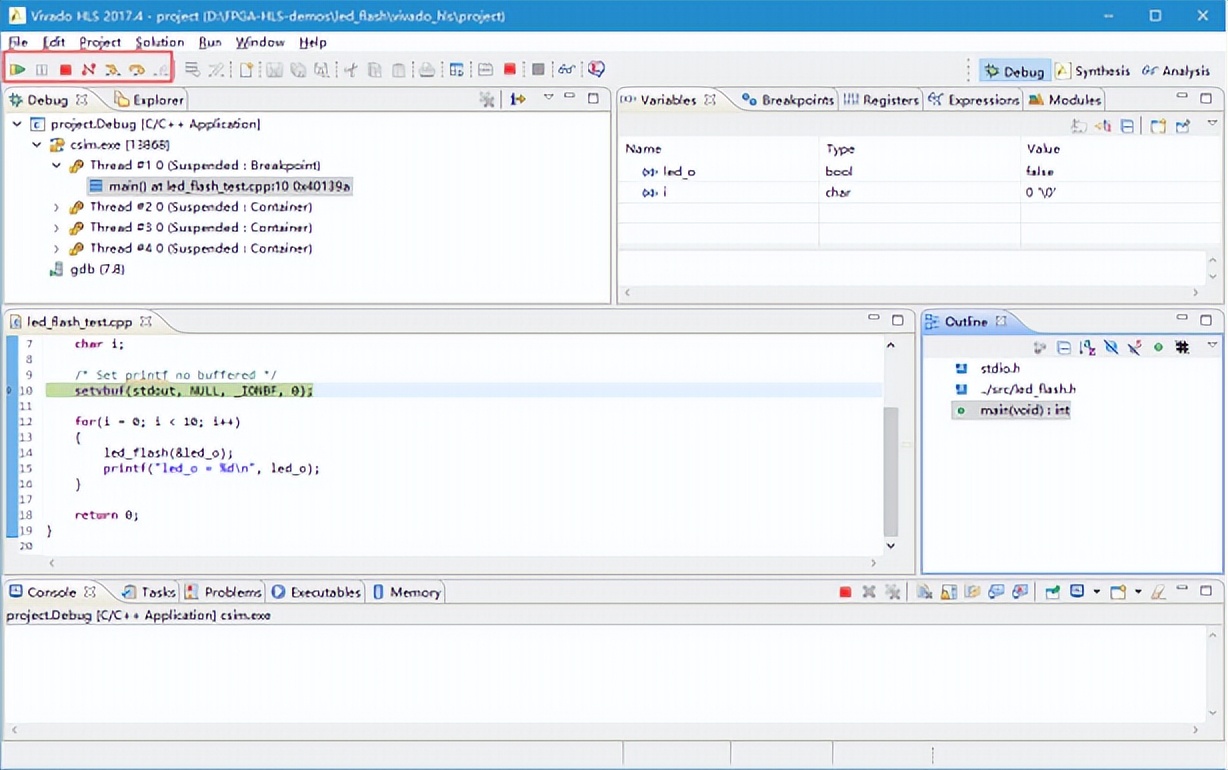

编译完成后,即可全速或单步运行进行仿真。

图 6

1.3 综合

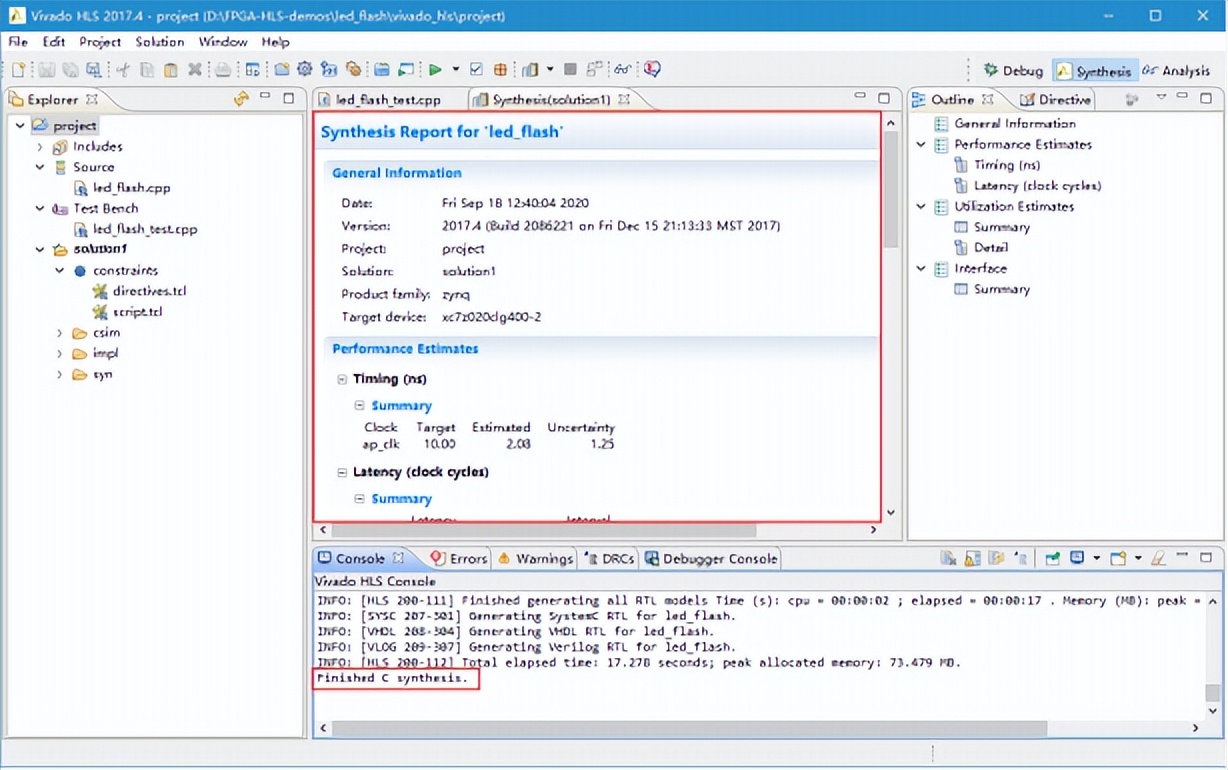

本小节演示将 C/C++等程序综合成为 RTL 设计,并生成综合报告。

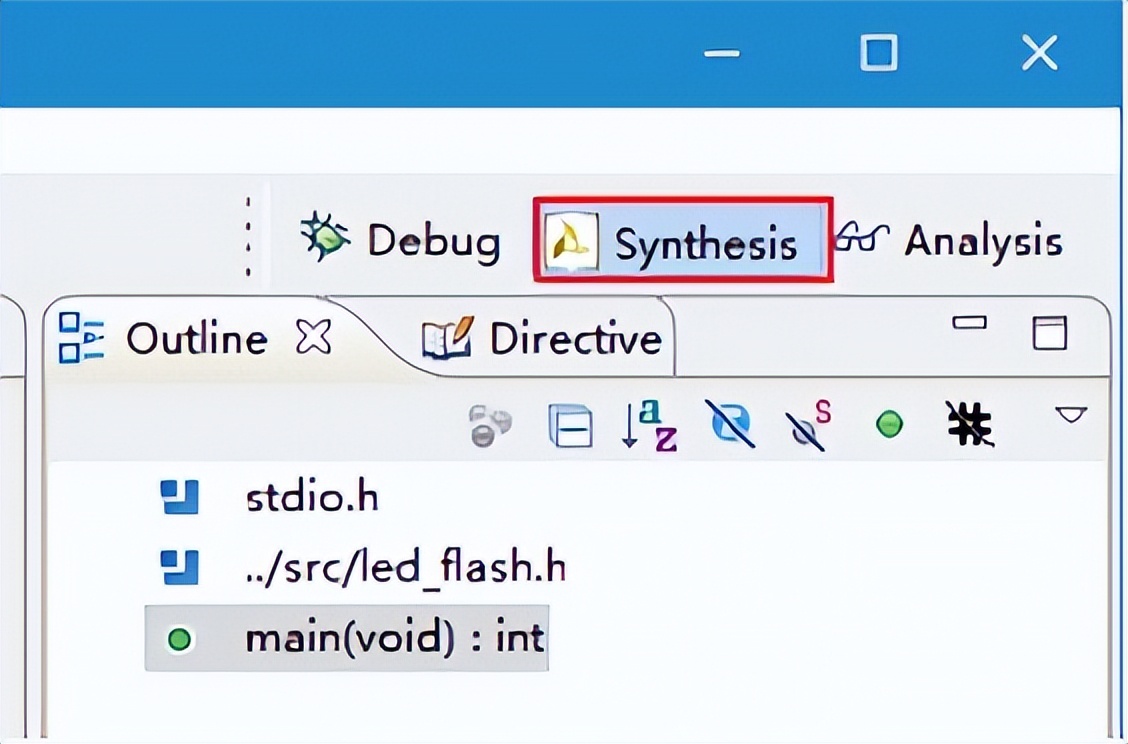

点击界面右上角Synthesis 返回至工程界面,然后点击

进行综合。

图 7

图 8

综合完成后,报表文件将自动打开。

图 9

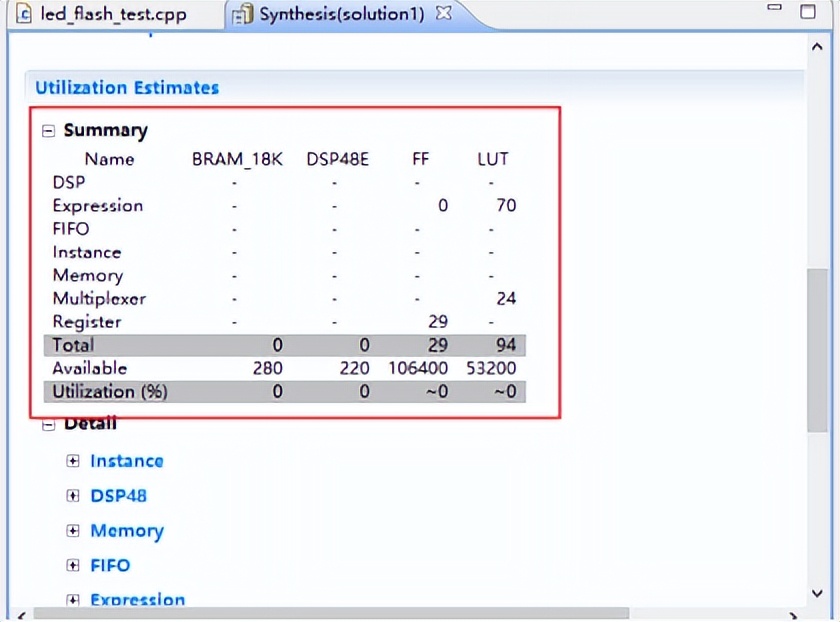

通过报表文件可查看本设计的时延、资源占用等信息。

图 10

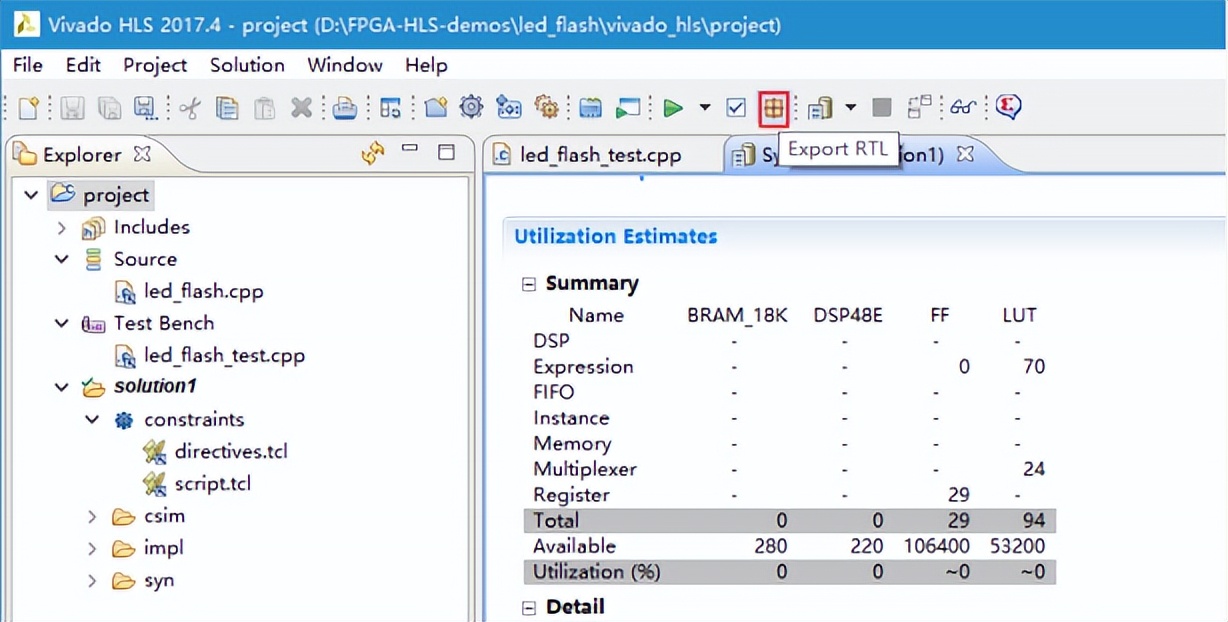

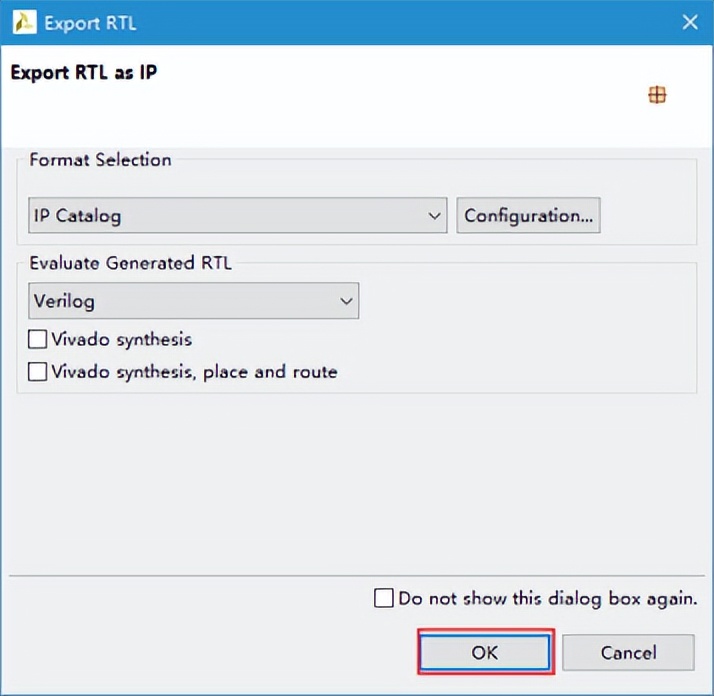

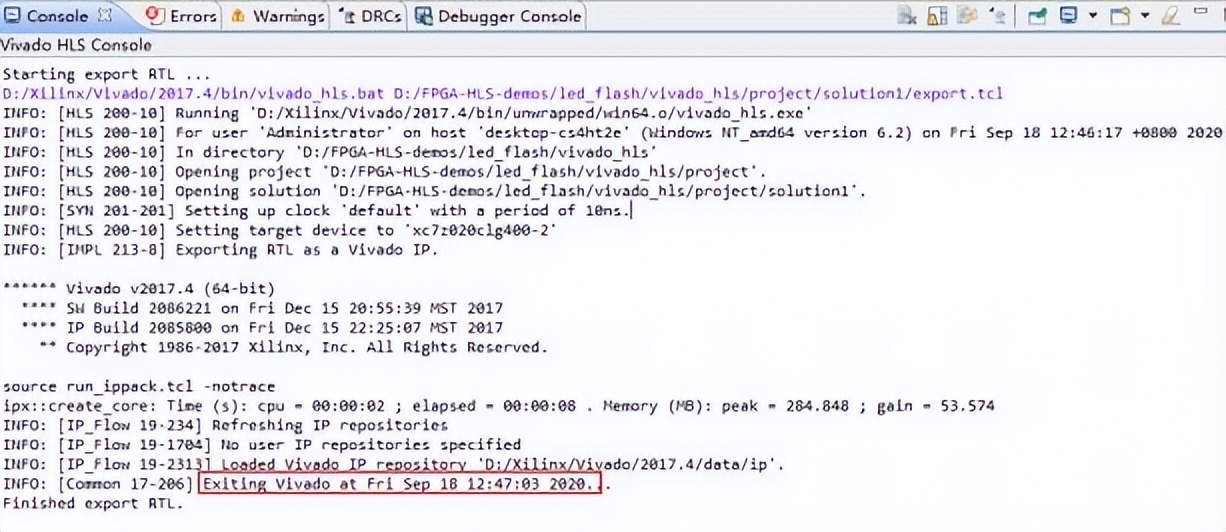

1.4 IP 核封装

综合完成后,点击 生成 IP 核。

图 11

图 12

图 13

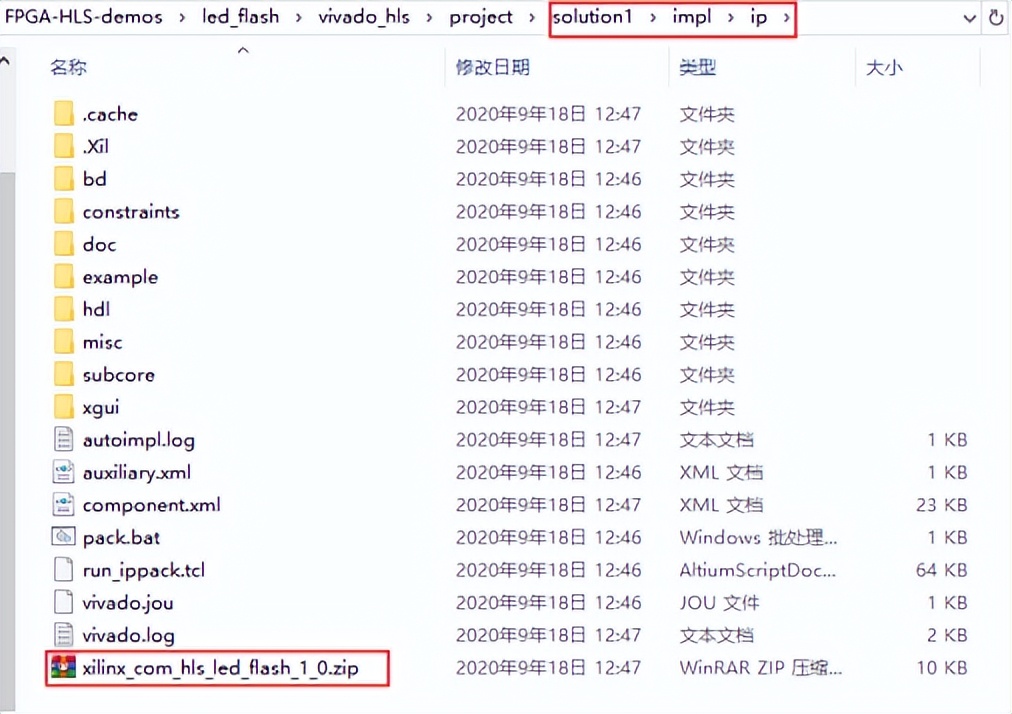

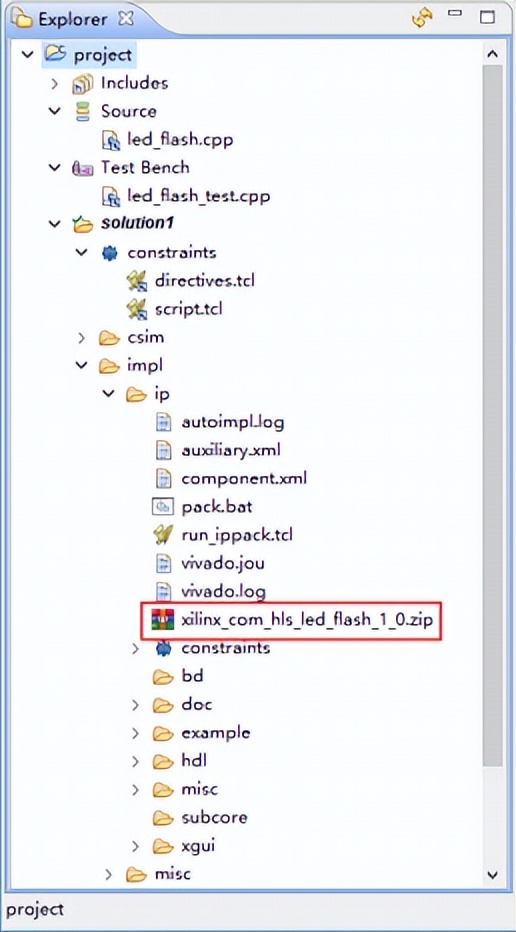

运行完成后,将会在案例“vivado_hlsprojectsolution1implip”目录下生成 IP 核。

图 14

图 15

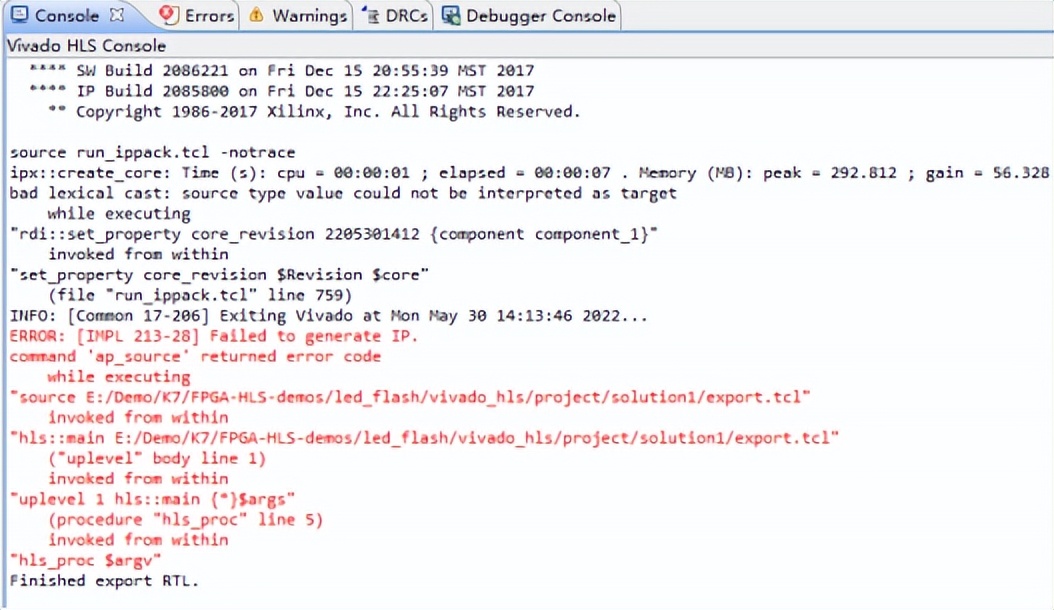

从 2022 年 1 月 1 日起,Vivado HLS 和 Vitis HLS 的导出 IP 命令将无法正常使用。原因 是 HLS 工具将 ip_version 设置为 YYMMDDHHMM 格式, 该值作为带符号整数(32 位) 访 问,会导致溢出并产生如下类似错误。

图 16

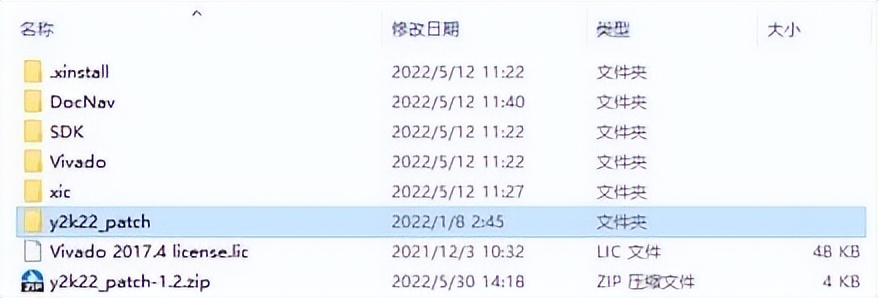

根据 Xilinx 官方建议,请将产品资料“4-软件资料Tools”目录下的y2k22_patch-

1.2.zip 补丁解压至 Vivado 2017.4 安装路径下。

图 17

确保 Windows 下已安装 Python 工具(2.7.5 版本以上),进入 Vivado 2017.4 安装路

径根目录下, 执行如下命令使用 Python 工具安装补丁。 安装完成后, 即可重新进行 IP 核

封装。

CMD# cd /d E:AppxilinxVivado

CMD# python y2k22_patchpatch.py

图 18

1.5 IP 核测试

进入案例“hls_ip_demoproject”或“hls_ip_demohwproject”对应平台 PL 端 IP 核测 试 Vivado 工程目录,双击.xpr 文件打开工程,工程默认已添加待测试的 IP 核。

图 19

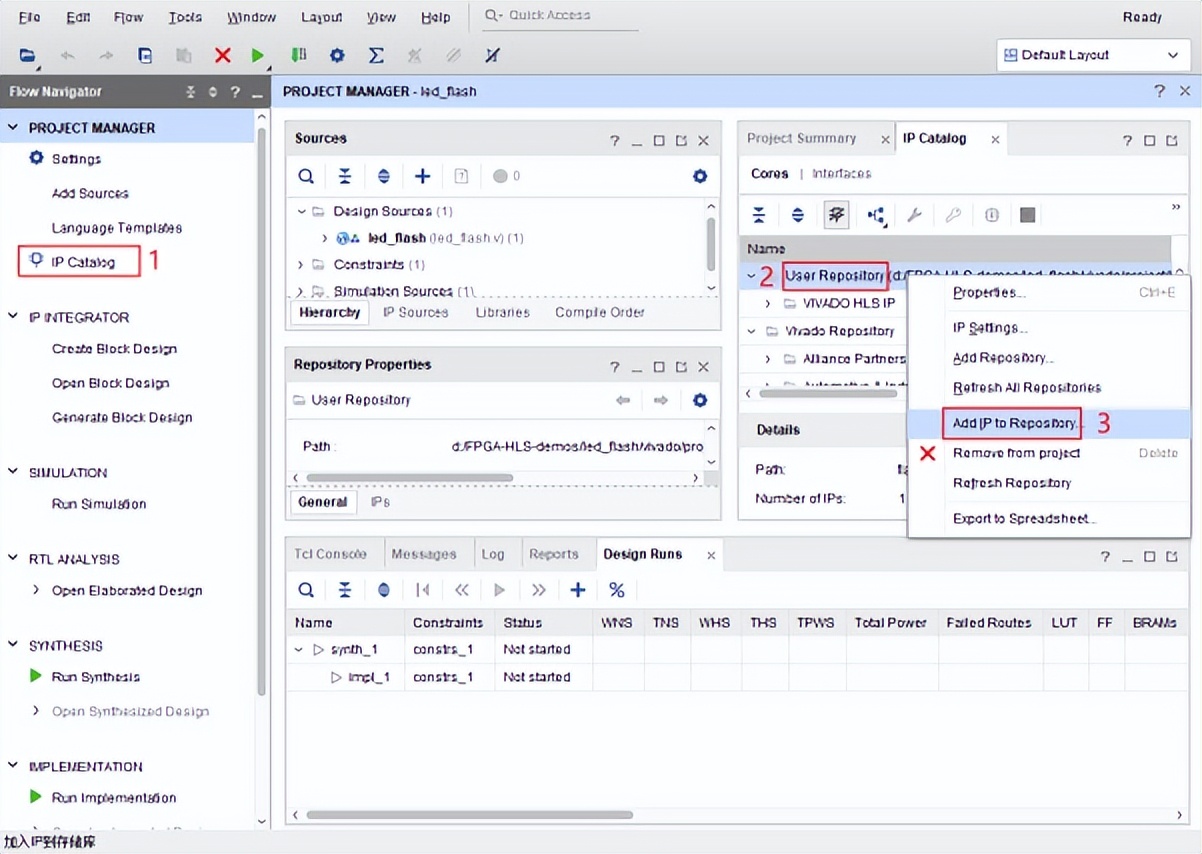

如需自行导入 IP 核, 请参考如下步骤。

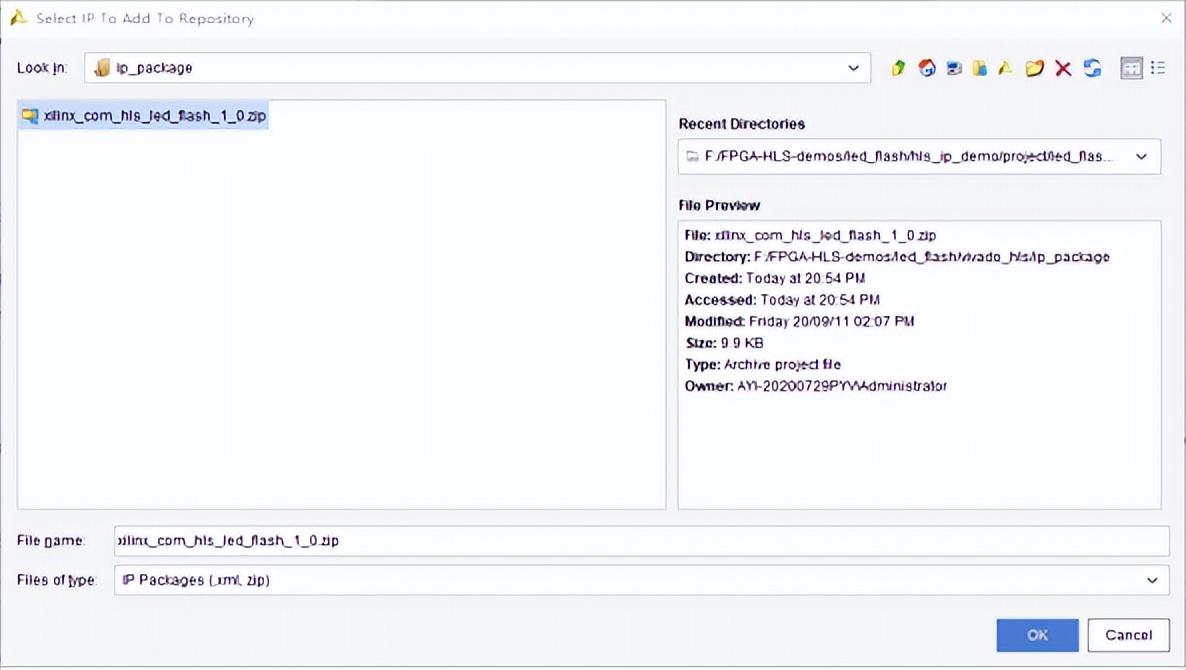

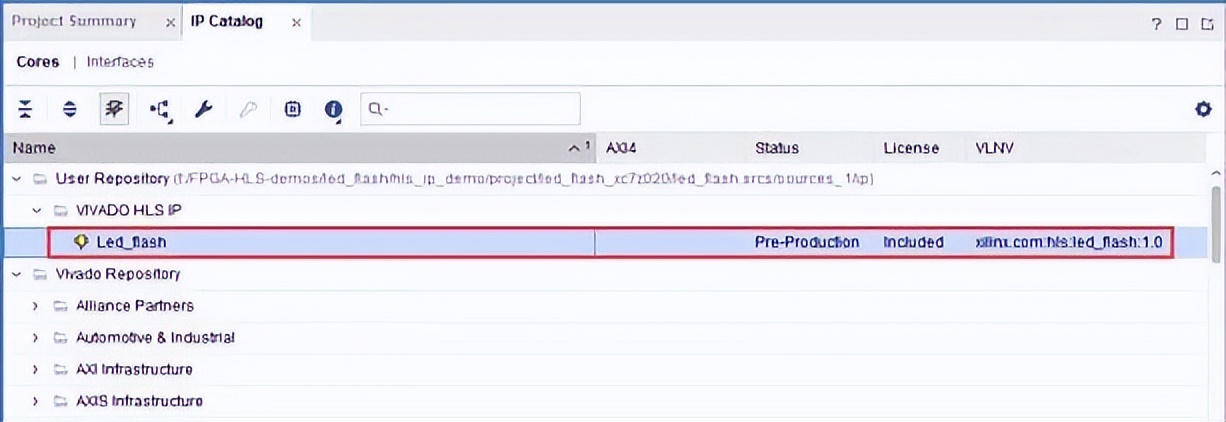

(1) 请点击“IP Catalog -> User Repository -> Add IP to Repository …” ,在弹出的界面中选择 IP 核后点击 OK。

图 20

图 21

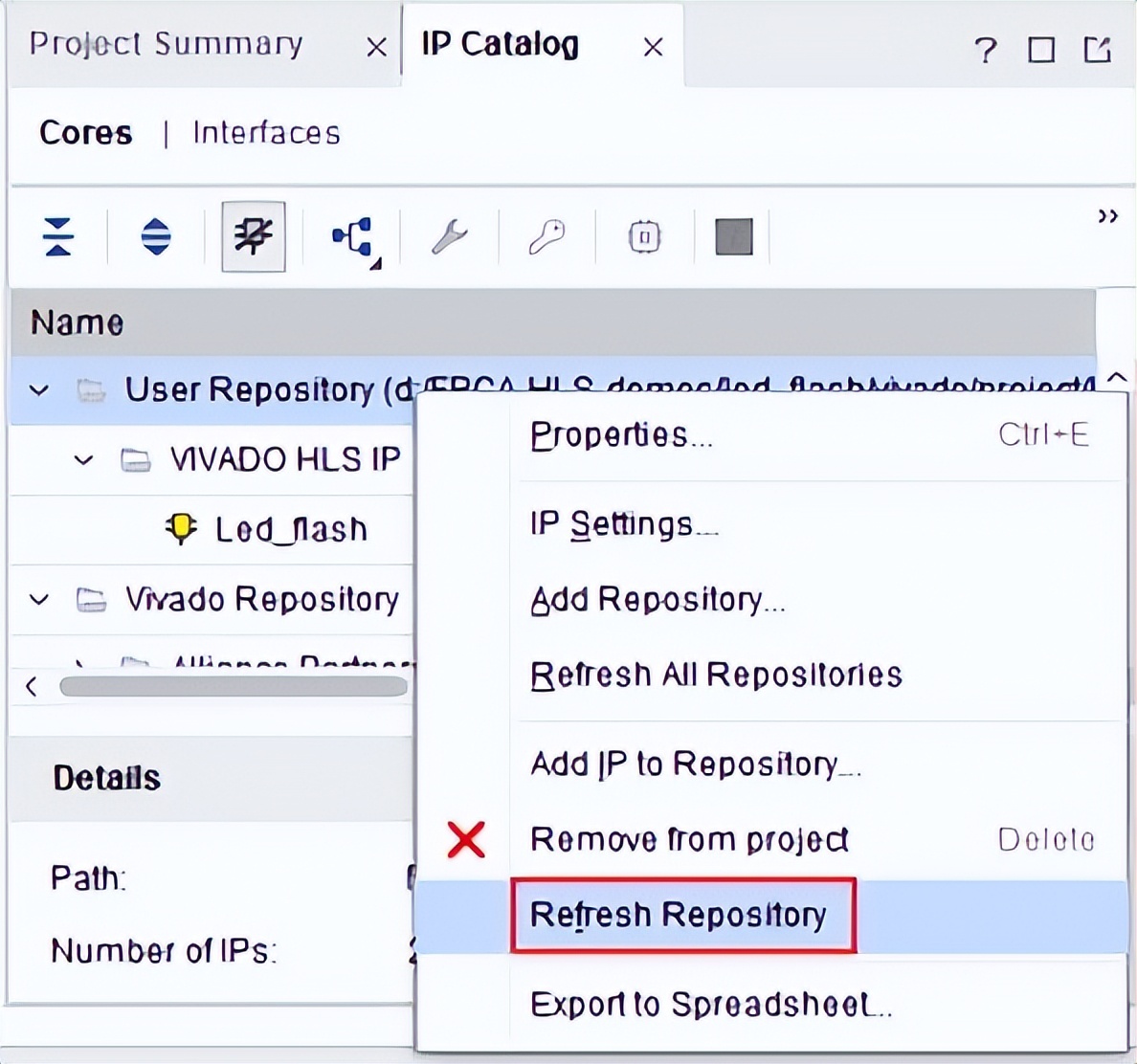

(2) 右击“User Repository”后点击“Refresh Repository”,即可看到添加的 IP 核。

图 22

图 23

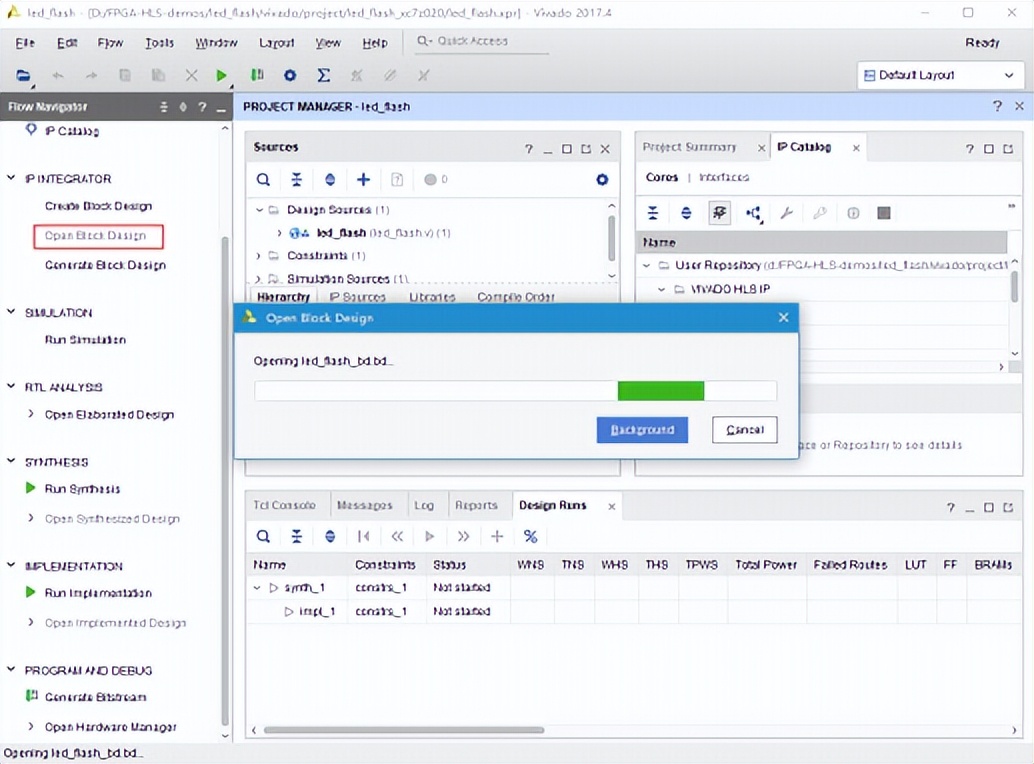

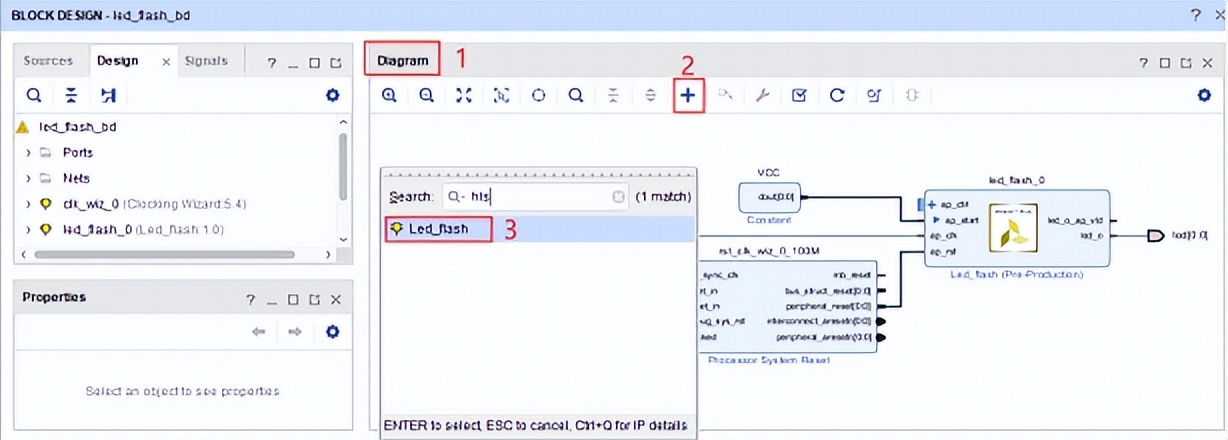

(3) 如需添加 Vivado 自带的 IP 核, 点击“Open Block Design”,在弹出的界面中点击

, 并选择所需 IP 核将其导入工程。

图 24

图 25

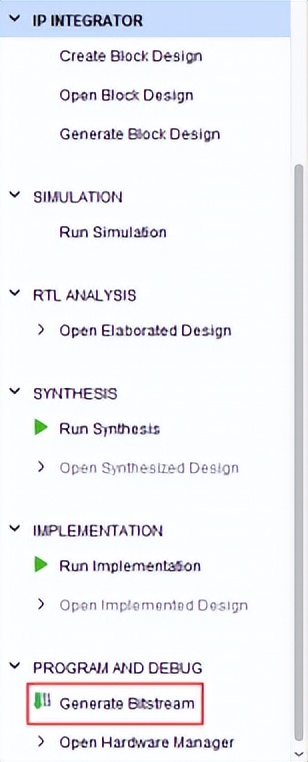

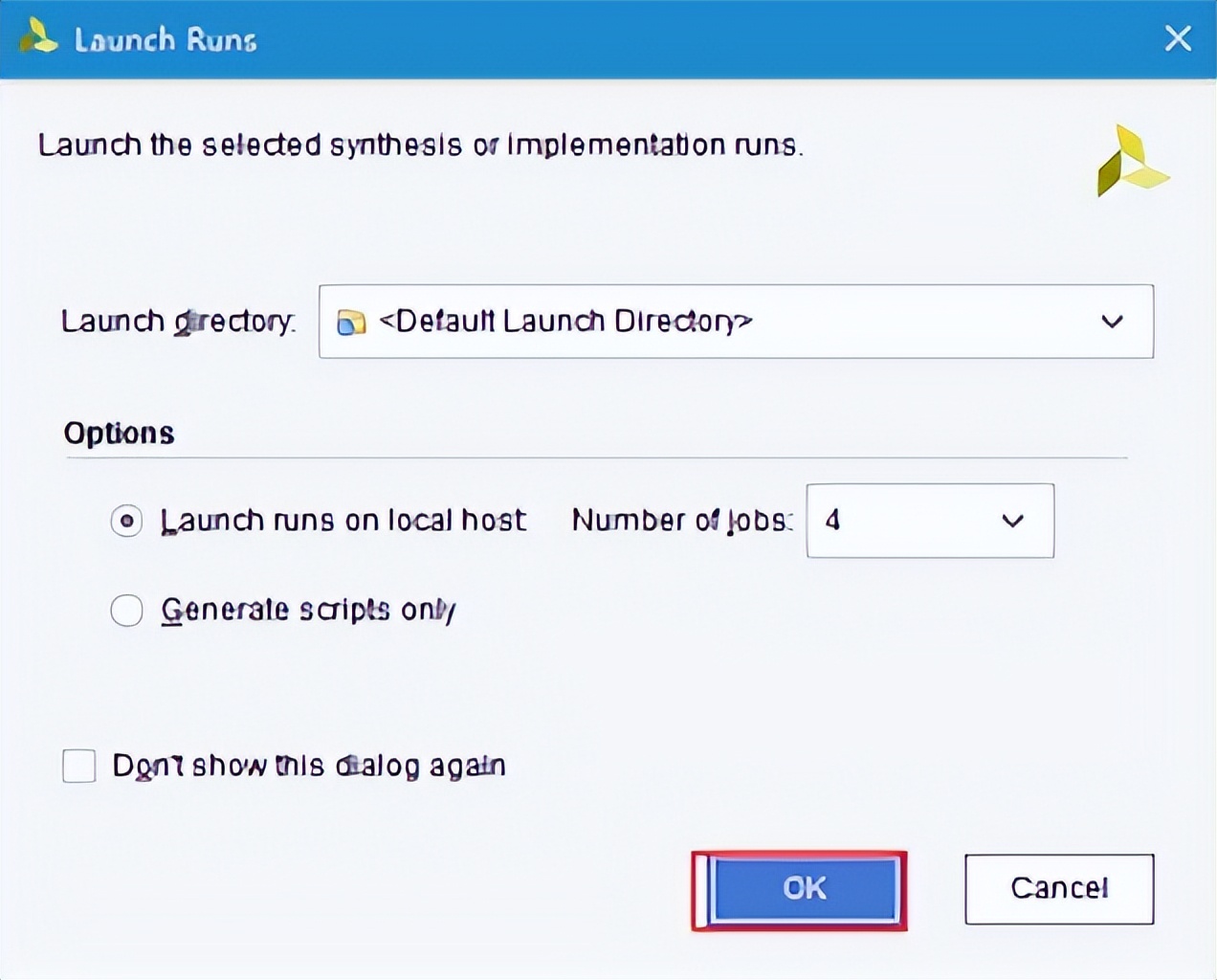

点击 Vivado 界面左侧的“Generate Bitstream”选项,在弹出的界面中点击 OK 进行 PL

端 IP 核测试 Vivado 工程编译。

图 26

图 27

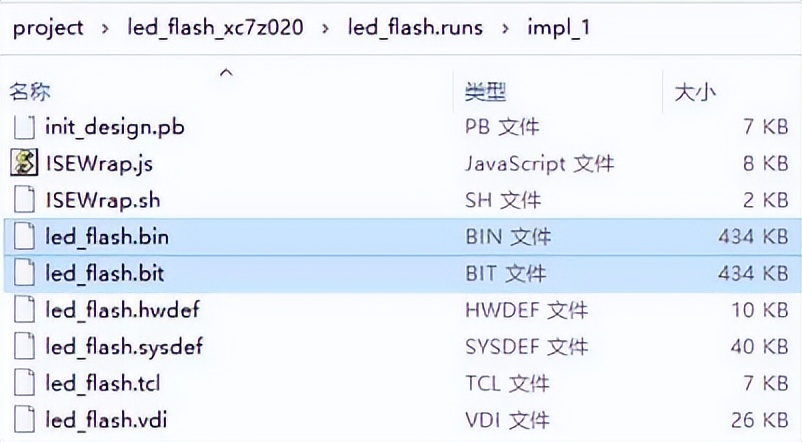

编译完成后,将会在工程“led_flash.runsimpl_1”目录下生成.bit 和.bin 格式可执行文

。

图 28

参考 PL 端案例开发手册说明加载 PL 端.bit 格式可执行文件,即可看到评估底板的 LED2 进行闪烁。