场效应晶体管(Field Effect Transistor, FET)简称场效应管,是一种由多数载流子参与导电的

半导体器件,也称为单极型晶体管,它主要分型场效应管(Junc

tion FET, JFET)和金属-氧化物半导体场效应管(Metal-Oxide Semiconductor FET,MOSFET),属于电压控制型半导体器件,具有输入电阻高、噪声小、功耗低、动态范围大、易于集成、无二次击穿现象、安全工作范围宽等优点。

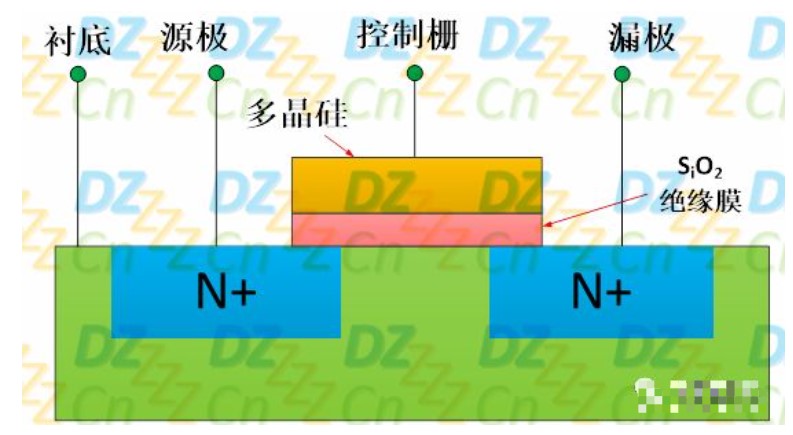

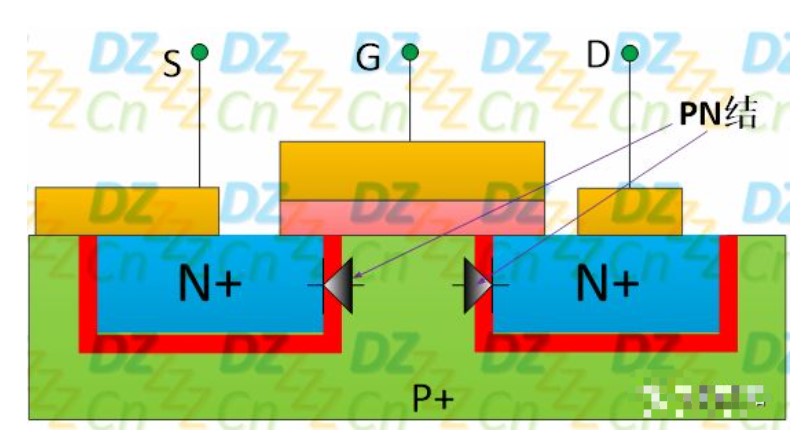

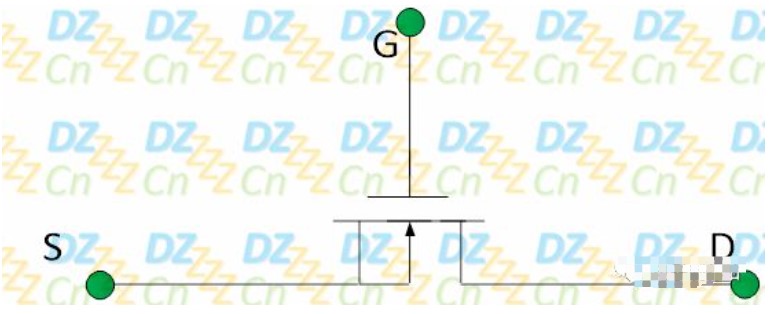

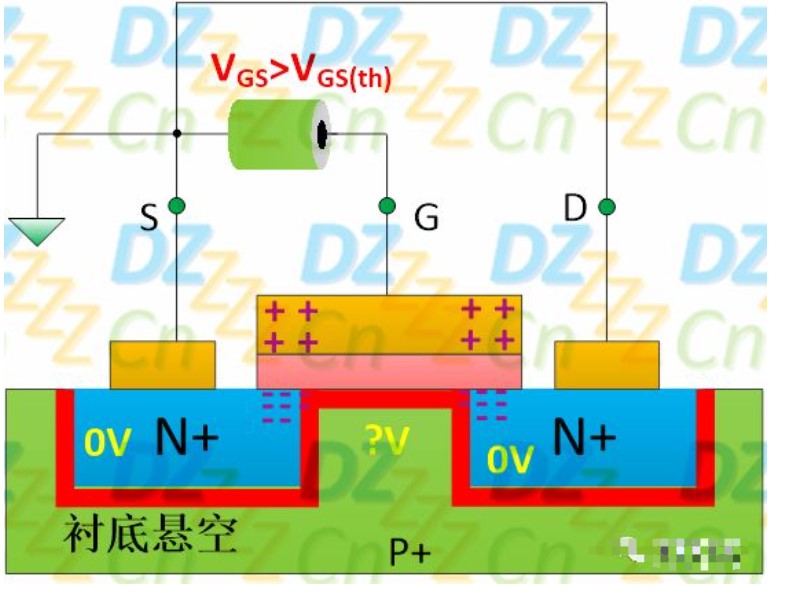

本节我们讲解一下N沟道增强型MOS场效应管,其基本结构如下图所示:

如上图所示,在一块P型

硅片(半导体)衬底(Substrate,也有称为Bulk或Body)上,形成两个高掺杂的N+区,分别命名为源(Source)区与漏(Drain)区,从中引出的电极分别称为源极(S)与漏极(D)。在P型衬底表面覆盖薄薄的一层

SiO2(二氧化硅)作为绝缘层,叫栅氧化层或栅绝缘层,再在上面覆盖一层

金属(现今广泛使用多晶硅,Poly-Silicon),其引出的电极称为栅极(Gate, S),这就是金属-氧化物-半导体(Metal-Oxide-Semiconductor)名称的由来。

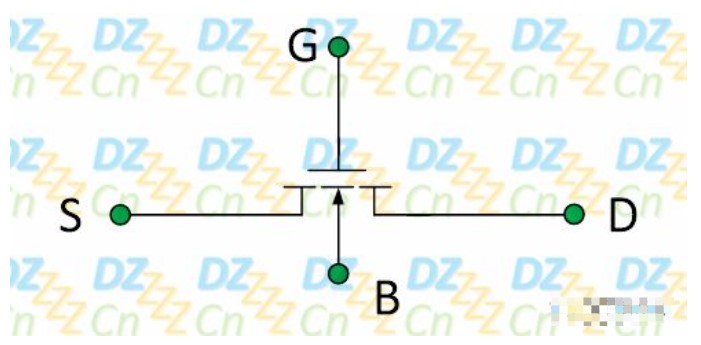

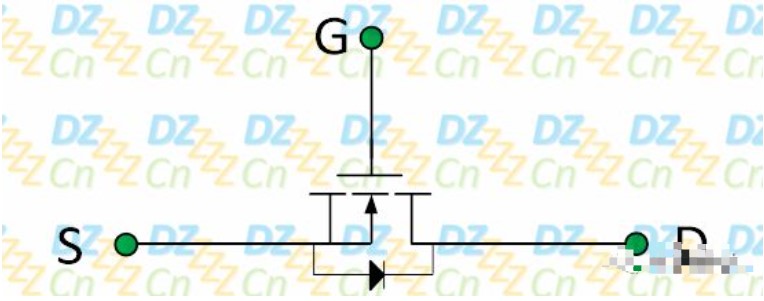

其原理图符号应如下所示:

从结构上可以看出,MOS管是完全对称的,因此

理论上源极S与漏极D是可以互换使用的。在MOS管中,源极为提供载流子的端子,而漏极为接收载流子的端子,源和漏的命名也由此而来,N沟通MOS管的源极通常连接至

电路的最低电位,而P沟通MOS管的源极连接至电路的最高电位(为什么?)。

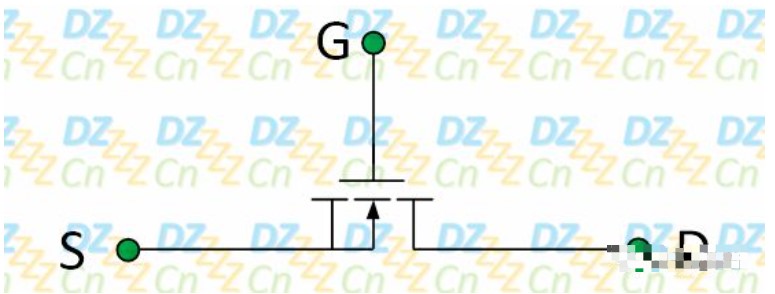

对于单个MOS场效应管,衬底B通常与源极S连接在一起,这样两个电极的电位是一致的,这样可以避免体效应引起阈值电压的漂移(后面会提到),因此,你看到的MOS场效应管符号可能如下图所示:

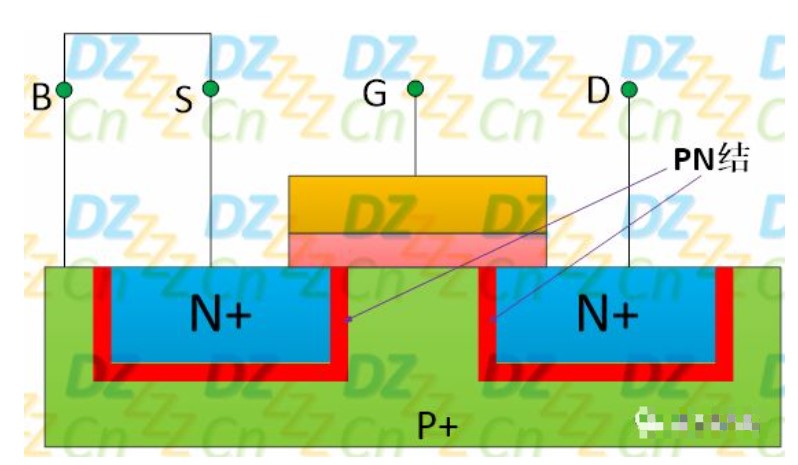

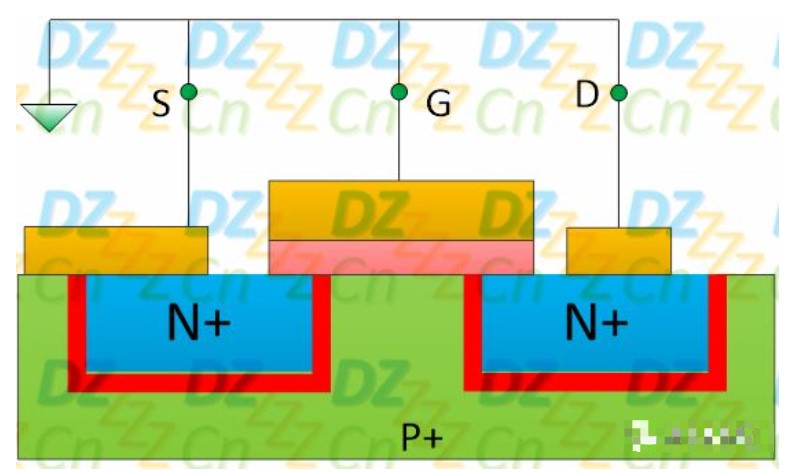

这样场效应管就应该如下图所示:

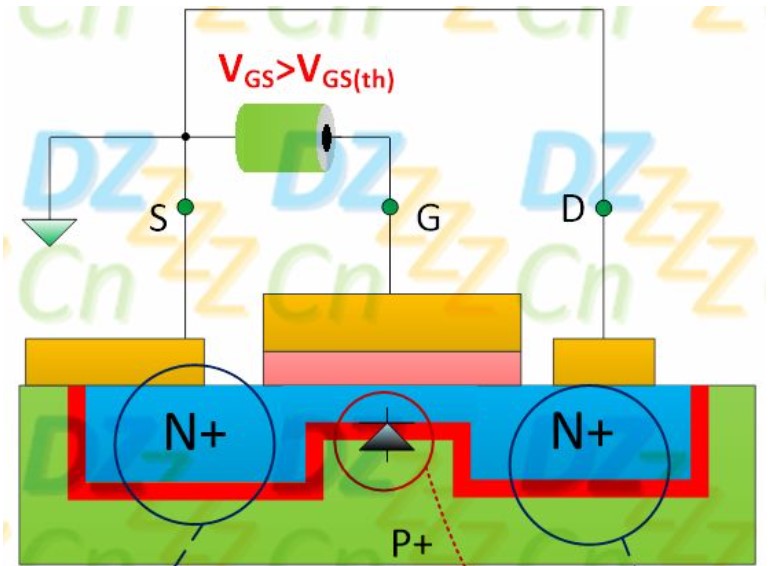

实际的场效应管通常把衬底电极B与源极电极S做在一起,因此,通常我们是看不到衬底电极的。由于N区与P型衬底之间存在PN结(也叫做耗尽层),因此上图中已经形成了两个二极管,如下图所示:

很明显,左边的那个PN结(二极管)因B极与S极的短接而相当于不存在,右侧的二极管则称为寄生二极管,它是由源极S指向漏极D,因此,我们也有可能看到如下图所示的MOS场效应管原理图符号:

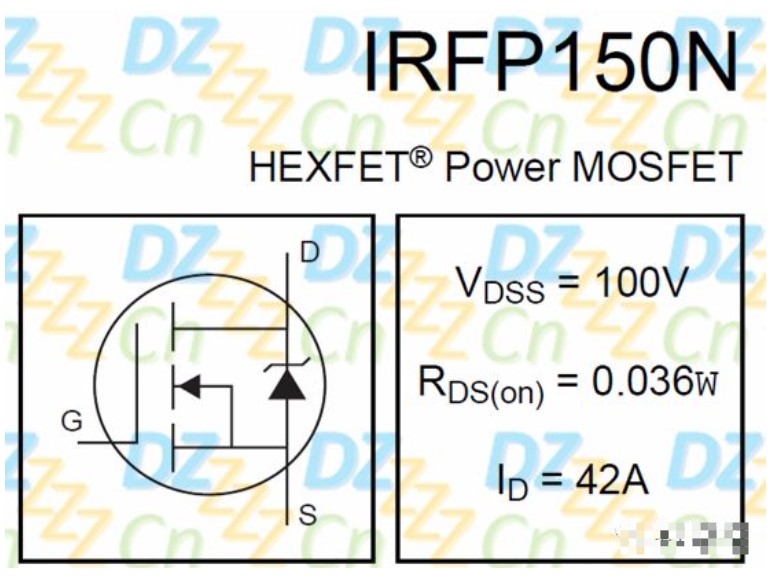

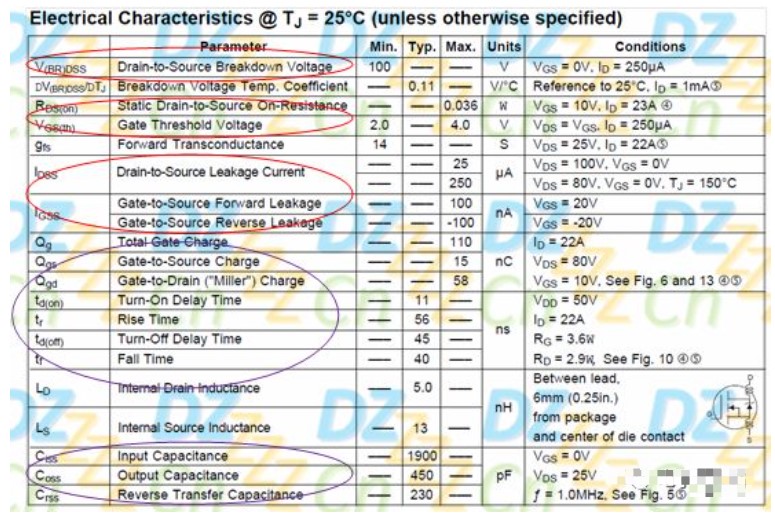

下图来自国际整流器IR的NMOS场效应管IRFP150N数据手册:

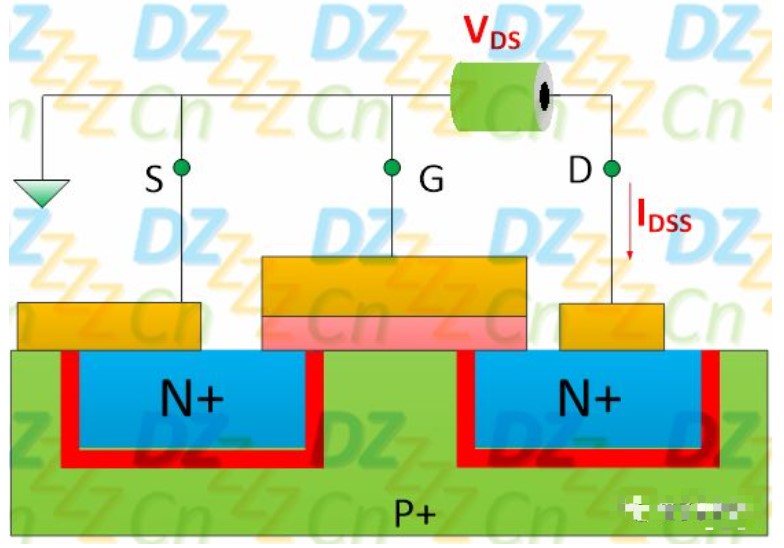

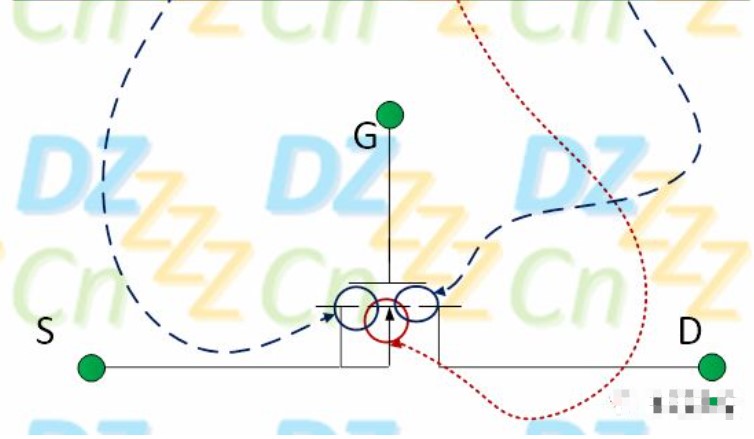

下面我们来看看N沟通MOS场效应管的工作原理。假设初始状态如下图所示,即栅-源电压VGS与漏-源电压VDS均为0V,这种状态称为截止区,亦即漏极D与源极S之间是不导通的。

如果此时在漏-源两极之间施加正向电压VDS,则仍然有一定的漏电流,我们称之为

漏源泄漏电流IDSS(Drain-to-Source Leakage Current),增强型MOS管的IDSS很小,一般是uA级别,如下图所示:

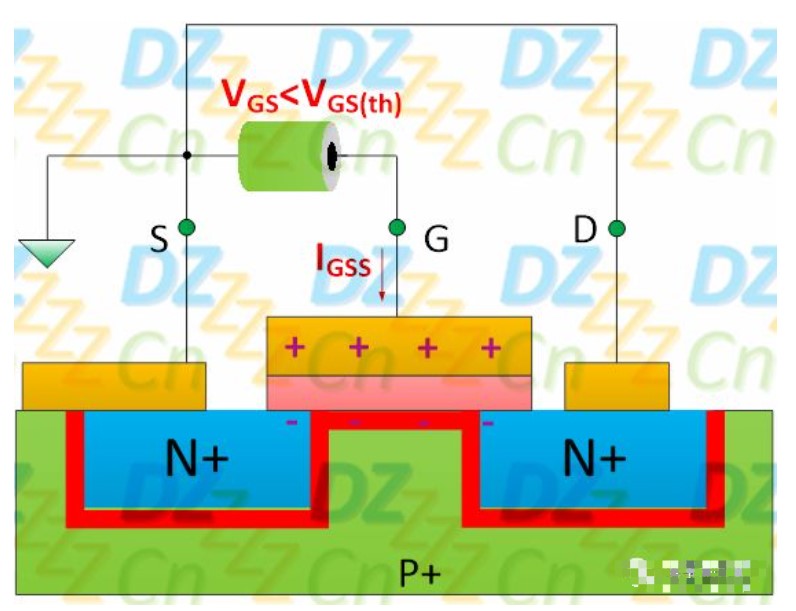

当对栅极G与源极S施加正向电压VGS时,在正向电场的作用力下,N区中的

电子(多子)与P型衬底中的电子(少子)均被吸附到栅极下的衬底表面,并与P型衬底中空穴(多子)复合而形成负离子为主的空间电荷区,这个空间电荷区把两侧的空间电荷区连接起来,但这个时候的栅-源电压VGS比较小,因此,漏极D与源极S之间的沟道仍然是不导通的(即截止区),如下图所示(关于电子与空穴复合可参考文章《二极管》):

此时,也有相应的

栅-源泄漏电流IGSS(Gate-to-Source Forward Leakage),因为栅极与源极之间相当于两个平板,而SiO2绝缘层相当于平板之间的介质,因此形成的平板电容肯定会有一定的泄漏电流,此值越小表示栅极与源极之间的绝缘氧化层的绝缘性越好。

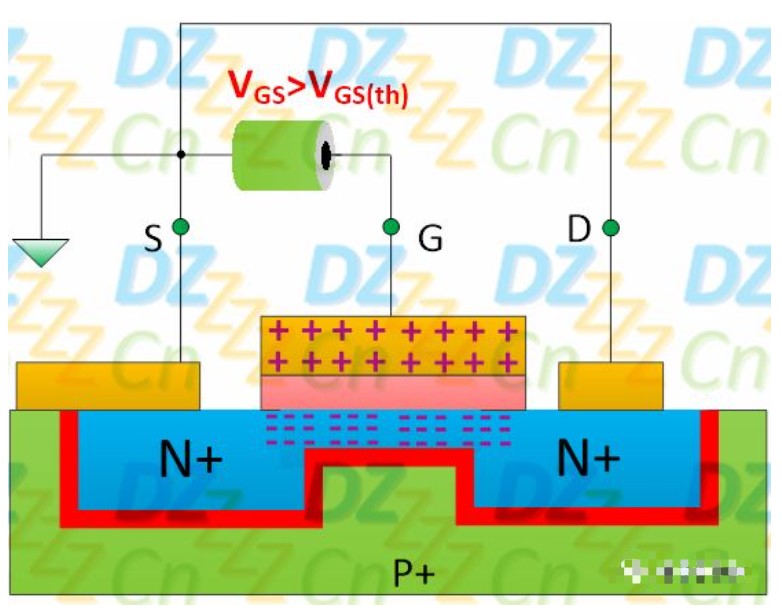

当栅-源电压VGS继续增大时,N区与P型衬底中的电子被进一步吸附到栅极下的衬底表面,直到电子的浓度大于空穴浓度,原来两个N区中间的P型衬底变换为N型,并将两侧的N区连通。我们把刚刚能使源-漏两极之间能够导通的电压称为

阈值电压VGS(th)(Gate Threahold Voltage),此值取决于场效应管的工艺,绝缘层越薄(电势梯度越大),N+区掺杂浓度愈高(电子越多),衬底掺杂浓度愈低(则P衬底的空穴越小,需要复合的电子就越少),则相应的阈值电压就越小。

这个导电沟通是由原来的P型衬底转变为N型的,因此也称为反型层。导电沟通也存在一定的电阻,我们称其为

通态漏源电阻RDS(on)(Static Drain-to-Source On-Resistance),显然,栅-源极间电压VGS越大,则反型层中的自由电子浓度也相应越大,导电沟道也越深,因此RDS(on)也越小,但是VGS也有其

最大值VGSS,通常为±10V~20V左右,超过此值则栅-源极间可能会被击穿。

此时的N型导电沟道与P型衬底之间也形成了一个PN结,如下图所示:

原理图符号中的箭头方向与该PN结的方向是一致的,因此以后你就不用记什么“箭头指向栅极是N沟道”之类的口诀了,而原理图符号两侧的线段则分别表示栅极与源极,并且在默认情况下是不导通的,所以是三条虚线段。很容易可以预想到,耗尽型MOS管的原理图符号应该是一条实线,因为耗尽型MOS管在默认情况下源极与漏极之间是导通的,如下图所示:

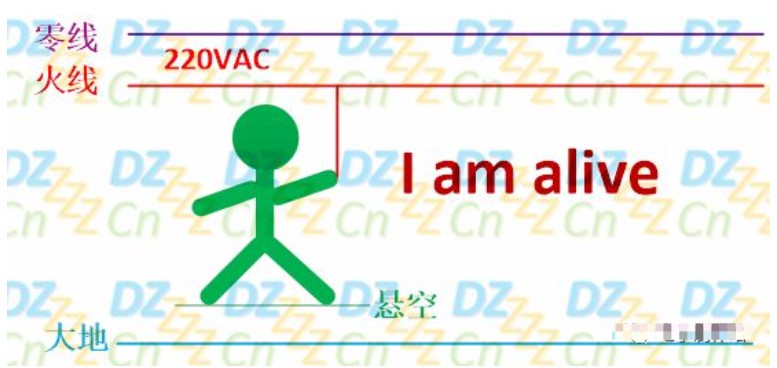

另外,我们也应该看到,正是由于P型衬底与源极S连接在一起,当对栅-源两极之间施加VGS正向电压时,才可以在相对较低的电场下也可以将P型衬底中的少子电子吸附过来,如果P型衬底没有与源极S相连接(悬空),或连接的是其它更高的电平,则由于P型衬底是悬空的(相当于栅-源电压找不到发力点),在正常的栅-源电压VGS电压下很难形成导电沟通,继而使MOS管无法正常工作。

换句话讲,在相同的外部条件下,我们需要更大的栅-源电压VGS才能形成N型导电沟道,亦即导致阈值电压VGS(th)的变化(漂移),如下图所示:

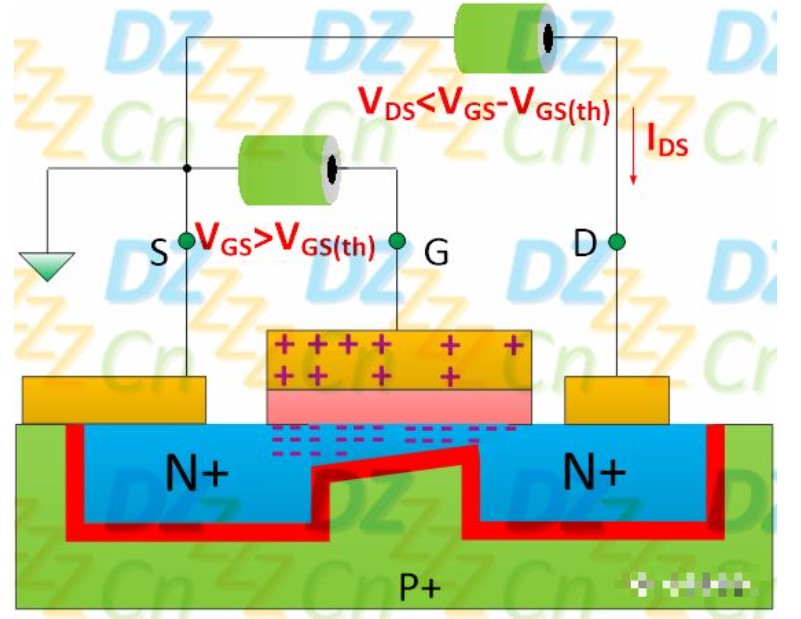

此时源极S与漏极D之间是导通的,如果在两个电极之间施加VDS正向电压,则会形成电流回路,如下图所示:

MOS管的漏-源极之间能通过的最大电流称为

漏极电流ID(Drain Current),也有些数据手册称为

源极电流IS(Source Current),其实两者是一致的。

同时我们也应该看到,相对于没有添加漏-源电压VDS前(VDS=0)的状态,栅-漏极之间的正向电压VGD会因为VDS的施加而减弱,即VGD=VGS-VDS,也就是说,栅-源极的正向电场最强,产生的导电沟通最深,而越往漏极靠近,产生正向电场逐渐减弱,这样导致导电沟通的深度是不均匀的。

这种状态也称为

非饱和区(Nonsaturation Region),也叫

变阻区(Ohmic Region)

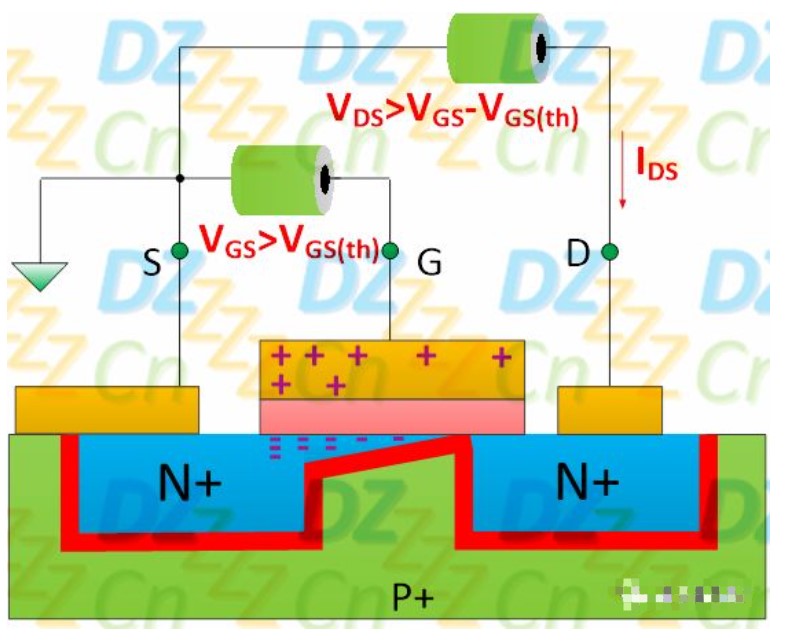

当漏-源电压VDS增大到其值为VGS-VGS(th)时,由于VGD形成的正向电场不足以在漏极端吸附足够的电子而造成N型沟道的消失,此时源极与漏极间也是不导通的。这种由VDS引起沟道不导通的现象称之为预夹断。这种状态也称为

饱和区(Saturation Region),也叫

放大区(Active Region),使用场效应管组成的放大电路应工作在此种状态(与三极管的饱和区不一样)。

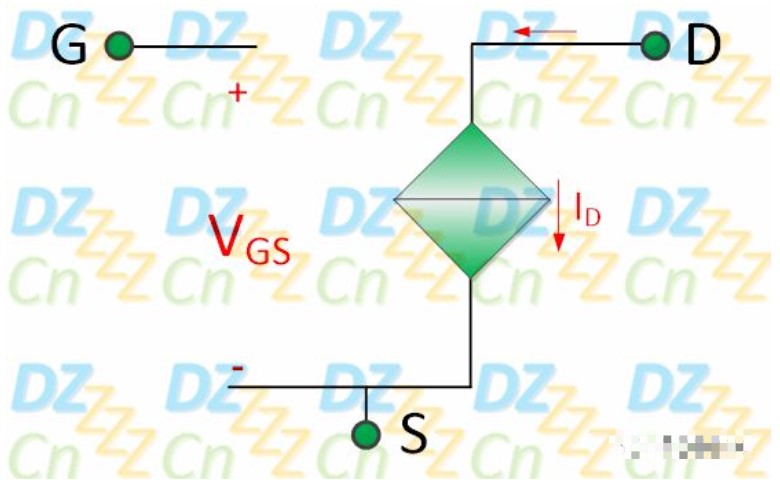

在MOS管的放大区,VDS的存在使其产生预夹断,这时漏极电流ID几乎不再受VDS控制,即仅受控于栅-源电压VGS,这与三极管的集电极电流IC受控于基极电流IB一样,只不过是由电压控制的电流源,它可以等效如下图所示:

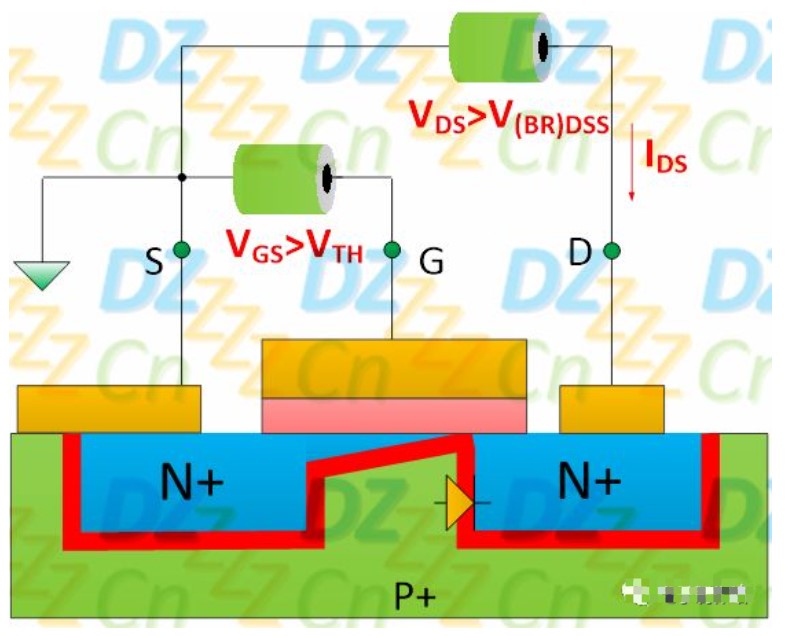

当漏-源电压VDS增大到某一程度时,漏极与P型衬底间的PN结引发雪崩击穿,此时电流迅速上升,MOS管进入到击穿区,如下图所示:

其中,

V(BR)DSS即漏-源击穿电压(Drain-to-Source Breakdown Voltage)

与三极管类型,MOS管也有相应的伏安特性曲线,但是MOS管输入栅极电流非常小,输入特性曲线就没有太大的必要,在共源极连接形式中,N沟道MOS管的输出特性曲线如下图所示:

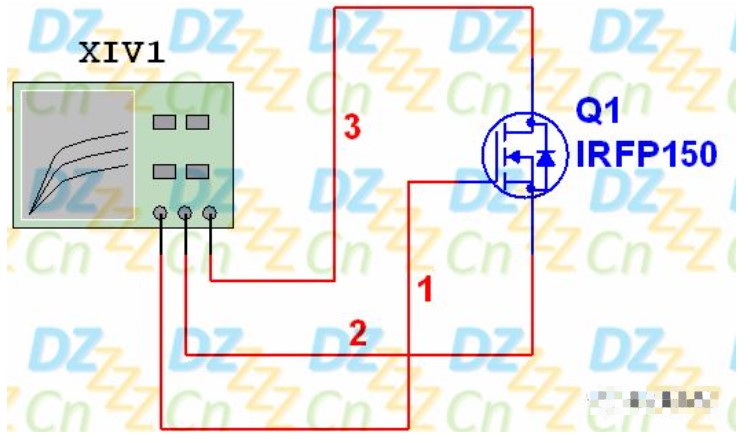

我们用下图所示的电路对IRFP150进行输出特性曲线的

仿真:

其中,XIV1为IV特性分析仪(IV-Analyzer),也就是伏安特性曲线分析仪,非常适合于测量分立半导体

元件的伏安特性曲线,如二极管、三极管、场效应管等。

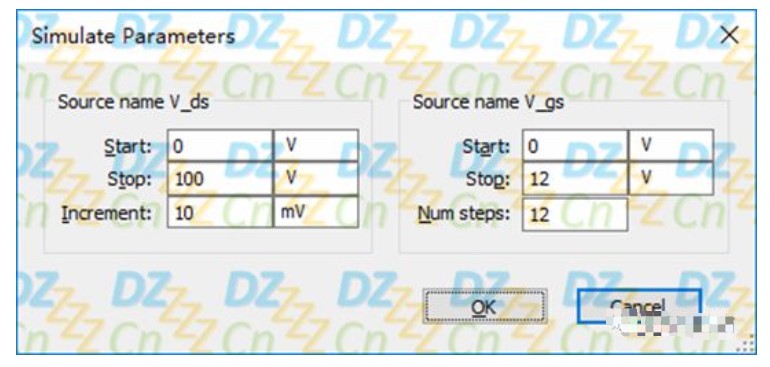

双击XIV1后,在弹出的对话框内进入Simulate Parameters仿真参数设置界面,如下图所示进行设置:

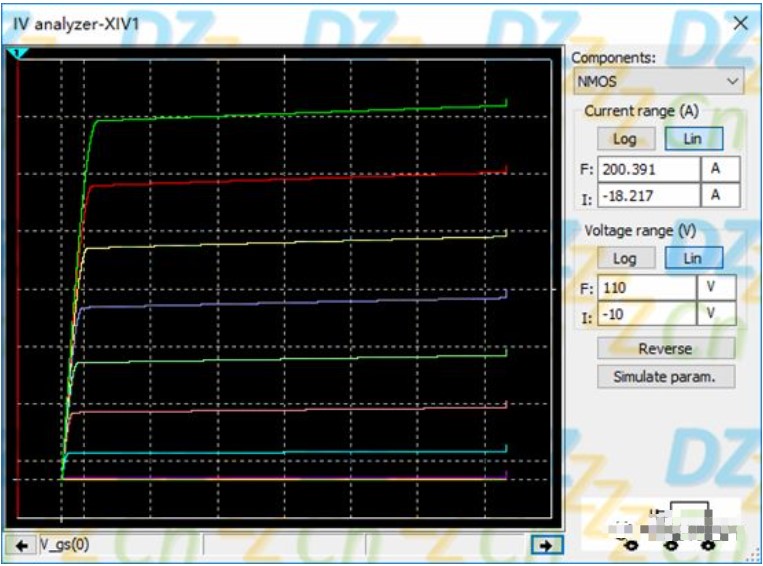

再运行仿真(交互式仿真模式下)即可出现如下图所示的伏安特性曲线:

下图为IRFP150数据手册的参数:

原作者: Jackie Long 电子制作站

举报

举报