1、IC设计中的多时钟域处理方法简析

我们在ASIC或FPGA系统设计中,常常会遇到需要在多个时钟域下交互传输的问题,时序问题也随着系统越复杂而变得更为严重。 跨时钟域处理技术是IC设计中非常重要的一个部分,我们需要学习并应用一些常用的处理方法,从而提高电路运行的稳定性,使得整个系统更鲁棒。 下面考虑ASIC设计场景,为了满足系统功能需求,整个系统由不同的功能块构成,例如:

处理器

存储器

浮点引擎

存储控制器

总线接口

高速接口

假如考虑处理器和存储器的工作频率为500MHz,带有存储器控制器的浮点引擎的工作频率为666.66MHz,总线接口和高速接口工作频率为250MHz,则该设计具有多个时钟,被视为多个时钟域的设计。

多时钟域设计常用方法如前所述,多个时钟域的处理问题是在传输数据和控制信号时,它对数据完整性有影响。下面的策略在ASIC设计阶段是有用的。

尝试为数据和控制路径优化制定策略。

尝试创建多个时钟域组来定义策略。

在多个时钟域之间传递控制信号时,尝试使用同步器的策略。

尝试使用FIFO和缓存的数据路径同步器来提高数据完整性。

现在讨论重要的跨时钟处理问题与策略及其在多时钟域设计中的使用。

多时钟域设计有哪些问题

如果我们考虑适度的门数设计或使用单时钟工作的处理器核心和设计,它可能在布局阶段由于额外的互连延迟而产生时序违例。但是这种设计可能会通过架构、RTL、综合和基于工具的优化调整来满足时序和性能。

现在考虑图中所示的需要多个时钟的设计,让我们试着理解设计中的问题。

1.由于多个时钟域,数据完整性是主要问题,设计需要通过数据完整性检查。

2.没有使用同步器的时钟域边界上的触发器将由于建立和保持违例而存在亚稳态问题。

3.该设计将存在时序违例,并且很难强制时序电路输出进入有效的合法状态。

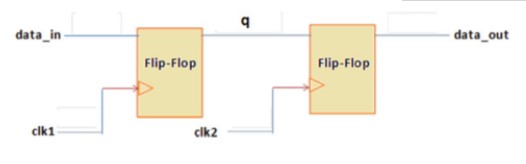

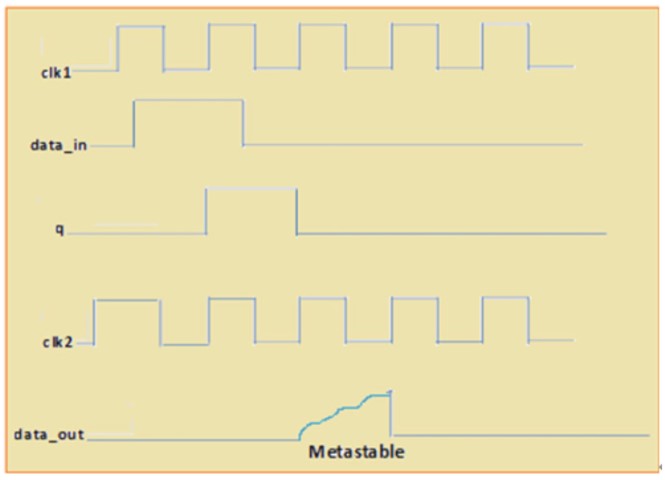

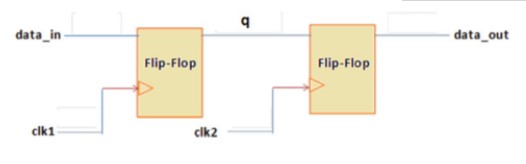

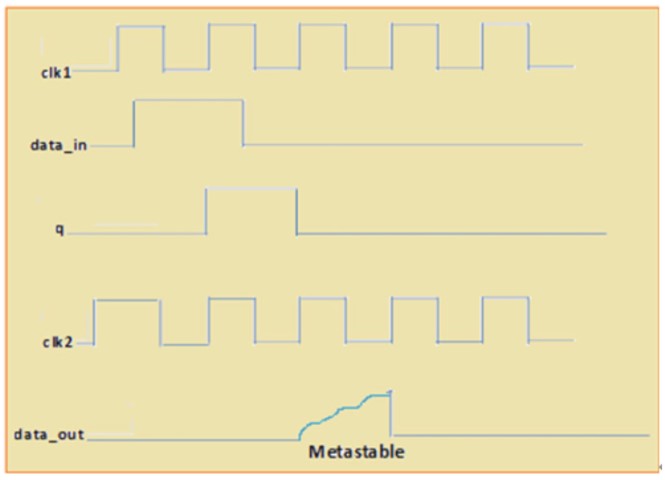

让我们用具有多个时钟域的时序电路来理解上面的内容。由于到达clk1和clk2之间的相差,第二个时钟域的触发器将有建立和保持违例,即触发器输出data_out将是亚稳态的。原因是时钟域1的q输出在clk2活动边的建立和保持窗口期间可能会改变,因此data_out将被迫进入非法状态,即亚稳态。如图1所示。

图1 多时钟域概念

时序如图2所示。

图2 亚稳态输出

原作者:Duoqiang Liu