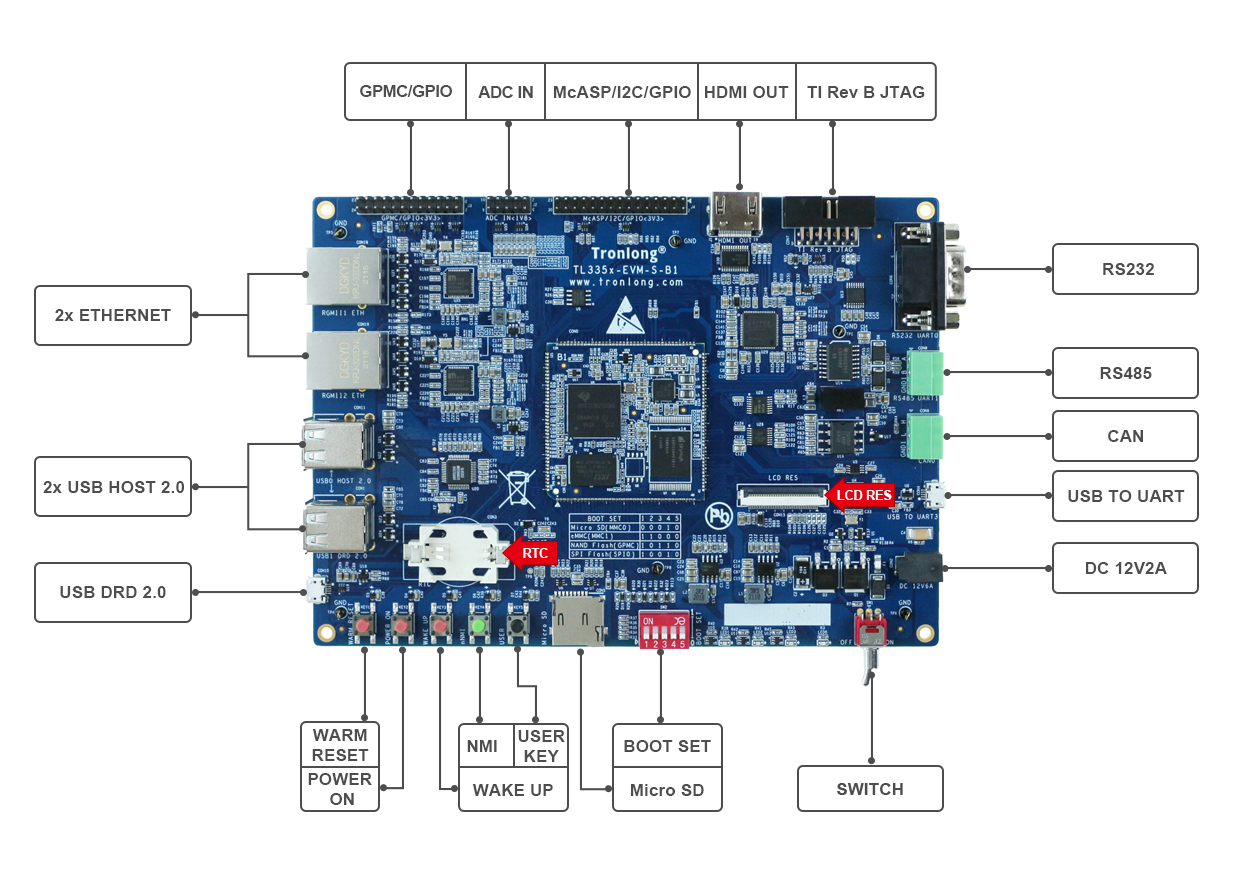

前 言本文档主要介绍嵌入式初级学习者,在使用核心板/开发板过程中,所做的一些硬件接口资源以及设计注意事项等内容。本篇文章是基于创龙科技TL335x-EVM-S开发板,它是一款基于ti Sitara系列AM3352/AM3354/AM3359 ARM Cortex-A8高性能低功耗处理器设计的评估板。

评估板接口资源丰富,引出双路千兆网口、LCD、HDMI、GPMC、CAN等接口,方便用户快速进行产品方案评估与技术预研,应用在通讯管理、数据采集、人机交互、运动控制、智能电力等典型领域。

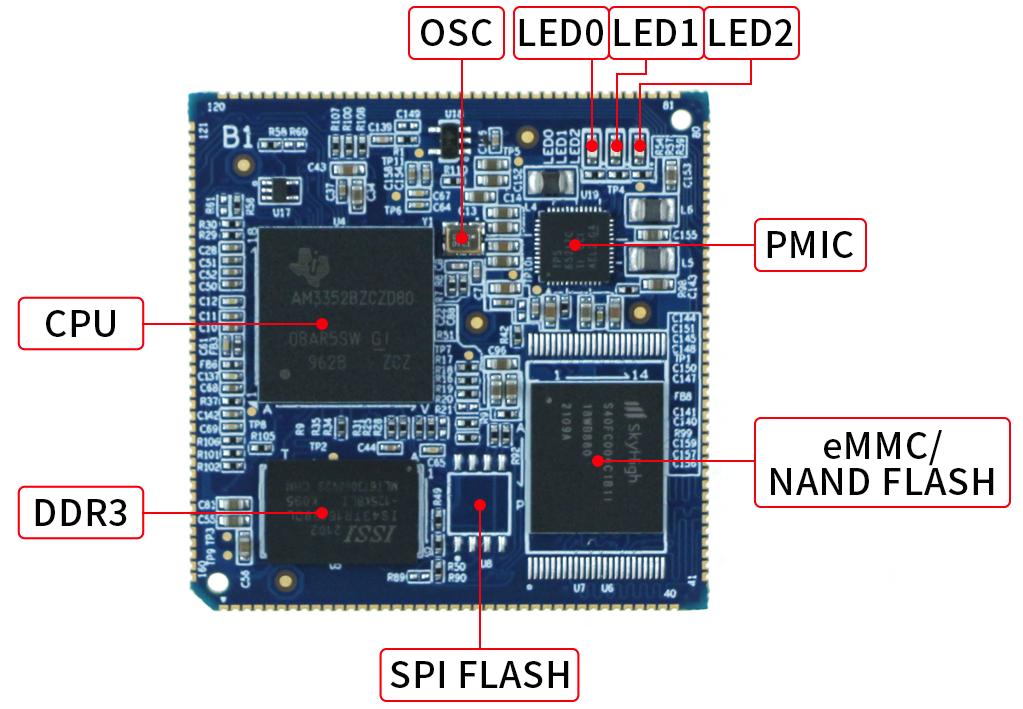

AM335x的IO电平标准一般为3.3V,上拉电源一般不超过3.3V,当外接信号电平与IO电平不匹配时,中间需增加电平转换芯片或信号隔离芯片。按键或接口需考虑ESD设计,ESD器件选型时需注意结电容是否偏大,否则可能会影响到信号通信。 SOM-TL335x-S核心板SOM-TL335x-S核心板板载CPU、ROM、RAM、晶振、电源管理芯片、LED等硬件资源,并通过邮票孔连接方式引出IO。核心板硬件资源、引脚说明、电气特性、机械尺寸、底板设计注意事项等详细内容,请查阅《SOM-TL335x-S核心板硬件说明书》。

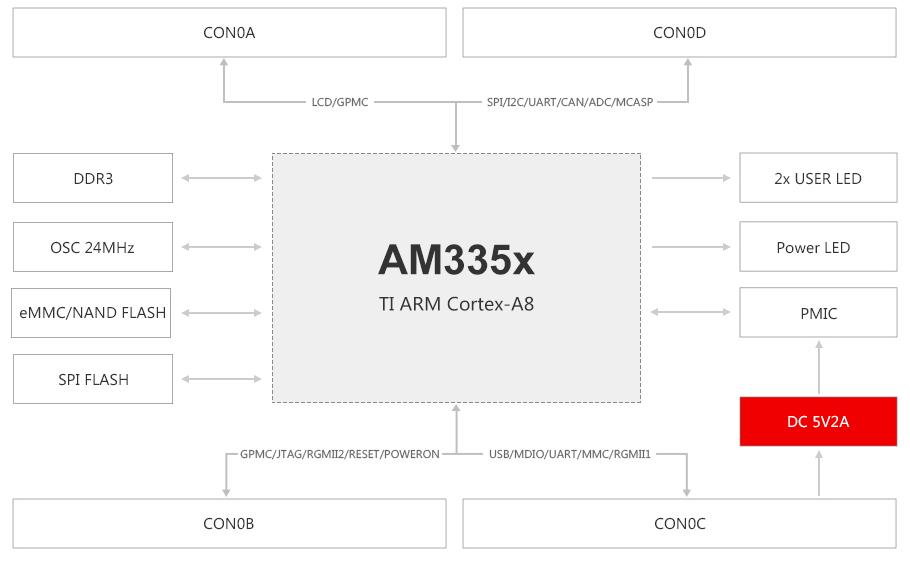

图 3 核心板硬件框图

图 4

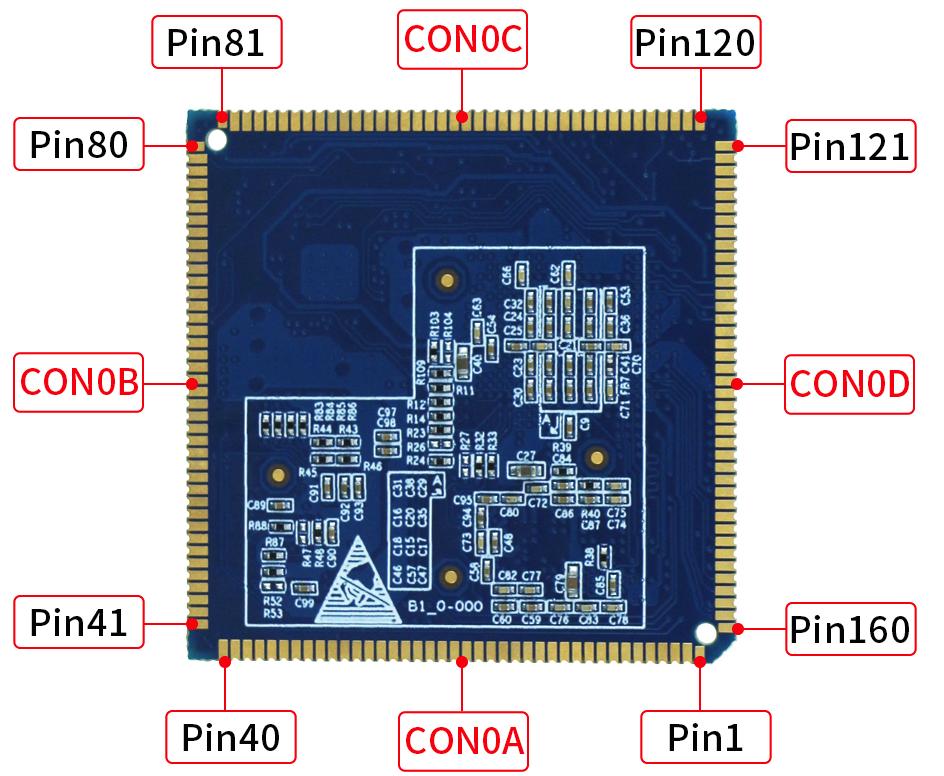

核心板采用4x 40pin邮票孔连接方式,共160pin,引脚间距为1.0mm。

图 5

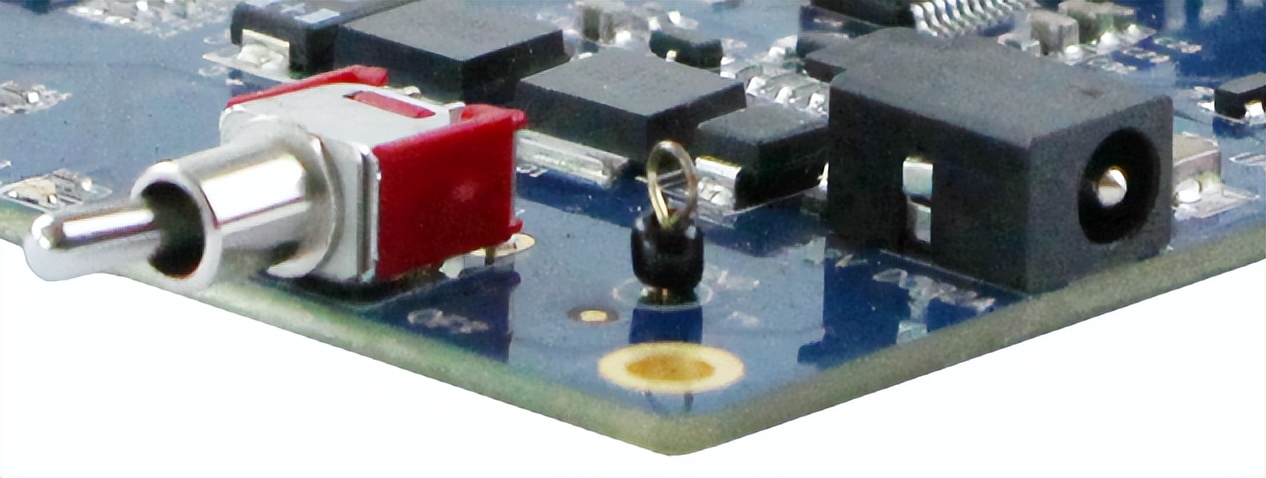

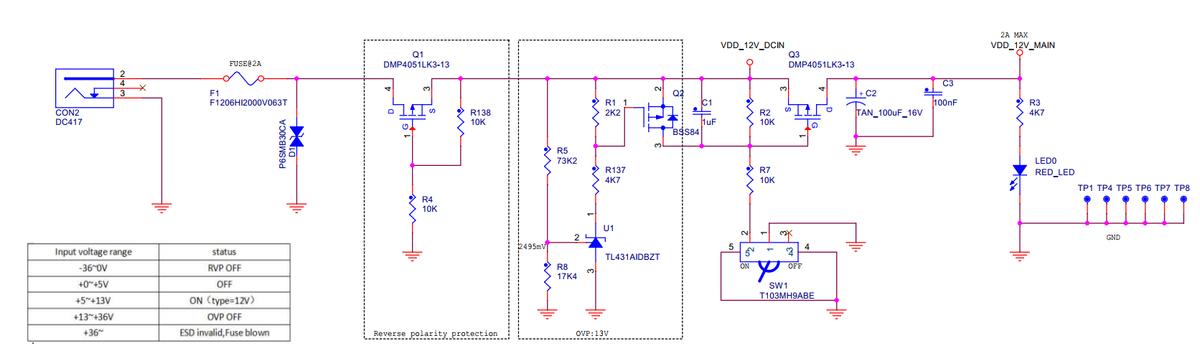

电源接口CON2为12V2A直流输入DC-417电源接口,可适配外径4.4mm、内径1.65mm电源插头。电源输入带有过流过压保护功能。SW1为电源摆动开关。

图 6

图 7

图 8

设计注意事项:

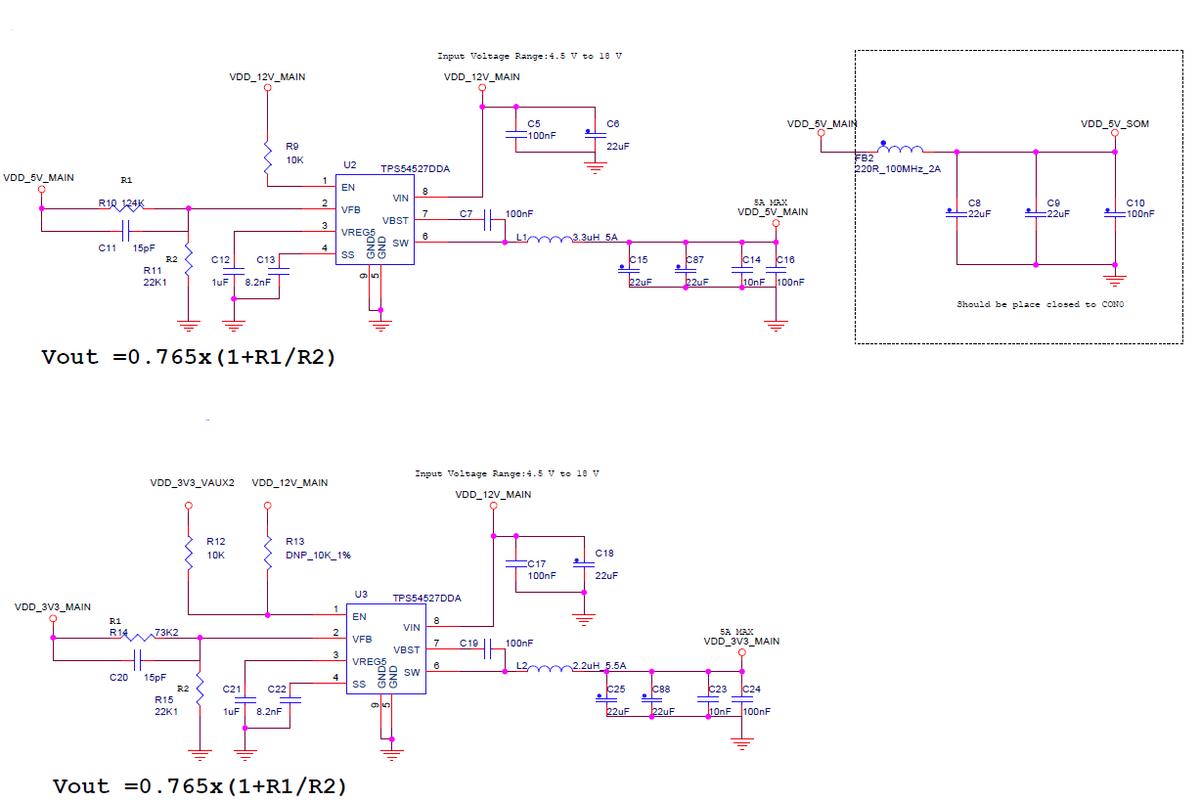

- VDD_12V_MAIN通过TPS54527DDA(DC-DC降压芯片)输出VDD_5V_MAIN供核心板使用,通过另一路TPS54527DDA芯片输出VDD_3V3_MAIN供评估底板外设使用。为使VDD_3V3_MAIN满足系统上电、掉电时序要求,需使用核心板输出电源VDD_3V3_VAUX2来控制VDD_3V3_MAIN的电源使能,使底板VDD_3V3_MAIN电源晚于核心板电源上电。

- VDD_5V_MAIN在核心板内部未预留总电源输入的储能大电容,底板设计时请在靠近邮票孔封装位置放置储能大电容。

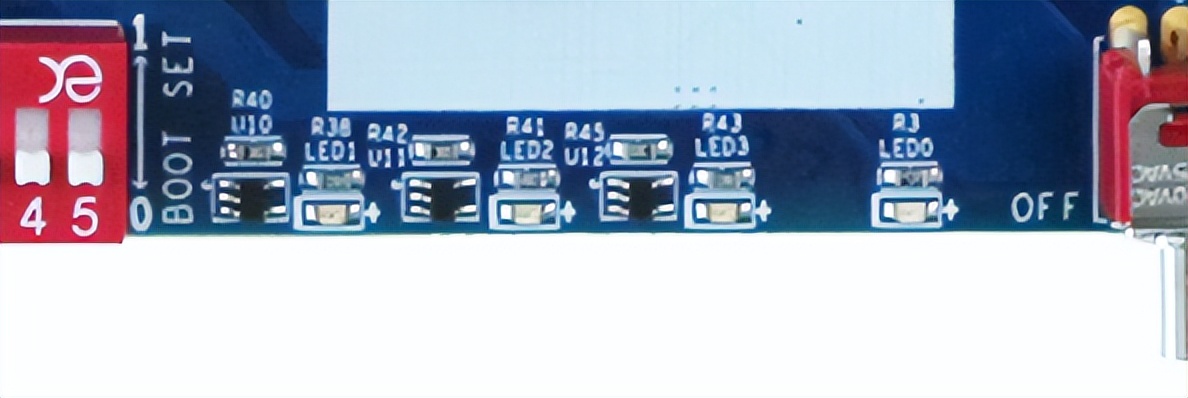

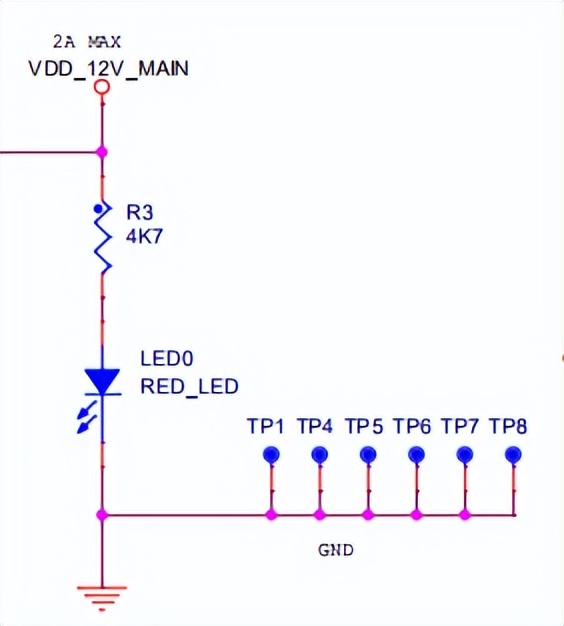

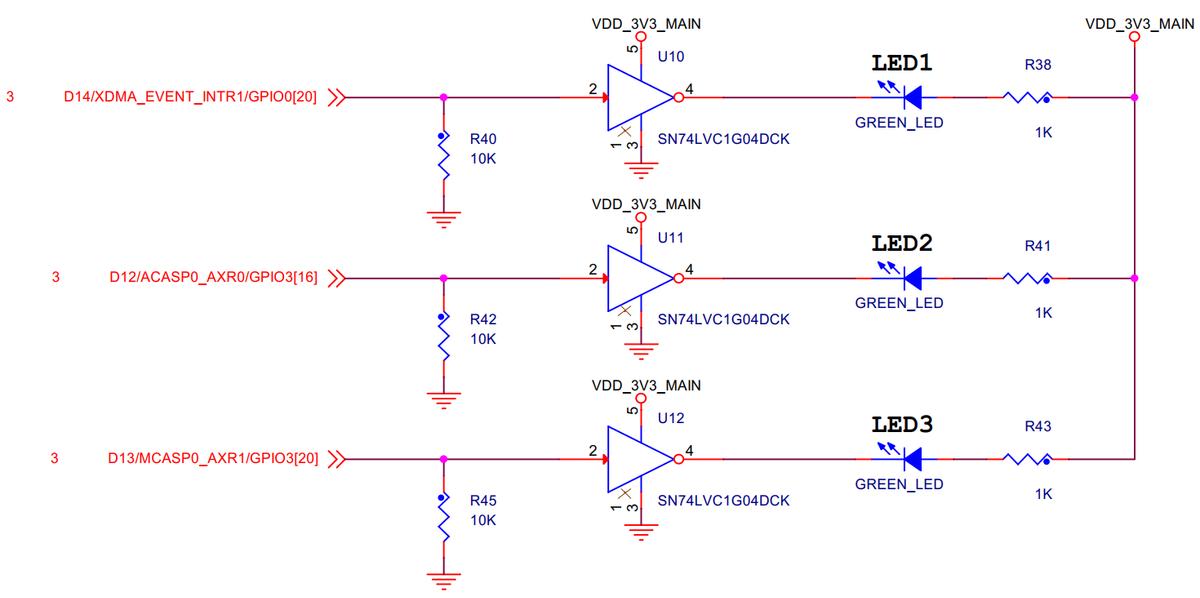

LED评估底板LED0为电源指示灯,系统上电默认点亮。评估底板LED1、LED2和LED3为用户可编程指示灯,通过GPIO控制,默认高电平点亮。

图 9

图 10

图 11

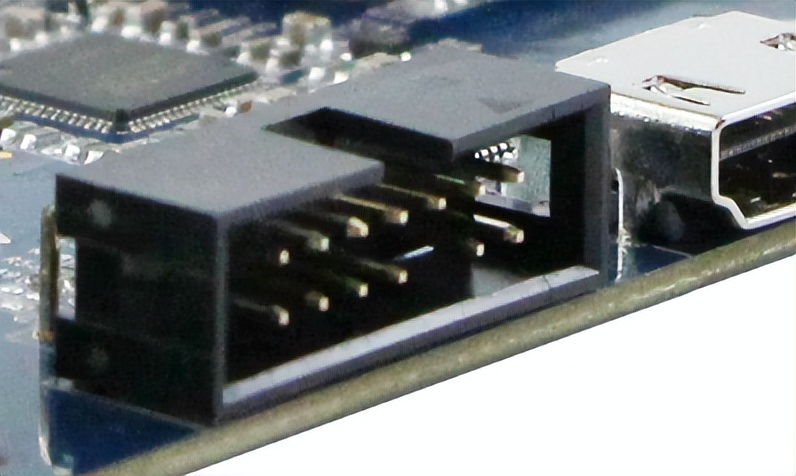

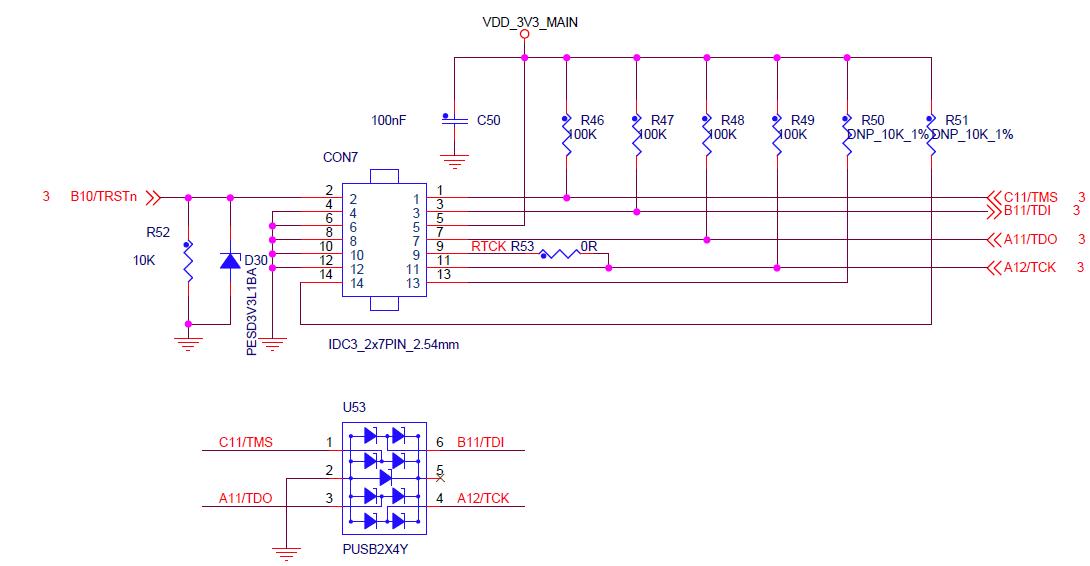

JTAG接口CON7为TI Rev B JTAG仿真调试接口,采用14pin简易牛角座连接器,间距2.54mm,可适配Tronlong的TL-XDS100V2、TL-XDS200和TL-XDS560V2仿真器。

图 12

图 13

设计注意事项:

- JTAG接口引脚信号电平为3.3V。

- 底板设计时,若JTAG总线仅引出测试点,通过飞线方式连接仿真器时,需将仿真器端的TDIS引脚接到底板的数字地,否则仿真器将无法识别到设备。

- 由于JTAG接口未将EMU0/EMU1引脚引出至底板,EMU0/EMU1引脚已经在核心板上用控制LED1/LED2,因此此设计暂不支持EMU0/EMU1功能测试。

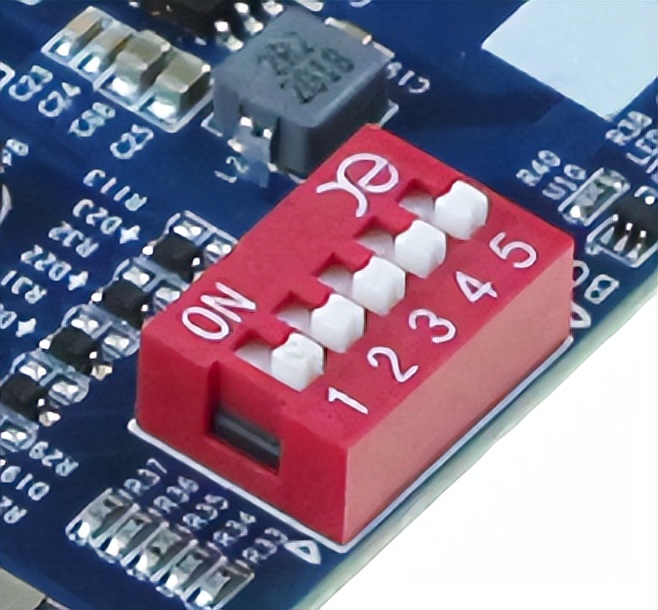

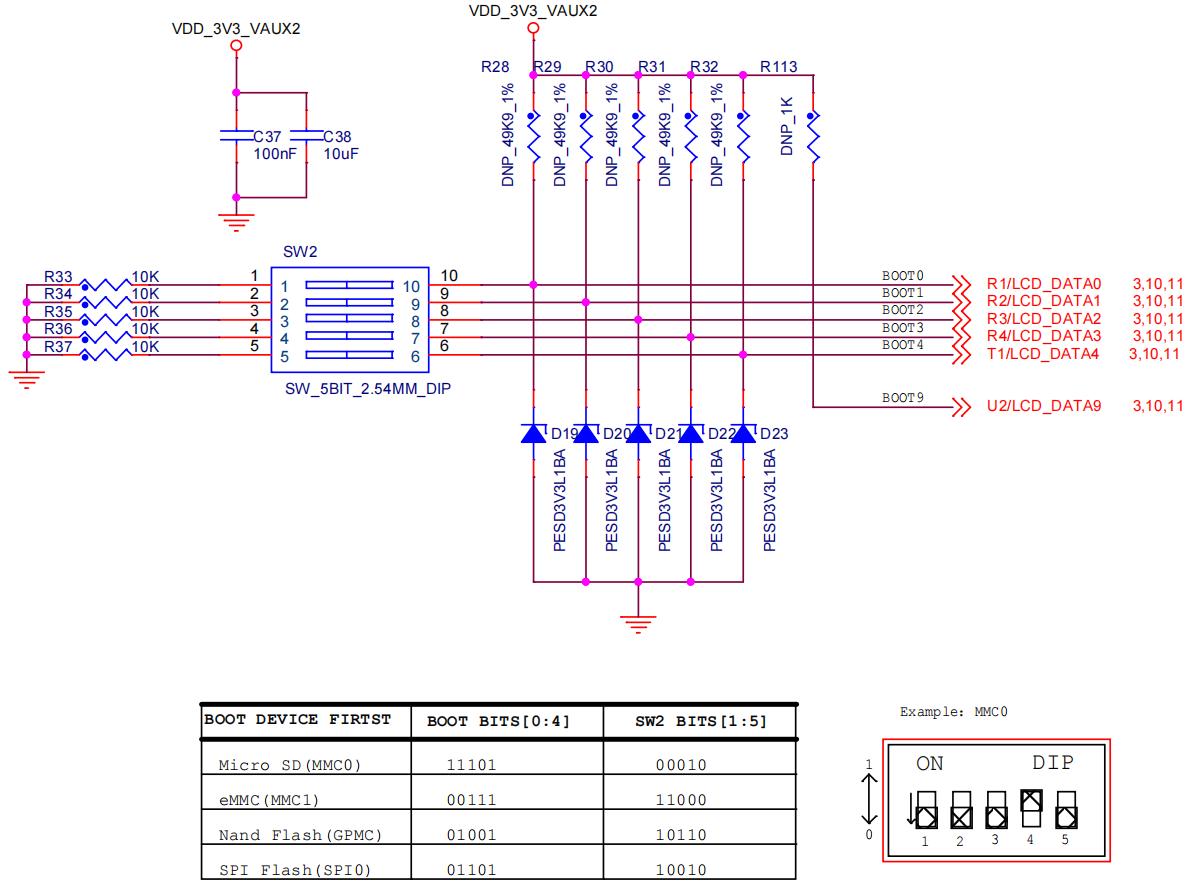

BOOT SET启动选择拨码开关SW2为5bit启动方式选择拨码开关。常用启动模式有如下两种,启动选择拨码开关的ON为1,相反为0。

- Micro SD卡启动模式:00010(1~5)

- eMMC启动模式:11000(1~5)

- NAND FLASH启动模式:10110(1~5)

- SPI FLASH启动模式:10010(1~5)

图 14

图 15

设计注意事项:

- SYSBOOT[4:0]和SYSBOOT9引脚在评估底板通过BOOT SET启动选择拨码开关或上下拉电阻进行启动模式选择。

- SYSBOOT[15:0]引脚请使用核心板输出的VDD_3V3_VAUX2。VDD_3V3_VAUX2为专用于BOOT SET配置的电源,请勿用于其他负载供电。

- 由于SYSBOOT引脚与LCDC总线存在复用关系,若使用LCDC总线外接设备或其他复用功能时,请确保AM335x在上电初始化过程中SYSBOOT引脚电平不受外接设备的影响,否则将会导致AM335x无法正常启动。可使用Buffer(SN74LV244A)实现AM335x在上电初始化中,隔离外接设备对SYSBOOT的影响。