二、中断和异常

二、中断和异常

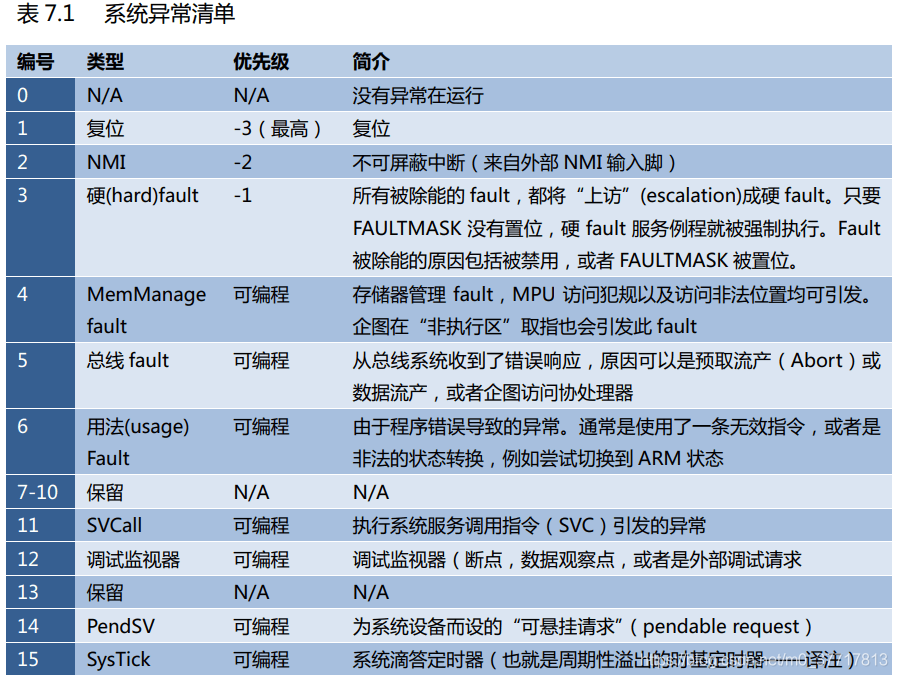

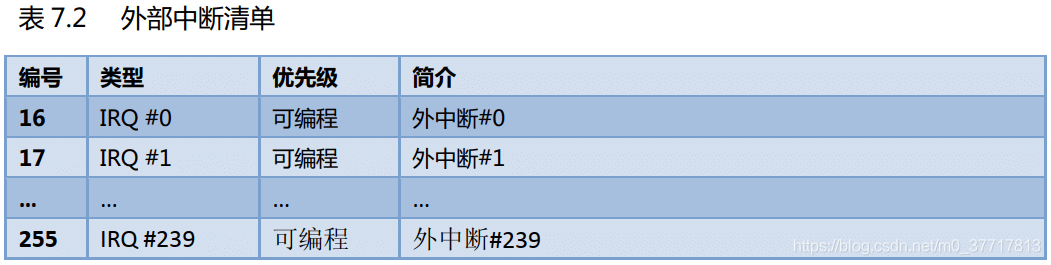

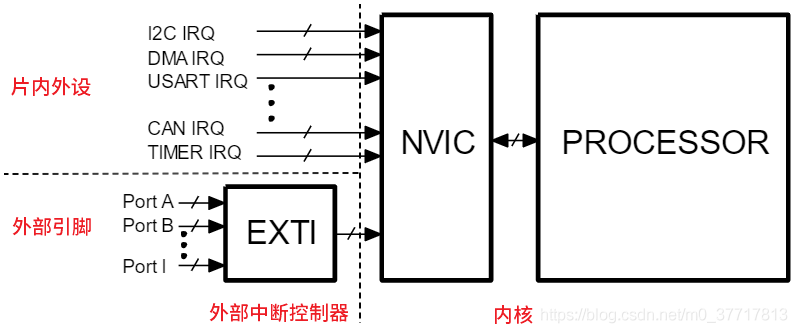

CM3 内核描述中的外部中断均是相对于内核而言的,比如串口中断、定时器中断等等都是(内核的)外部中断!而这里提到的STM32的外部中断(EXTI)指的是芯片的外部中断,主要是由芯片外部事件触发的中断,不是内核的外部中断!所以当阅读 STM32 参考手册时,外部中断(EXTI)指的均是芯片外部(IO引脚)事件触发的中断。而当阅读网络文章时,则要注意区分。为了避免混淆,都会加 (EXTI) 以区分。

STM32的外部中断(EXTI)属于内核的外部中断一部分。在STM32手册中外部中断(EXIT)均是指芯片的外部中断加粗样式,也就是上表中的 EXIT0-9。

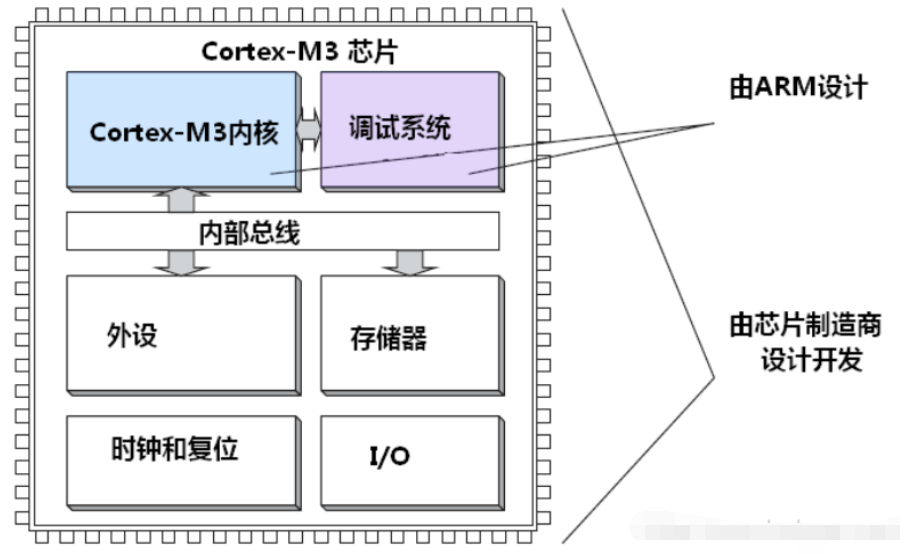

这里的 内外部 就是物理空间的内外部。

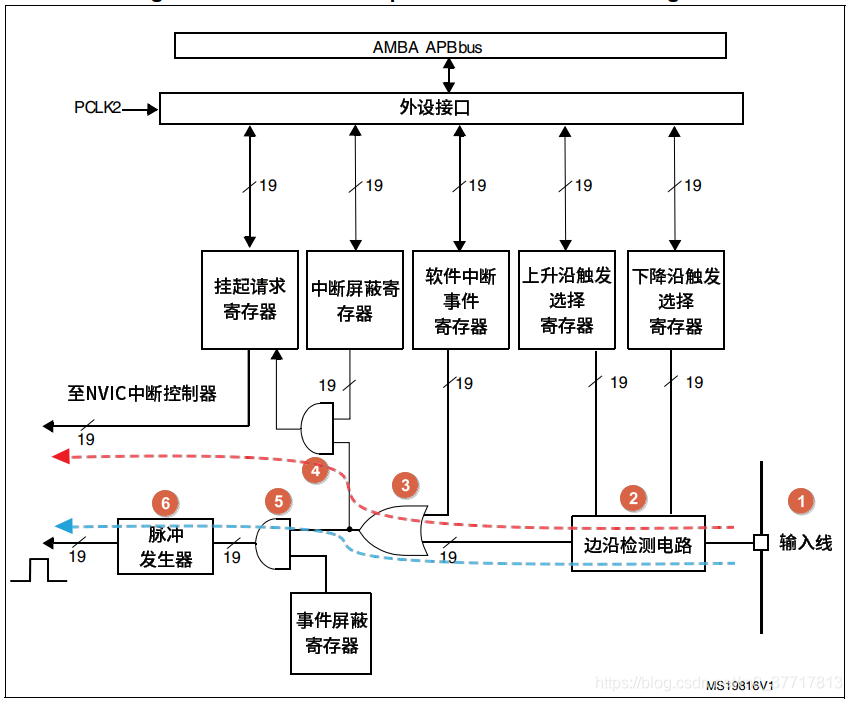

这张图的在 STM32中文手册 中是错误的,英文版的是对的。因而网上很多文章此处的配图都有误,我这里重置了。

例子:接下来详细说明 EXIT 执行过程。

比方STM32的GPIO口的电平跳变是可能触发外部中断(EXIT)的。但在具体配置时,可以根据需要来决定启用还是禁用相关脚的中断功能,从而选择不同的事件触发方式,即:外部事件模式和外部中断模式。如果不希望电平跳变事件触发中断,就配置为事件模式,反之,配置为中断模式

我们可以通过程序控制此处的软件中断事件寄存器,人为的通过或门(编号 ③)输入一个外部事件,从而不需要真实的外部输入,就能产生一个可能触发中断的事件,相当与模拟该中断线上的事件。

诸如ADC、串口、定时器之类产生的中断,就叫 名称+中断,如:定时器中断、串口中断、ADC中断。并不属于这里的软件中断范畴,STM32手册中唯一提到软件中断这个词的就是指这个寄存器,不要混淆了。或门的输出接到了两个与门(编号 ④、⑤)上,一方面与中断屏蔽寄存器求与编号(④)触发中断, 另一方面与事件屏蔽寄存器求与(⑤)触发事件。 中断屏蔽寄存器控制了相应的中断是否开启了,如果开启了中断将会产生一个中断触发信号,置位中断请求寄存器, 同时将中断触发信号提交给中断控制器(NVIC)。 同样的道理,事件屏蔽寄存器控制事件是否开启,如果开启则直接产生一个脉冲通知后继的功能模块处理事件,例如通知DMA读写内存等。

简单举例: 外部I/O触发AD转换,来测量外部物品的重量;相比之下,后者不要软件参与启动AD转换,并且响应速度也更块;要是再使用事件触发DMA操作,就完全不用软件参与(AD转换后操作)就可以完成某些联动任务了。

- 如果使用传统的中断通道,需要I/O触发产生外部中断(EXIT),外部中断(EXIT)服务程序启动AD转换,AD转换完成中断服务程序提交最后结果;

- 要是使用事件通道,I/O触发产生事件,然后联动触发AD转换,AD转换完成中断服务程序提交最后结果;

举报

举报

更多回帖