CC2530 I/O 端口具备如下重要特性:

- 21 个数字 I/O 引脚

- 可以配置为通用 I/O 或外部设备 I/O

- 输入口具备上拉或下拉能力

- 具有外部中断能力

通用I/O配置

寄存器介绍

- 寄存器 PxSEL,其中 x 为端口的标号 0~2,用来设置端口的每个引脚为通用 I/O(设置为0) 或者是外部设备 I/O 信号(设置为1)。作为缺省的情况,每当复位之后,所有的数字输入/输出引脚都设置为通用输入引脚

- 寄存器 PxDIR 来设置每个端口引脚为输入或输出。因此只要设置 PxDIR 中的指定位为 1,其对应的引脚口就被设置为输出了

- 通用 I/O 端口引脚可以设置为上拉、下拉(0表示)或三态(1表示)操作模式。作为缺省的情况,复位之后,所有的端口均设置为带上拉的输入。要取消输入的上拉或下拉功能,就要将 PxINP 中的对应位设置为 1。 I/O 端口引脚 P1.0 和 P1.1 没有上拉/下拉功能。注意配置为外设 I/O 信号的引脚没有上拉/下拉功能,即使外设功能是一个输入

P2INP高3位决定在配置为上下拉模式的时候,组为上拉还是下拉。P2INP第7位对应P2组 第6位对应P1组 第5位对应P0组 0表示上拉 1表示下拉

Example:

设置P1_0输出低电平

P1SEL &=0xFE; //1111 1110 设置为通用I/OP1DIR |= 0x01; //设置引脚为输出P1_0 = 0; //输出低电平 设置P0_6为输入上拉

P0SEL &=0xBF; //1011 1111 设置为通用I/OP0DIR &=0xBF; //1011 1111 设置引脚为输出P0INP &=0xBF; //让P0_6配置为上下拉模式P2INP &=0xDF; //1101 1111让P0组处于上拉模式 通用 I/O 中断

通用 I/O 引脚设置为输入后,可以用于产生中断。中断可以设置在外部信号的上升或下降沿触发。 P0、 P1或 P2 端口都有中断使能位,对位于 IEN1-2 寄存器内的端口所有的位都是公共的,如下:

IEN1.P0IE: P0组中断使能

IEN2.P1IE: P1组中断使能

IEN2.P2IE: P2组中断使能

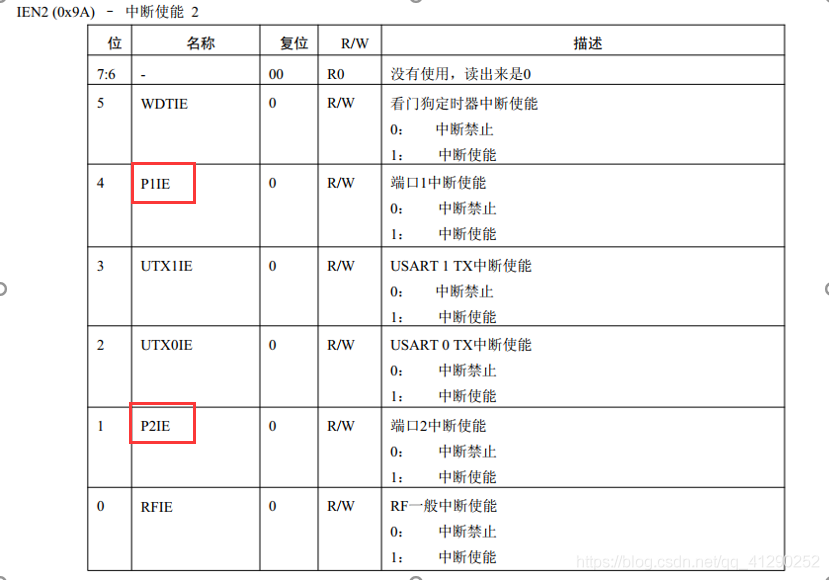

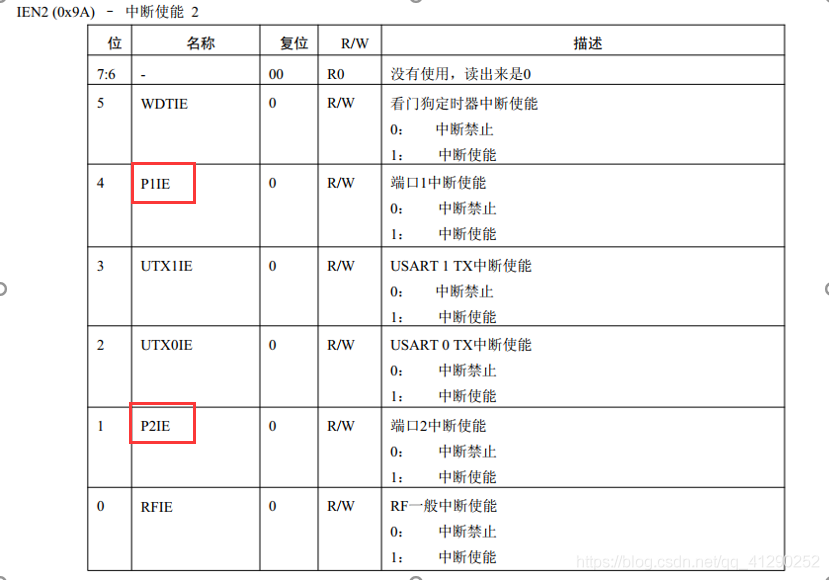

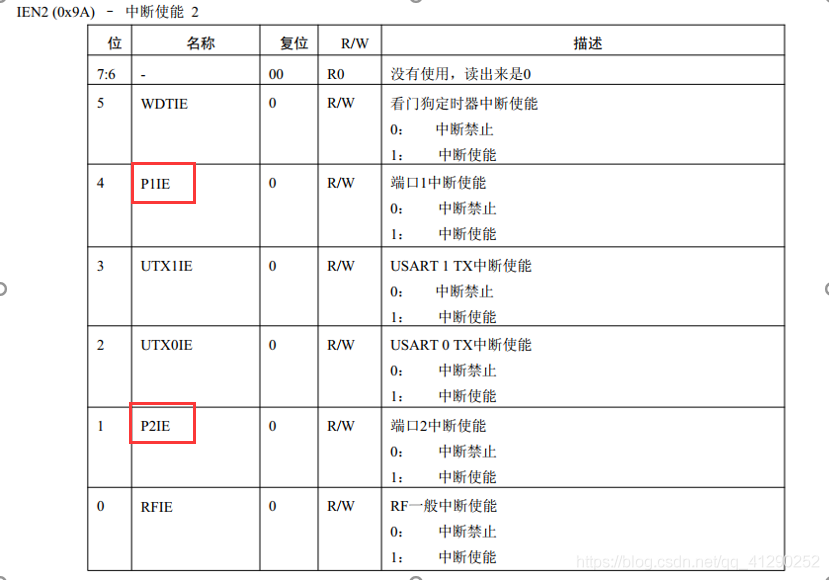

IEN2寄存器(不可位寻址)

除了这些公共中断使能之外, 每个端口的位都有位于 SFR 寄存器 P0IEN、 P1IEN 和 P2IEN的单独的中断使能。即使配置为外设 I/O 或通用输出的 I/O 引脚使能时都有中断产生,当中断条件发生在 I/O 引脚之一上面, P0-P2 中断标志寄存器 P0IFG、 P1IFG 或 P2IFG 中相应的中断状态标志将设置为 1。不管引脚是否设置了它的中断使能位,中断状态标志都被设置。当中断已经执行,中断状态标志被清除,该标志写入 0。 这个标志必须在清除 CPU 端口中断标志(PxIF)之前被清除

寄存器总结如下:

除了这些公共中断使能之外, 每个端口的位都有位于 SFR 寄存器 P0IEN、 P1IEN 和 P2IEN的单独的中断使能。即使配置为外设 I/O 或通用输出的 I/O 引脚使能时都有中断产生,当中断条件发生在 I/O 引脚之一上面, P0-P2 中断标志寄存器 P0IFG、 P1IFG 或 P2IFG 中相应的中断状态标志将设置为 1。不管引脚是否设置了它的中断使能位,中断状态标志都被设置。当中断已经执行,中断状态标志被清除,该标志写入 0。 这个标志必须在清除 CPU 端口中断标志(PxIF)之前被清除

寄存器总结如下:

- P0IEN: P0 中断使能

- P1IEN: P1 中断使能

- P2IEN: P2 中断使能

- P0FG: P0 中断标志

- P1IFG: P1 中断标志

- P2IFG: P2 中断标志

- PICTL: P0、 P1 和 P2 触发沿设置

Example

外部中断配置过程

- 初始化IO口工作在普通IO,上拉输入状态

- 首先开组内对应的具体某IO口中断

- 开IO口组中断

- 开组内对应的具体某IO口中断

- 上升沿还是下降沿触发

- 开CPU总中断EA = 1

配置P0_5的外部中断

P0SEL &=0xDF;

P0DIR &=0xDF;

P0INP &=0xDF;

P2INP &=0xDF; // 初始化IO口工作在普通IO,上拉输入状态

P0IEN |= 0x20;// 开组内对应的具体某IO口中断

P0IE = 1; //开P0口组中断(P1、P2组P1IE/P2IE)不可位寻址

//开P1组中断应 IEN2 |=0x20;

PICTL |= 0x01; //把PO一组配置成下降沿触发

EA = 1; //开CPU总中断

中断函数

#pragma vector = P0INT_VECTOR

__interrupt void fn()

{

if(P0IFG & 0x20)//判断是否P0_5触发中断

{

}

P0IFG = 0;

P0IF = 0;//清除中断

}

CC2530 I/O 端口具备如下重要特性:

- 21 个数字 I/O 引脚

- 可以配置为通用 I/O 或外部设备 I/O

- 输入口具备上拉或下拉能力

- 具有外部中断能力

通用I/O配置

寄存器介绍

- 寄存器 PxSEL,其中 x 为端口的标号 0~2,用来设置端口的每个引脚为通用 I/O(设置为0) 或者是外部设备 I/O 信号(设置为1)。作为缺省的情况,每当复位之后,所有的数字输入/输出引脚都设置为通用输入引脚

- 寄存器 PxDIR 来设置每个端口引脚为输入或输出。因此只要设置 PxDIR 中的指定位为 1,其对应的引脚口就被设置为输出了

- 通用 I/O 端口引脚可以设置为上拉、下拉(0表示)或三态(1表示)操作模式。作为缺省的情况,复位之后,所有的端口均设置为带上拉的输入。要取消输入的上拉或下拉功能,就要将 PxINP 中的对应位设置为 1。 I/O 端口引脚 P1.0 和 P1.1 没有上拉/下拉功能。注意配置为外设 I/O 信号的引脚没有上拉/下拉功能,即使外设功能是一个输入

P2INP高3位决定在配置为上下拉模式的时候,组为上拉还是下拉。P2INP第7位对应P2组 第6位对应P1组 第5位对应P0组 0表示上拉 1表示下拉

Example:

设置P1_0输出低电平

P1SEL &=0xFE; //1111 1110 设置为通用I/OP1DIR |= 0x01; //设置引脚为输出P1_0 = 0; //输出低电平 设置P0_6为输入上拉

P0SEL &=0xBF; //1011 1111 设置为通用I/OP0DIR &=0xBF; //1011 1111 设置引脚为输出P0INP &=0xBF; //让P0_6配置为上下拉模式P2INP &=0xDF; //1101 1111让P0组处于上拉模式 通用 I/O 中断

通用 I/O 引脚设置为输入后,可以用于产生中断。中断可以设置在外部信号的上升或下降沿触发。 P0、 P1或 P2 端口都有中断使能位,对位于 IEN1-2 寄存器内的端口所有的位都是公共的,如下:

IEN1.P0IE: P0组中断使能

IEN2.P1IE: P1组中断使能

IEN2.P2IE: P2组中断使能

IEN2寄存器(不可位寻址)

除了这些公共中断使能之外, 每个端口的位都有位于 SFR 寄存器 P0IEN、 P1IEN 和 P2IEN的单独的中断使能。即使配置为外设 I/O 或通用输出的 I/O 引脚使能时都有中断产生,当中断条件发生在 I/O 引脚之一上面, P0-P2 中断标志寄存器 P0IFG、 P1IFG 或 P2IFG 中相应的中断状态标志将设置为 1。不管引脚是否设置了它的中断使能位,中断状态标志都被设置。当中断已经执行,中断状态标志被清除,该标志写入 0。 这个标志必须在清除 CPU 端口中断标志(PxIF)之前被清除

寄存器总结如下:

除了这些公共中断使能之外, 每个端口的位都有位于 SFR 寄存器 P0IEN、 P1IEN 和 P2IEN的单独的中断使能。即使配置为外设 I/O 或通用输出的 I/O 引脚使能时都有中断产生,当中断条件发生在 I/O 引脚之一上面, P0-P2 中断标志寄存器 P0IFG、 P1IFG 或 P2IFG 中相应的中断状态标志将设置为 1。不管引脚是否设置了它的中断使能位,中断状态标志都被设置。当中断已经执行,中断状态标志被清除,该标志写入 0。 这个标志必须在清除 CPU 端口中断标志(PxIF)之前被清除

寄存器总结如下:

- P0IEN: P0 中断使能

- P1IEN: P1 中断使能

- P2IEN: P2 中断使能

- P0FG: P0 中断标志

- P1IFG: P1 中断标志

- P2IFG: P2 中断标志

- PICTL: P0、 P1 和 P2 触发沿设置

Example

外部中断配置过程

- 初始化IO口工作在普通IO,上拉输入状态

- 首先开组内对应的具体某IO口中断

- 开IO口组中断

- 开组内对应的具体某IO口中断

- 上升沿还是下降沿触发

- 开CPU总中断EA = 1

配置P0_5的外部中断

P0SEL &=0xDF;

P0DIR &=0xDF;

P0INP &=0xDF;

P2INP &=0xDF; // 初始化IO口工作在普通IO,上拉输入状态

P0IEN |= 0x20;// 开组内对应的具体某IO口中断

P0IE = 1; //开P0口组中断(P1、P2组P1IE/P2IE)不可位寻址

//开P1组中断应 IEN2 |=0x20;

PICTL |= 0x01; //把PO一组配置成下降沿触发

EA = 1; //开CPU总中断

中断函数

#pragma vector = P0INT_VECTOR

__interrupt void fn()

{

if(P0IFG & 0x20)//判断是否P0_5触发中断

{

}

P0IFG = 0;

P0IF = 0;//清除中断

}

举报

举报

举报

举报