一概述

首先介绍一下什么是肉电路:

个人理解:画好的PCB板子,焊接完成以后,会出现莫名其妙的问题,譬如:当你在调试的时候,手指触碰了一个IC,会出现信号不稳,或者系统会重启之类的问题,很大的可能是因为信号不完整造成的。

那怎么样解决呢?你可以在信号线上上拉电阻或者下拉电阻或者信号线直接串电阻,具体的怎么做,那一定要先分析电路。

但是如果是芯片系统复位呢?,那么还是要分析电路,是因为电源干扰?还是因为没共地?还是因为寄生电容、寄生电感等相互干扰?

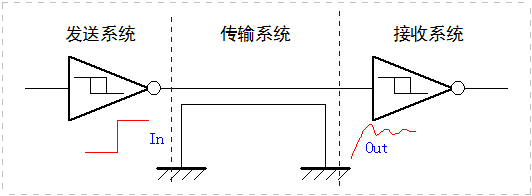

二 电路是波与场之间的变化

大多数信号都是从发射端进行传递到接收端,但是在这过程中必然伴随着电磁场的建立和扩散,当这时候,你用手触摸信号线,实际上会改变接口电路的阻抗,在一定的条件下与电路传输发生了阻抗匹配,这时候就减小信号的失真,那么,怎么解决呢?先分析电路,

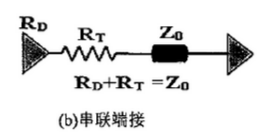

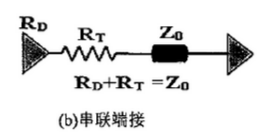

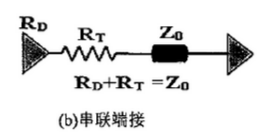

串联端接方式

靠近输出端的位置串联一个电阻,要达到匹配效果,串联电阻和驱动端输出阻抗的总和应等于传输线的特征阻抗Z0。

在通常的数字信号系统中,器件的输出阻抗通常是十几欧姆到二十几欧姆,传输线的阻抗通常会控制在50欧姆,所以始端匹配电阻常见为33欧姆电阻。

当然要达到好的匹配效果,驱动端输出到串联电阻这一段的传输路径最好较短,短到可以忽略这一段传输线的影响。

串联电阻优缺点如下:

(1)优点

1、只需要一个电阻;

2、没有多余的直流功耗;

3、消除驱动端的二次反射;

4、不受接收端负载变化的影响;

(2)缺点

1、接收端的一次发射依然存在;

2、信号边沿会有一些变化;

3、电阻要靠近驱动端放置,不适合双向 传输信号;

4、在线上传输的电压是驱动电压的一半,不适合菊花链的多型负载结构。

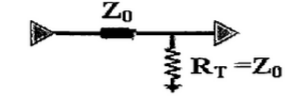

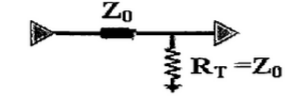

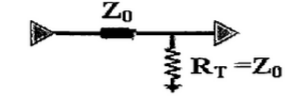

二、并联端接方式

并联端接又叫终端匹配,要达到阻抗匹配的要求,端接的电阻应该和传输线的特征阻抗Z0相等。

在通常的数字信号传输系统里,接收端的阻抗范围为几兆到十几兆,终端匹配电阻如果和传输线的特征阻抗相等,其和接收端阻抗并联后的阻抗大致还是在传输线的特征阻抗左右,那么终端的反射系数为0。不会产生反射,消除的是终端的一次反射。

并联端接优缺点

(1)优点

1、适用于多个负载

2、只需要一个电阻并且阻值容易选取

(2)缺点

1、增加了直流功耗

2、并联端接可以上拉到电源或者下拉到地,是的低电平升高或者高电平降低,减小噪声容限。

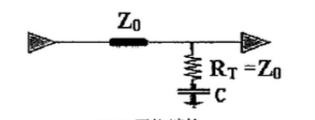

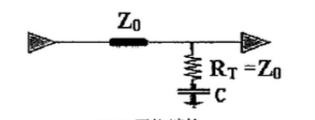

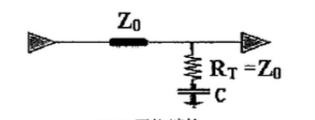

三、AC并联端接

并联端接为消除直流功耗,可以采用如下所示的AC并联端接(AC终端匹配)。要达到匹配要求,端接的电阻应该和传输线的特征阻抗Z0相等。

优缺点描述如下:

(1)优点

1、适用于多个负载

2、无直流功耗增加

(2)缺点

1、需要两个器件

2、增加了终端的容性负载,增加了RC电路造成的延时

3、对周期性的信号有效(如时钟),不适合于非周期信号(如数据)

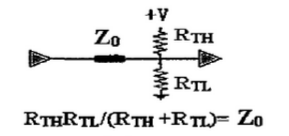

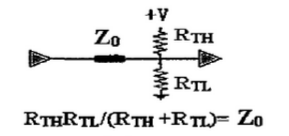

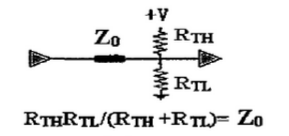

四、戴维南端接

戴维南端接同终端匹配,如下图,要达到匹配要求,终端的电阻并联值要和传输线的特征阻抗Z0相等。

优缺点描述:

(1)优点

1、适用于多个负载

2、很适用于SSTL/HSTL电平上拉或下拉输出阻抗很好平衡的情况。

(2)缺点

1、直流功耗增加

2、需要两个器件

3、端接电阻上拉到电源或下拉到地,会使得低电平升高或高电平降低

4、电阻值较难选择,电阻值取值小会使低电平升高,高电平降低更加恶劣;电阻值取大有可能造成不能完全匹配,使反射增大,可以通过仿真来确定

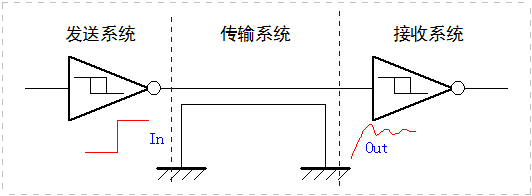

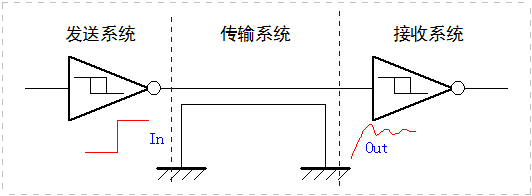

三 电路是信号与系统

电路是由各个元器件相互连接而形成的复杂电子系统,无论是信号源,还是接收源,还是连接线都是一个独立的系统,他们各自都有传输的特性,包括输入输出线是否有线性、具有多大的频率带宽等。在实际系统中都是具有限带宽的失真系统

电压、电流信号在经过引线(传输系统)传递的时候,会由传输系统的带宽、频率响应等特性而发生改变。其中最主要的是原来信号中的不同频率分量会受到传输系统频率特性的影响而得到不同的放大和衰减。

使用手触碰电路端口,改变了传输线系统的频率响应。原本可能会出现的谐振点有可能会被手指的阻抗进行阻尼掉,进而减小波形的振荡和失真。

四 言归正传

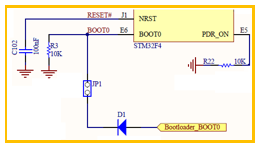

本文章是针对STM32F4 IC芯片的做的铺垫,这是一个很小的,很不细心的设计,那就是F4的LQFP 144引脚的143引脚PDR_ON

如果这个引脚悬空状态,那么你用手触摸芯片,用示波器测量RESET引脚,引脚会被拉低,亲测!

有些STM32产品能够使能/失能内部电源监视器,通过PDR_ON引脚电平进行控制实现。PDR_ON引脚电平为低时,内部电源监视器关闭;当PDR_ON引脚电平为高时,内部电源监视器使能。

内部电源监视器影响的功能包括:POR(上电复位)、PDR(掉电复位)、BOR(欠压复位)、PVD(可编程电位检测)、VBAT功能。其中,VBAT功能包括:维持后备寄存器/存储器,为RTC、LSE振荡器提供后备供电和维持其在掉电时工作。

在使用低电压电源的低功耗应用中,当VDD低至最低供电电压附近时,PDR_ON管脚需要进行合理配置。一般当VDD在1.7V~1.9V之间时【不同系列可能略有差异,以手册中VDD范围为准】,可以考虑通过拉低PDR_ON管脚关闭内部电源监视器。当PDR_ON拉低时,内部电源管理器被关闭,POR和PDR功能停止工作,这样可以避免由于供电在POR/PDR阈值附近的电压波动而引起频繁的POR/PDR复位。当然,如果VDD一定不低于1.8V,则可将PDR_ON置高,不必关闭内部电源管理器。

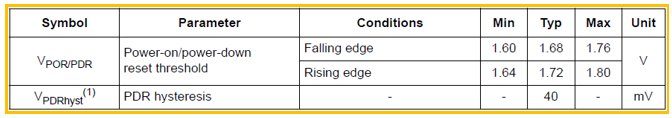

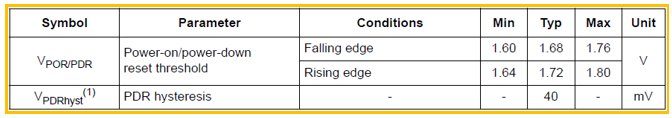

如下电气参数表,摘自

DS11189(STM32F469xx)。当VDD较低时,在VDD纹波下,可能出现满足POR/PDR的触发条件。 例如1.8V供电,纹波在60mV,则VDD供电在1.74~1.86V之间波动,反复出现POR/PDR,这种情况就一定要考虑PDR_ON功能,将其下拉,关闭内部电源管理器。

PDR_ON拉低时,内部电源管理器失能,需要添加外部电源管理器。具体实现电路可参考AN4488。

注:仅在具有PDR_ON引脚封装的STM32产品才能关闭电源监视器。没有PDR_ON功能的STM32,默认使用内部电源监视器工作。

异常现象描述

客户应用中,采用的电源为1.86V左右。根据上述分析,客户考虑到VDD波动低至1.8V(更准确来说,对应PDR域的最大值1.76V)的情况。将PDR_ON引脚下拉,关闭了内部电源管理器。

在压力测试环节,发现设备快速掉电重启时,MCU工作异常。异常后,即使通过热重启,MCU无法恢复工作,只能通过冷重启使其恢复。 如果设备掉电重启间隔时间长,则不存在这种问题。

原因分析

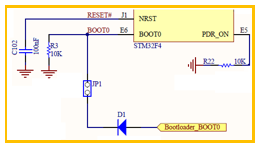

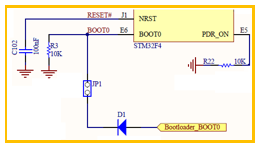

在展开分析时,先看一下采用电路的示意图,如下。

其中,PDR_ON采用下拉形式,根据上面介绍,内部电源管理器失能(内部的POR/PDR功能关闭)。

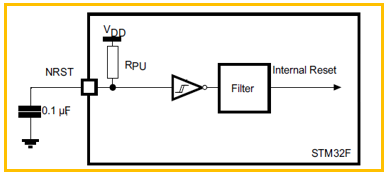

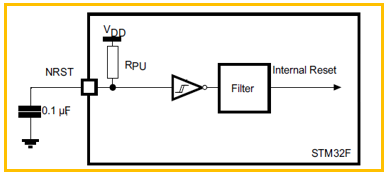

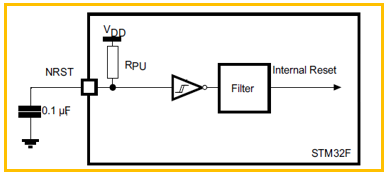

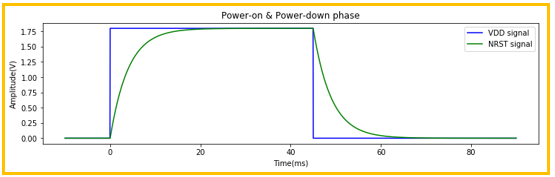

上图为NRST部分电路示意图,外部NRST引脚外接了100nF电容,与内部上拉电阻组成阻容电路,上电和下电时VDD和NRST信号如下图所示。在上电过程中,VDD有效时,NRST依然处于使能状态(低电位),起到了上电复位效果。但是能够看出,这种电路实现不会达到快速掉电复位效果。

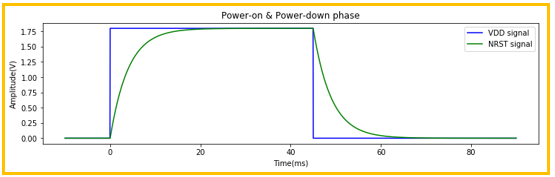

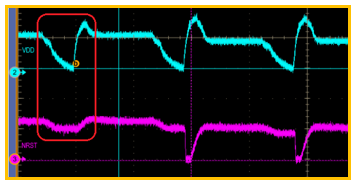

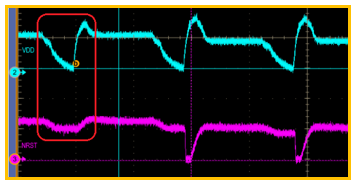

应用中存在掉电重启间隔非常短的情况。同时,由于VDD耦合电容的存在,VDD掉电同样是一个放电过程,存在如下波形图。

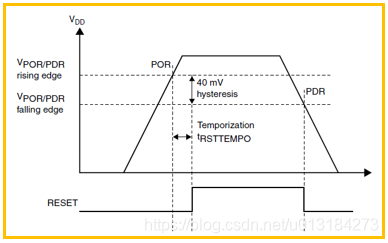

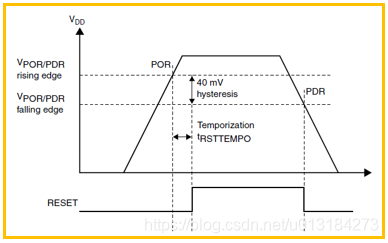

图中红框内,VDD电压已经下降到远低于MCU的正常供电范围(1.7~3.6V)。但是由于缺乏PDR,尽管NRST也在下降,但总体仍然处于非激活状态(高电位)。这会导致MCU运行在非正常供电下,甚至是VDD很低的情况下工作,而这种情况在产品的数据表中明确表示,运行在工作范围外,MCU无法正常工作。而红色部分,就是由于MCU工作已经异常,所以在再次上电时,MCU已经无法正常工作, tRSTTEMPO部分也无法正常生效(tRSTTEMPO对应部分如下图介绍)。

掉电重启间隔时间长,VDD放电充分,即使MCU工作异常,在充分掉电后,MCU也完全停止工作。再次上电时,则不会受到影响。

根据分析,异常出现的原因:在低电压供电需求下,关闭内部电源管理器时,并没有在外部增加电源管理单元实现类似功能。使MCU在极低供电电压下依然工作,引发MCU工作异常。

注:经过实测,STM32F469内部电源管理器的关闭,并不影响上图中tRSTTEMPO部分的功能。

总结及建议

MCU电源电路相对简单。但是在实际开发中,建议完全参考数据手册和《Getting started with xxxx MCU hardware development》中电源部分设计,避免由于对ST MCU不熟悉引发的硬件设计问题。

一概述

首先介绍一下什么是肉电路:

个人理解:画好的PCB板子,焊接完成以后,会出现莫名其妙的问题,譬如:当你在调试的时候,手指触碰了一个IC,会出现信号不稳,或者系统会重启之类的问题,很大的可能是因为信号不完整造成的。

那怎么样解决呢?你可以在信号线上上拉电阻或者下拉电阻或者信号线直接串电阻,具体的怎么做,那一定要先分析电路。

但是如果是芯片系统复位呢?,那么还是要分析电路,是因为电源干扰?还是因为没共地?还是因为寄生电容、寄生电感等相互干扰?

二 电路是波与场之间的变化

大多数信号都是从发射端进行传递到接收端,但是在这过程中必然伴随着电磁场的建立和扩散,当这时候,你用手触摸信号线,实际上会改变接口电路的阻抗,在一定的条件下与电路传输发生了阻抗匹配,这时候就减小信号的失真,那么,怎么解决呢?先分析电路,

串联端接方式

靠近输出端的位置串联一个电阻,要达到匹配效果,串联电阻和驱动端输出阻抗的总和应等于传输线的特征阻抗Z0。

在通常的数字信号系统中,器件的输出阻抗通常是十几欧姆到二十几欧姆,传输线的阻抗通常会控制在50欧姆,所以始端匹配电阻常见为33欧姆电阻。

当然要达到好的匹配效果,驱动端输出到串联电阻这一段的传输路径最好较短,短到可以忽略这一段传输线的影响。

串联电阻优缺点如下:

(1)优点

1、只需要一个电阻;

2、没有多余的直流功耗;

3、消除驱动端的二次反射;

4、不受接收端负载变化的影响;

(2)缺点

1、接收端的一次发射依然存在;

2、信号边沿会有一些变化;

3、电阻要靠近驱动端放置,不适合双向 传输信号;

4、在线上传输的电压是驱动电压的一半,不适合菊花链的多型负载结构。

二、并联端接方式

并联端接又叫终端匹配,要达到阻抗匹配的要求,端接的电阻应该和传输线的特征阻抗Z0相等。

在通常的数字信号传输系统里,接收端的阻抗范围为几兆到十几兆,终端匹配电阻如果和传输线的特征阻抗相等,其和接收端阻抗并联后的阻抗大致还是在传输线的特征阻抗左右,那么终端的反射系数为0。不会产生反射,消除的是终端的一次反射。

并联端接优缺点

(1)优点

1、适用于多个负载

2、只需要一个电阻并且阻值容易选取

(2)缺点

1、增加了直流功耗

2、并联端接可以上拉到电源或者下拉到地,是的低电平升高或者高电平降低,减小噪声容限。

三、AC并联端接

并联端接为消除直流功耗,可以采用如下所示的AC并联端接(AC终端匹配)。要达到匹配要求,端接的电阻应该和传输线的特征阻抗Z0相等。

优缺点描述如下:

(1)优点

1、适用于多个负载

2、无直流功耗增加

(2)缺点

1、需要两个器件

2、增加了终端的容性负载,增加了RC电路造成的延时

3、对周期性的信号有效(如时钟),不适合于非周期信号(如数据)

四、戴维南端接

戴维南端接同终端匹配,如下图,要达到匹配要求,终端的电阻并联值要和传输线的特征阻抗Z0相等。

优缺点描述:

(1)优点

1、适用于多个负载

2、很适用于SSTL/HSTL电平上拉或下拉输出阻抗很好平衡的情况。

(2)缺点

1、直流功耗增加

2、需要两个器件

3、端接电阻上拉到电源或下拉到地,会使得低电平升高或高电平降低

4、电阻值较难选择,电阻值取值小会使低电平升高,高电平降低更加恶劣;电阻值取大有可能造成不能完全匹配,使反射增大,可以通过仿真来确定

三 电路是信号与系统

电路是由各个元器件相互连接而形成的复杂电子系统,无论是信号源,还是接收源,还是连接线都是一个独立的系统,他们各自都有传输的特性,包括输入输出线是否有线性、具有多大的频率带宽等。在实际系统中都是具有限带宽的失真系统

电压、电流信号在经过引线(传输系统)传递的时候,会由传输系统的带宽、频率响应等特性而发生改变。其中最主要的是原来信号中的不同频率分量会受到传输系统频率特性的影响而得到不同的放大和衰减。

使用手触碰电路端口,改变了传输线系统的频率响应。原本可能会出现的谐振点有可能会被手指的阻抗进行阻尼掉,进而减小波形的振荡和失真。

四 言归正传

本文章是针对STM32F4 IC芯片的做的铺垫,这是一个很小的,很不细心的设计,那就是F4的LQFP 144引脚的143引脚PDR_ON

如果这个引脚悬空状态,那么你用手触摸芯片,用示波器测量RESET引脚,引脚会被拉低,亲测!

有些STM32产品能够使能/失能内部电源监视器,通过PDR_ON引脚电平进行控制实现。PDR_ON引脚电平为低时,内部电源监视器关闭;当PDR_ON引脚电平为高时,内部电源监视器使能。

内部电源监视器影响的功能包括:POR(上电复位)、PDR(掉电复位)、BOR(欠压复位)、PVD(可编程电位检测)、VBAT功能。其中,VBAT功能包括:维持后备寄存器/存储器,为RTC、LSE振荡器提供后备供电和维持其在掉电时工作。

在使用低电压电源的低功耗应用中,当VDD低至最低供电电压附近时,PDR_ON管脚需要进行合理配置。一般当VDD在1.7V~1.9V之间时【不同系列可能略有差异,以手册中VDD范围为准】,可以考虑通过拉低PDR_ON管脚关闭内部电源监视器。当PDR_ON拉低时,内部电源管理器被关闭,POR和PDR功能停止工作,这样可以避免由于供电在POR/PDR阈值附近的电压波动而引起频繁的POR/PDR复位。当然,如果VDD一定不低于1.8V,则可将PDR_ON置高,不必关闭内部电源管理器。

如下电气参数表,摘自

DS11189(STM32F469xx)。当VDD较低时,在VDD纹波下,可能出现满足POR/PDR的触发条件。 例如1.8V供电,纹波在60mV,则VDD供电在1.74~1.86V之间波动,反复出现POR/PDR,这种情况就一定要考虑PDR_ON功能,将其下拉,关闭内部电源管理器。

PDR_ON拉低时,内部电源管理器失能,需要添加外部电源管理器。具体实现电路可参考AN4488。

注:仅在具有PDR_ON引脚封装的STM32产品才能关闭电源监视器。没有PDR_ON功能的STM32,默认使用内部电源监视器工作。

异常现象描述

客户应用中,采用的电源为1.86V左右。根据上述分析,客户考虑到VDD波动低至1.8V(更准确来说,对应PDR域的最大值1.76V)的情况。将PDR_ON引脚下拉,关闭了内部电源管理器。

在压力测试环节,发现设备快速掉电重启时,MCU工作异常。异常后,即使通过热重启,MCU无法恢复工作,只能通过冷重启使其恢复。 如果设备掉电重启间隔时间长,则不存在这种问题。

原因分析

在展开分析时,先看一下采用电路的示意图,如下。

其中,PDR_ON采用下拉形式,根据上面介绍,内部电源管理器失能(内部的POR/PDR功能关闭)。

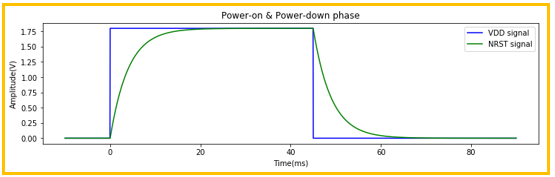

上图为NRST部分电路示意图,外部NRST引脚外接了100nF电容,与内部上拉电阻组成阻容电路,上电和下电时VDD和NRST信号如下图所示。在上电过程中,VDD有效时,NRST依然处于使能状态(低电位),起到了上电复位效果。但是能够看出,这种电路实现不会达到快速掉电复位效果。

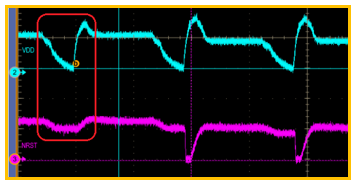

应用中存在掉电重启间隔非常短的情况。同时,由于VDD耦合电容的存在,VDD掉电同样是一个放电过程,存在如下波形图。

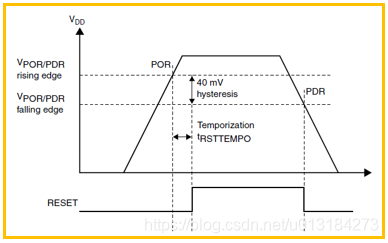

图中红框内,VDD电压已经下降到远低于MCU的正常供电范围(1.7~3.6V)。但是由于缺乏PDR,尽管NRST也在下降,但总体仍然处于非激活状态(高电位)。这会导致MCU运行在非正常供电下,甚至是VDD很低的情况下工作,而这种情况在产品的数据表中明确表示,运行在工作范围外,MCU无法正常工作。而红色部分,就是由于MCU工作已经异常,所以在再次上电时,MCU已经无法正常工作, tRSTTEMPO部分也无法正常生效(tRSTTEMPO对应部分如下图介绍)。

掉电重启间隔时间长,VDD放电充分,即使MCU工作异常,在充分掉电后,MCU也完全停止工作。再次上电时,则不会受到影响。

根据分析,异常出现的原因:在低电压供电需求下,关闭内部电源管理器时,并没有在外部增加电源管理单元实现类似功能。使MCU在极低供电电压下依然工作,引发MCU工作异常。

注:经过实测,STM32F469内部电源管理器的关闭,并不影响上图中tRSTTEMPO部分的功能。

总结及建议

MCU电源电路相对简单。但是在实际开发中,建议完全参考数据手册和《Getting started with xxxx MCU hardware development》中电源部分设计,避免由于对ST MCU不熟悉引发的硬件设计问题。

举报

举报

举报

举报