2.4控制电路

本实验中选用的控制核心是STM32系列单片机,具体型号为STM32F103R8T6。STM32F103R8T6是一款嵌入式-微控制器集成电路,是ST旗下的一款常用的增强型系列微控制器。此芯片工作电压为2.0V-3.6V,处理速度为72MHz,芯片可以存储程序的容量为256KB,存储器类型为FLASH,RAM容量为48K。芯片共有64个引脚,采用LQFP64的封装,有49个GPIO口。其中,包含16个12位ADC通道,3组USART串口。

STM32作为CPU可以适用于很多场合,比如电机驱动、游戏外设和打印机等。

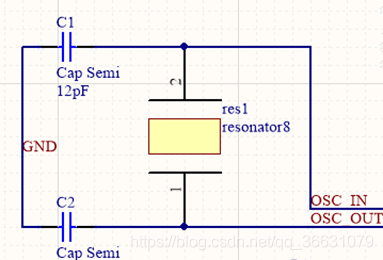

2.4.1晶振电路

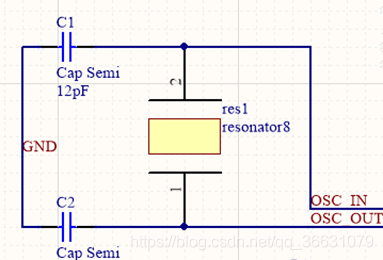

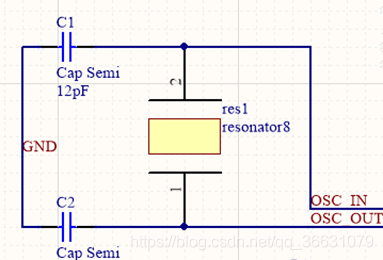

STM32系统正常工作需要时钟,没有时钟的话系统就无法稳定工作。通过阅读芯片手册我们可以得知CPU内部有两个时钟源,我们要做的就是布置好系统的外部时钟源,此次设计中我们选用的是8M赫兹的石英晶振,封装为49S直插。硬件部分电路设计如图2-7所示:

图2-7 晶振电路设计图

图2-7的晶振可以等效成一个有两个谐振点的二端网络。然后再将其接入一个反馈电路,就可以构成正弦波振荡电路。

此外,此电路的振荡频率会比较稳定,其具体原因如下:在此电路中,两个谐振频率的相当的接近,在这种情况下,就算电路网络中的其他元件参数有较大变化,晶振电路的震荡频率不会有很大的变化。

在设计晶振电路时,除了选择晶振的频率之外,最重要的就是考虑晶振的负载电容值,取选择合适的电容接在晶振的两端。只有选择了合适的电容值,才可以使得晶振按照标称频率进行振荡。外接电容的计算原理如式2-7所示:

Cf=Cd*CgCd+Cg+Cic+∆C (2-7)

其中:Cf为晶振的负载电容;

CdCg为接入晶振两脚上的电容;

Cic为集成电路内部电容;

∆C为PCB板上的电容。

此外,出于简单考虑,两脚上的外接电容也可以直接选择与负载电容值相等的电容,也可以得到标称振荡频率。目前使用较多的是12.5pf的外接电容,来构成整个的晶振电路。

在设计晶振电路时,还有以下几点需要注意:

晶振内部的石英晶体要避免碰撞,防止破损引起的晶振不起振。所以在焊接时位置尽可能靠近CPU,远离PCB板的边缘;

在焊接时应尽量将外接电容靠近晶振的电源;

在焊接时注意温度控制,防止温度过高损坏晶振;

信号线避免经过晶振下方,防止产生信号干扰;

在连接时钟信号线时,走线应该尽量短且宽。

2.4.2复位电路

在进行CPU设计的时候,复位电路也是需要我们重点关注的。复位电路设计的效果,直接影响着设计出来的整个系统在工作时的可靠性和稳定性。如果复位电路设计时出现问题,导致即使在实验室等环境下可以成功工作,在工业现场也很容易出现很多问题。

单片机在上电之后都需要复位,这样可以使得整个系统从初始状态开始工作。复位电路的主要功能就在于在系统上电或者复位的过程中,复位电路可以保证CPU处于复位状态,而不是直接进行工作。否则单片机很容易发出错误的指令,影响到我们整个系统的稳定性。

我们需要设计的是系统的手动复位电路,在查阅相关资料之后,决定采取按键复位的电路进行设计。

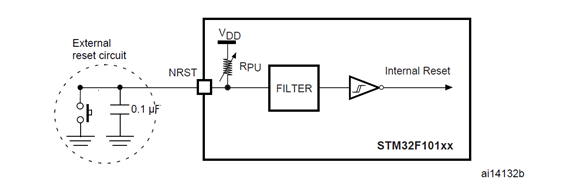

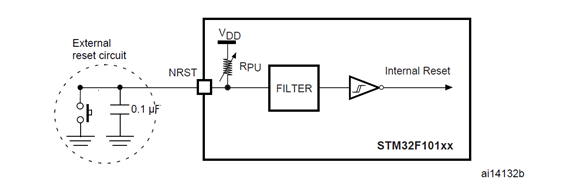

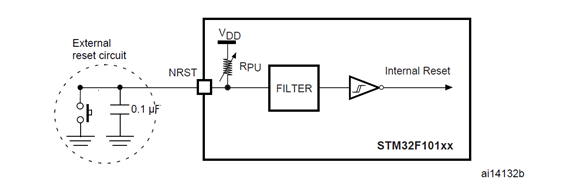

在设计本系统的复位电路之前,我们首先关注一下STM32系列CPU的复位电路原理。通过查阅芯片的数据手册我们可以看到其原理图如图2-8所示:

图2-8 STM32复位电路原理图

通过数据手册上的原理图,我们可以发现此复位电路的工作方式为:NSRT通过电阻接到VDD,并通过一个电容去接地,且外接了一个按键。在正常工作时,NRST引脚通过一个上拉电阻上拉至高电平。在需要复位时,按下按键,将NRST引脚置为低电平,再经过芯片内部的反相器,就可以使得芯片的Reset为高电平,实现芯片的复位。事实上,Reset需要保持一定时间的高电平才可以成功复位,但以人按键的时间来看是足以满足这个要求的。

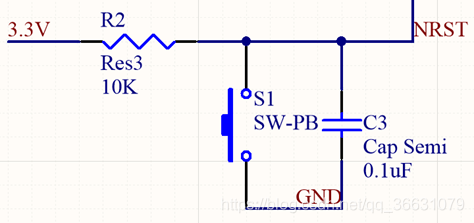

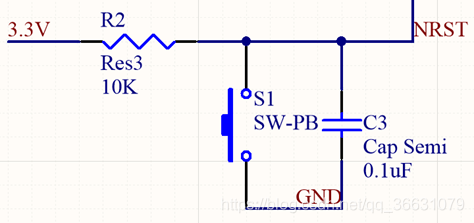

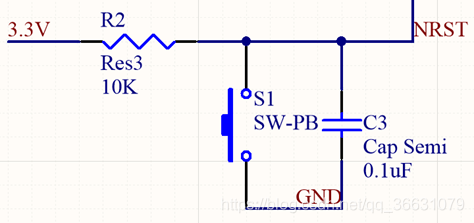

了解了芯片复位电路的原理,我们就可以来设计本系统的按键复位电路了,具体设计结果如图2-9所示:

图2-9 复位电路设计图

需要说明的是,在图2-9所示的复位电路中,我们在芯片NRST引脚外接了一个上拉电阻。事实上,我们可以从图8的原理图中得知此芯片内部是有一个上拉电阻的,所以此处的上拉电阻可以省去。不过,鉴于有些芯片的内部没有上拉电阻,需要这个外接的上拉电阻,我们可以把这个当作一个好习惯保留下来。同时,外加的上拉电阻也可以增强系统抗电磁干扰的能力。

在图2-9所示的电路中,当电路正常工作时,NRST引脚为高电平。在我们需要对系统进行复位操作时,按下按键使得NRST引脚接地,成为低电平,完成对芯片的复位操作。此电路简单实用,在我们此后的调试过程中起着很重要的作用。

2.4.3下载电路

下载电路是一个系统的基础,下载电路如果有差错,会导致程序无法下载,进而整个系统就会瘫痪。

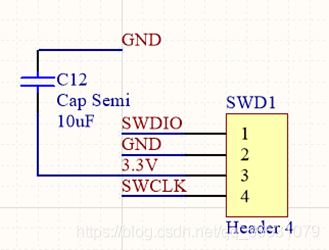

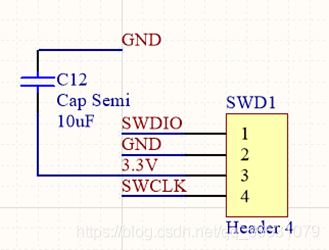

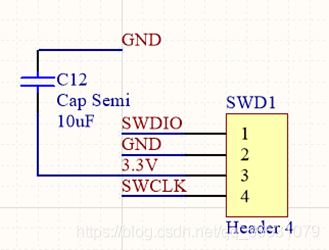

STM32芯片的程序下载电路有两种:串口下载和J-Link下载。在本次设计中,我们采用J-Link下载方式,具体设计电路如图2-10所示:

图2-10 下载电路设计图

图10所示的下载电路中,SWDIO接在芯片的PA13引脚,SWCLK接在芯片的PA14引脚。在接3.3V的引脚上接一个10uf的电容以减少噪音。同时,在设计时应尽量使得接下载线的排针靠近芯片的下载引脚,这样可以尽可能的减少外界干扰导致的下载失败。

在下载时,我们可以利用J-Link或者ST-Link连接电脑和单片机,然后将程序下载至单片机中

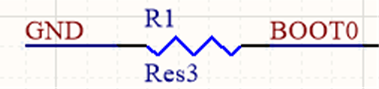

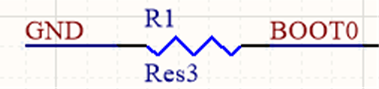

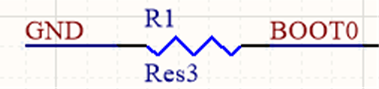

2.4.4 BOOT模式设置

STM32系列芯片可以通过设置BOOT引脚实现三种不同的启动模式,具体对应关系如表2-2所示:

当BOOT0置低时,启动模式为从主闪存存储器启动。主闪存存储器是STM32的内置Flash,当我们下载程序时就是将程序下载入主闪存存储器中,掉电重启也是从主闪存存储器启动。

当BOOT0置高,BOOT1置低时,启动模式为系统存储器启动。一般来说,采用此方式启动时会选择通过串口下载程序。

当BOOT0置高,BOOT1置高时,启动模式为内置SRAM启动。这种模式一般用于系统调试过程,一旦系统掉电,程序就会丢失。

在本设计中,由于我们采取的是JTAG模式下载程序,我们选择主闪存存储器作为系统的启动模式,即将BOOT0置为低电平,其具体设计图如图2-11所示:

图2-11 BOOT模式设计图

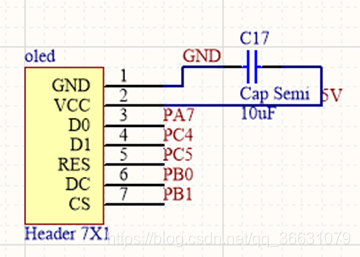

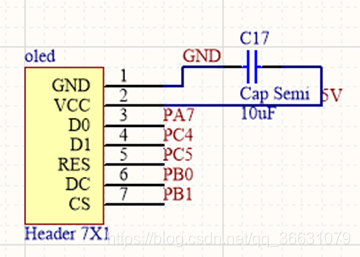

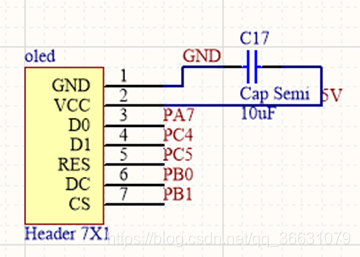

2.5 OLED显示电路

在系统调试时,一块OLED显示屏可以帮助我们实时的了解系统的工作情况,让我们及时地对系统进行改进。在设计完成之后,可以利用OLED显示屏显示实时的倾斜角度,让我们的设计结果更加直观。

本设计使用的是一个七脚OLED屏,其实物图如图2-12所示:

具体引脚定义为:1脚GND;

2脚VCC;

3脚D0:SPI时钟线;

4脚D1:SPI数据线;

5脚RES:OLED复位引脚;

6脚DC:SPI数据/命令选择脚;

7脚CS:SPI片选,低电平有效。

在本设计中,我们选择将OLED工作在模拟SPI模式之下。在接入电路时,我们用一个排座将其插在PCB板上。1脚和2脚分别接地和电源,其余几个引脚接于单片机普通IO口即可。具体设计图如图2-13所示:

图2-13 OLED接口设计图

同样的,在电源引脚处加上电容减少噪声。同时,我们在设计时需要注意抗干扰的问题,否则会导致OLED无法无法正常显示。信号线附近不能有强干扰源。此外,注意PCB板的布局,尽量将排座放置于板子的边缘,且将OLED朝向外部插入,否则由于OLED的高度,可能会导致PCB板上的其他元器件的布局受到一定的限制

2.6 485通信电路

本设计涉及到与上位机之间的通讯,需要将测量所得的倾斜角上传给上位机,同时需要接收上位机发送的阈值信息。在本设计中我们选择485协议作为我们的通信方式。

2.6.1 485通信协议

目前的工业设备通信基本都是通过异步串口通信,而其中又以RS232和RS485应用最为普遍。RS485通信协议规定了数据通信的电气特性,所以是物理层的概念,其对应的物理器件为RS485驱动芯片。RS485驱动芯片能够将UART传送过来的CPU的电压信号转换为RS485电平逻辑。

在工业应用中,RS485通信协议具有其独到的优势。采用平衡传输方式的RS485通信标准,使用双绞线进行传输,在传输速率为100Kbps时,传输距离可以达到1500米,远远高于其他通信协议。同时,其在远距离传输时的抗干扰能力也较为突出。

与RS232不同,RS485通常采用一对TTL电平的差分信号进行通信。RS485通常无法实现全双工通信,只能实现半双工通信,即在同一时间只能选择接收或者发送,无法同时进行。两者之间的具体差别如表2-3所示:

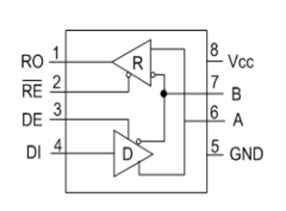

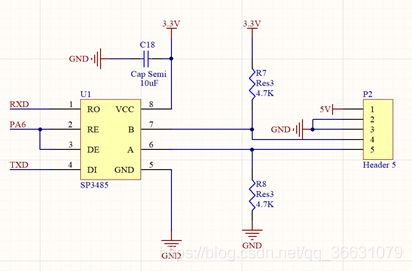

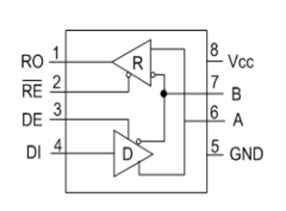

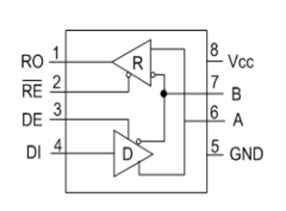

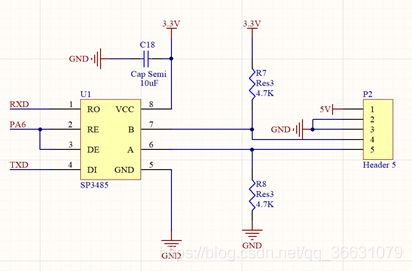

2.6.2 485通信电路设计

在此次设计中,我们所使用的485通信芯片为SP3485,此芯片为8脚SOIC封装,可以实现半双工通信。在此芯片处于发送状态时,输出采用差分输出,满足RS485标准,空载时输出电压为0V-3.3V,传输速率可以达到10Mbps,驱动器最大输出电流为250mA。处于接收状态时,输入灵敏度可以达到200mV,数据传输速率依然可以达到10Mbps,接收器具有故障自动保护特性,可以使得输出引脚在输入悬空时为高电平状态。另外,此芯片可以工作在关断状态下,此时输入使能和输出使能都被关断。芯片原理图如图2-14所示:

图2-14 SP3485结构图

对此芯片做如下说明:

芯片的5脚和8脚分别是GND和VCC;

2脚为接收使能引脚,低电平有效,1脚是数据接收引脚,接CPU的RX引脚;

3脚是发送使能引脚,高电平有效,4脚是数据接收引脚,接CPU的TX引脚;

6脚和7脚分别接485的和B,通过这两个引脚的差分电压进行数据的传输;

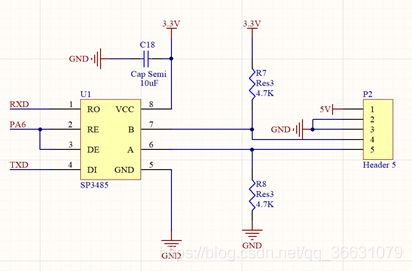

根据SP3485芯片的原理及功能,将其接入我们的系统中,具体设计如图2-15所示:

图2-15 485通信电路设计图

在图15所示电路图中,我们用PA6引脚作为发送和接收的使能引脚。当系统需要发送数据时,将PA6引脚置为高电平;当系统需要接收数据时,将PA6引脚置为低电平。RXD和TXD分别接CPU的USART2的RX和TX。P2排针外接一个485转USB的转换器,这样可以很方便的实现与电脑的通信。

值得注意的是,在芯片的A引脚和B引脚分别接了一个电阻到GND和VCC,这样做的目的是当SP3485不参与通信时不会影响网络的稳定性。另外若是涉及远距离通信,应在AB之间接一个匹配电阻,实现远距离的阻抗匹配。而本设计中的信息传输距离较近,故并未加入此匹配电阻。

2.7电源电路

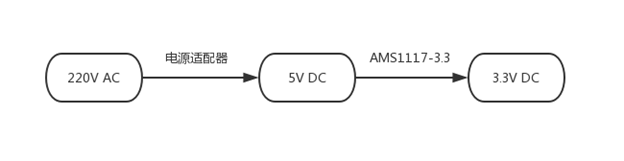

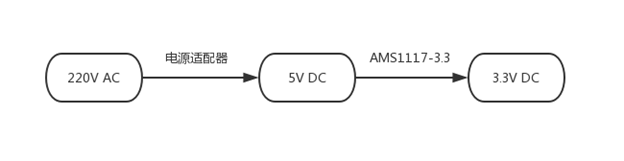

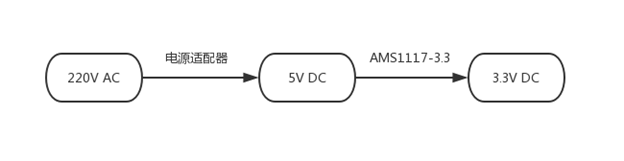

在分析第二章的硬件设计之后,可以发现5V和3.3V两种电压即可满足本设计所用器件的供电电压需求。由此本设计的电源部分设计思路为:用电源适配器将家用220V交流电转换为5V直流电接入电路以获得5V电压,再用5V转3.3V的稳压管获得3.3V电压供给电路。

因此本设计的电源部分设计思路如图2-16所示:

图2-16 电源部分设计流程图

在稳压管的选择上,本设计选用的是AMS1117-3.3型号稳压管,此稳压管可以将最高15V的直流电稳压为3.3V。其精度可以达到1%,且在内部集成了过热保护和限流电路,可以对设计电路起到很好的保护作用,很适合本设计的用途。

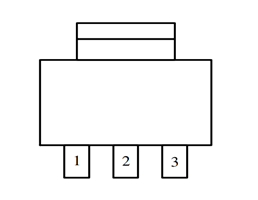

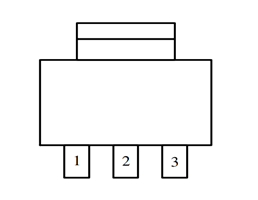

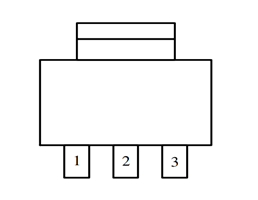

本设计所使用的AMS1117-3.3为3脚SOT-223封装,其封装如图2-17所示:

图2-17 AMS1117-3.3芯片SOT-223封装图

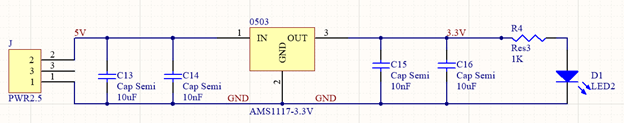

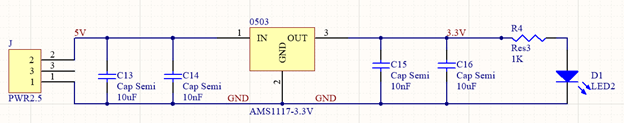

其中,1脚为GND,2脚为稳压输出,3脚为输入电压。将其接入本设计电路,具体设计图如图2-18所示:

图2-18 电源电路设计图

在图18所示设计图中,J为电源适配器接口,为电路提供5V直流电压。并在稳压管的输入端和输出端各加入两个滤波电容,可以使得稳压出的电压更加稳定。除此之外,在稳压后的电路加上一个LED灯,可以为电源电路的成功运行提供一个清晰的指示。

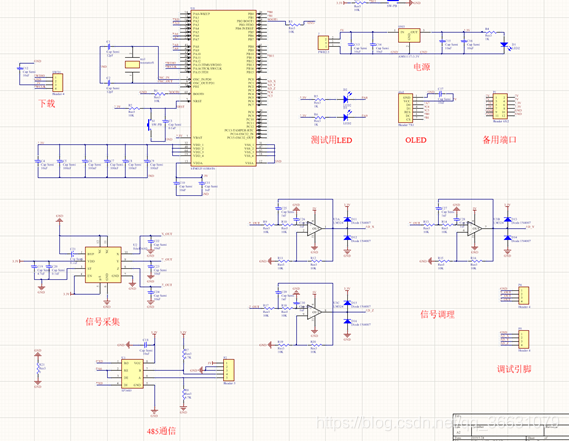

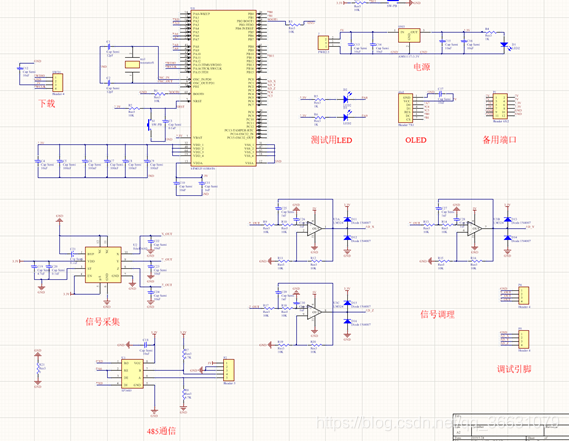

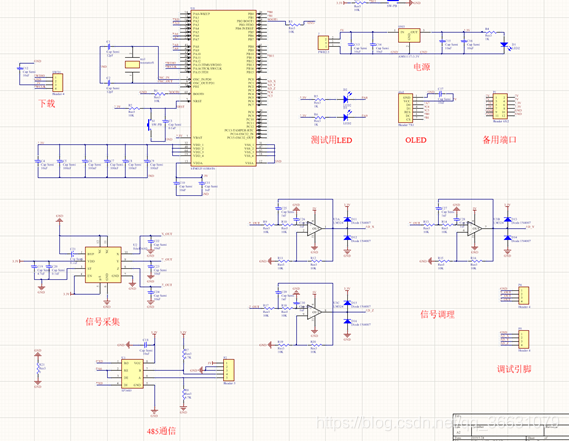

最终原理图:

2.4控制电路

本实验中选用的控制核心是STM32系列单片机,具体型号为STM32F103R8T6。STM32F103R8T6是一款嵌入式-微控制器集成电路,是ST旗下的一款常用的增强型系列微控制器。此芯片工作电压为2.0V-3.6V,处理速度为72MHz,芯片可以存储程序的容量为256KB,存储器类型为FLASH,RAM容量为48K。芯片共有64个引脚,采用LQFP64的封装,有49个GPIO口。其中,包含16个12位ADC通道,3组USART串口。

STM32作为CPU可以适用于很多场合,比如电机驱动、游戏外设和打印机等。

2.4.1晶振电路

STM32系统正常工作需要时钟,没有时钟的话系统就无法稳定工作。通过阅读芯片手册我们可以得知CPU内部有两个时钟源,我们要做的就是布置好系统的外部时钟源,此次设计中我们选用的是8M赫兹的石英晶振,封装为49S直插。硬件部分电路设计如图2-7所示:

图2-7 晶振电路设计图

图2-7的晶振可以等效成一个有两个谐振点的二端网络。然后再将其接入一个反馈电路,就可以构成正弦波振荡电路。

此外,此电路的振荡频率会比较稳定,其具体原因如下:在此电路中,两个谐振频率的相当的接近,在这种情况下,就算电路网络中的其他元件参数有较大变化,晶振电路的震荡频率不会有很大的变化。

在设计晶振电路时,除了选择晶振的频率之外,最重要的就是考虑晶振的负载电容值,取选择合适的电容接在晶振的两端。只有选择了合适的电容值,才可以使得晶振按照标称频率进行振荡。外接电容的计算原理如式2-7所示:

Cf=Cd*CgCd+Cg+Cic+∆C (2-7)

其中:Cf为晶振的负载电容;

CdCg为接入晶振两脚上的电容;

Cic为集成电路内部电容;

∆C为PCB板上的电容。

此外,出于简单考虑,两脚上的外接电容也可以直接选择与负载电容值相等的电容,也可以得到标称振荡频率。目前使用较多的是12.5pf的外接电容,来构成整个的晶振电路。

在设计晶振电路时,还有以下几点需要注意:

晶振内部的石英晶体要避免碰撞,防止破损引起的晶振不起振。所以在焊接时位置尽可能靠近CPU,远离PCB板的边缘;

在焊接时应尽量将外接电容靠近晶振的电源;

在焊接时注意温度控制,防止温度过高损坏晶振;

信号线避免经过晶振下方,防止产生信号干扰;

在连接时钟信号线时,走线应该尽量短且宽。

2.4.2复位电路

在进行CPU设计的时候,复位电路也是需要我们重点关注的。复位电路设计的效果,直接影响着设计出来的整个系统在工作时的可靠性和稳定性。如果复位电路设计时出现问题,导致即使在实验室等环境下可以成功工作,在工业现场也很容易出现很多问题。

单片机在上电之后都需要复位,这样可以使得整个系统从初始状态开始工作。复位电路的主要功能就在于在系统上电或者复位的过程中,复位电路可以保证CPU处于复位状态,而不是直接进行工作。否则单片机很容易发出错误的指令,影响到我们整个系统的稳定性。

我们需要设计的是系统的手动复位电路,在查阅相关资料之后,决定采取按键复位的电路进行设计。

在设计本系统的复位电路之前,我们首先关注一下STM32系列CPU的复位电路原理。通过查阅芯片的数据手册我们可以看到其原理图如图2-8所示:

图2-8 STM32复位电路原理图

通过数据手册上的原理图,我们可以发现此复位电路的工作方式为:NSRT通过电阻接到VDD,并通过一个电容去接地,且外接了一个按键。在正常工作时,NRST引脚通过一个上拉电阻上拉至高电平。在需要复位时,按下按键,将NRST引脚置为低电平,再经过芯片内部的反相器,就可以使得芯片的Reset为高电平,实现芯片的复位。事实上,Reset需要保持一定时间的高电平才可以成功复位,但以人按键的时间来看是足以满足这个要求的。

了解了芯片复位电路的原理,我们就可以来设计本系统的按键复位电路了,具体设计结果如图2-9所示:

图2-9 复位电路设计图

需要说明的是,在图2-9所示的复位电路中,我们在芯片NRST引脚外接了一个上拉电阻。事实上,我们可以从图8的原理图中得知此芯片内部是有一个上拉电阻的,所以此处的上拉电阻可以省去。不过,鉴于有些芯片的内部没有上拉电阻,需要这个外接的上拉电阻,我们可以把这个当作一个好习惯保留下来。同时,外加的上拉电阻也可以增强系统抗电磁干扰的能力。

在图2-9所示的电路中,当电路正常工作时,NRST引脚为高电平。在我们需要对系统进行复位操作时,按下按键使得NRST引脚接地,成为低电平,完成对芯片的复位操作。此电路简单实用,在我们此后的调试过程中起着很重要的作用。

2.4.3下载电路

下载电路是一个系统的基础,下载电路如果有差错,会导致程序无法下载,进而整个系统就会瘫痪。

STM32芯片的程序下载电路有两种:串口下载和J-Link下载。在本次设计中,我们采用J-Link下载方式,具体设计电路如图2-10所示:

图2-10 下载电路设计图

图10所示的下载电路中,SWDIO接在芯片的PA13引脚,SWCLK接在芯片的PA14引脚。在接3.3V的引脚上接一个10uf的电容以减少噪音。同时,在设计时应尽量使得接下载线的排针靠近芯片的下载引脚,这样可以尽可能的减少外界干扰导致的下载失败。

在下载时,我们可以利用J-Link或者ST-Link连接电脑和单片机,然后将程序下载至单片机中

2.4.4 BOOT模式设置

STM32系列芯片可以通过设置BOOT引脚实现三种不同的启动模式,具体对应关系如表2-2所示:

当BOOT0置低时,启动模式为从主闪存存储器启动。主闪存存储器是STM32的内置Flash,当我们下载程序时就是将程序下载入主闪存存储器中,掉电重启也是从主闪存存储器启动。

当BOOT0置高,BOOT1置低时,启动模式为系统存储器启动。一般来说,采用此方式启动时会选择通过串口下载程序。

当BOOT0置高,BOOT1置高时,启动模式为内置SRAM启动。这种模式一般用于系统调试过程,一旦系统掉电,程序就会丢失。

在本设计中,由于我们采取的是JTAG模式下载程序,我们选择主闪存存储器作为系统的启动模式,即将BOOT0置为低电平,其具体设计图如图2-11所示:

图2-11 BOOT模式设计图

2.5 OLED显示电路

在系统调试时,一块OLED显示屏可以帮助我们实时的了解系统的工作情况,让我们及时地对系统进行改进。在设计完成之后,可以利用OLED显示屏显示实时的倾斜角度,让我们的设计结果更加直观。

本设计使用的是一个七脚OLED屏,其实物图如图2-12所示:

具体引脚定义为:1脚GND;

2脚VCC;

3脚D0:SPI时钟线;

4脚D1:SPI数据线;

5脚RES:OLED复位引脚;

6脚DC:SPI数据/命令选择脚;

7脚CS:SPI片选,低电平有效。

在本设计中,我们选择将OLED工作在模拟SPI模式之下。在接入电路时,我们用一个排座将其插在PCB板上。1脚和2脚分别接地和电源,其余几个引脚接于单片机普通IO口即可。具体设计图如图2-13所示:

图2-13 OLED接口设计图

同样的,在电源引脚处加上电容减少噪声。同时,我们在设计时需要注意抗干扰的问题,否则会导致OLED无法无法正常显示。信号线附近不能有强干扰源。此外,注意PCB板的布局,尽量将排座放置于板子的边缘,且将OLED朝向外部插入,否则由于OLED的高度,可能会导致PCB板上的其他元器件的布局受到一定的限制

2.6 485通信电路

本设计涉及到与上位机之间的通讯,需要将测量所得的倾斜角上传给上位机,同时需要接收上位机发送的阈值信息。在本设计中我们选择485协议作为我们的通信方式。

2.6.1 485通信协议

目前的工业设备通信基本都是通过异步串口通信,而其中又以RS232和RS485应用最为普遍。RS485通信协议规定了数据通信的电气特性,所以是物理层的概念,其对应的物理器件为RS485驱动芯片。RS485驱动芯片能够将UART传送过来的CPU的电压信号转换为RS485电平逻辑。

在工业应用中,RS485通信协议具有其独到的优势。采用平衡传输方式的RS485通信标准,使用双绞线进行传输,在传输速率为100Kbps时,传输距离可以达到1500米,远远高于其他通信协议。同时,其在远距离传输时的抗干扰能力也较为突出。

与RS232不同,RS485通常采用一对TTL电平的差分信号进行通信。RS485通常无法实现全双工通信,只能实现半双工通信,即在同一时间只能选择接收或者发送,无法同时进行。两者之间的具体差别如表2-3所示:

2.6.2 485通信电路设计

在此次设计中,我们所使用的485通信芯片为SP3485,此芯片为8脚SOIC封装,可以实现半双工通信。在此芯片处于发送状态时,输出采用差分输出,满足RS485标准,空载时输出电压为0V-3.3V,传输速率可以达到10Mbps,驱动器最大输出电流为250mA。处于接收状态时,输入灵敏度可以达到200mV,数据传输速率依然可以达到10Mbps,接收器具有故障自动保护特性,可以使得输出引脚在输入悬空时为高电平状态。另外,此芯片可以工作在关断状态下,此时输入使能和输出使能都被关断。芯片原理图如图2-14所示:

图2-14 SP3485结构图

对此芯片做如下说明:

芯片的5脚和8脚分别是GND和VCC;

2脚为接收使能引脚,低电平有效,1脚是数据接收引脚,接CPU的RX引脚;

3脚是发送使能引脚,高电平有效,4脚是数据接收引脚,接CPU的TX引脚;

6脚和7脚分别接485的和B,通过这两个引脚的差分电压进行数据的传输;

根据SP3485芯片的原理及功能,将其接入我们的系统中,具体设计如图2-15所示:

图2-15 485通信电路设计图

在图15所示电路图中,我们用PA6引脚作为发送和接收的使能引脚。当系统需要发送数据时,将PA6引脚置为高电平;当系统需要接收数据时,将PA6引脚置为低电平。RXD和TXD分别接CPU的USART2的RX和TX。P2排针外接一个485转USB的转换器,这样可以很方便的实现与电脑的通信。

值得注意的是,在芯片的A引脚和B引脚分别接了一个电阻到GND和VCC,这样做的目的是当SP3485不参与通信时不会影响网络的稳定性。另外若是涉及远距离通信,应在AB之间接一个匹配电阻,实现远距离的阻抗匹配。而本设计中的信息传输距离较近,故并未加入此匹配电阻。

2.7电源电路

在分析第二章的硬件设计之后,可以发现5V和3.3V两种电压即可满足本设计所用器件的供电电压需求。由此本设计的电源部分设计思路为:用电源适配器将家用220V交流电转换为5V直流电接入电路以获得5V电压,再用5V转3.3V的稳压管获得3.3V电压供给电路。

因此本设计的电源部分设计思路如图2-16所示:

图2-16 电源部分设计流程图

在稳压管的选择上,本设计选用的是AMS1117-3.3型号稳压管,此稳压管可以将最高15V的直流电稳压为3.3V。其精度可以达到1%,且在内部集成了过热保护和限流电路,可以对设计电路起到很好的保护作用,很适合本设计的用途。

本设计所使用的AMS1117-3.3为3脚SOT-223封装,其封装如图2-17所示:

图2-17 AMS1117-3.3芯片SOT-223封装图

其中,1脚为GND,2脚为稳压输出,3脚为输入电压。将其接入本设计电路,具体设计图如图2-18所示:

图2-18 电源电路设计图

在图18所示设计图中,J为电源适配器接口,为电路提供5V直流电压。并在稳压管的输入端和输出端各加入两个滤波电容,可以使得稳压出的电压更加稳定。除此之外,在稳压后的电路加上一个LED灯,可以为电源电路的成功运行提供一个清晰的指示。

最终原理图:

举报

举报

举报

举报