第一章

1.1 开关电路数学表示方法初步

1.1.1 真值表

1.1.2 二进制编码

1.1.3 真值表的常见形式

1.1.4 分析与综合

1.2 逻辑代数

1.2.1 逻辑代数的基本运算

与,或,非三种运算

1.2.2 逻辑函数

逻辑函数的等价性判断

逻辑函数的等价性判断

1.2.3 逻辑代数的基本公式和运算规则

基本公式:0律,对合律,1律,重叠律,互补律,交换律,结合律,分配律,吸收律,德摩根律,包含律。

公式具有对偶性:

*把一个公式当中的运算符 “ 。 ”替换成”+“,把运算符”+“替换成” 。 “,把常数0替换成1,把常数1替换成0,将得到对应的公式。

对新产生的公式作同样的替换,将的到原公式。

公式法证明公式的正确性

(1)对偶规则

(2)反演规则

1.3 用与门,或门和非门进行逻辑综合

1.4公式法化简逻辑函数

1.合并乘积项法

2.吸收法

3.消去法

4.添加项法

5.配项法

1.5 卡诺图 化简逻辑函数

1.5.1 卡诺图是是真值表的图形表现形式

1.5.2 用卡诺图化简逻辑函数

名词术语:

* 乘积项

* 文字

*最小项

*最大项

*最小项的性质

1.5.2 用卡诺图化简逻辑函数

名词术语:

*逻辑相邻与几何相邻:

卡诺图可以看作一张纸,将其卷成一个圆筒,则原来两边不相邻的部分就变成了相邻的部分,所以在消除冗余的时候需要考虑。

1.5.3 概念提升

*质蕴含项 :在卡诺图用是圈,圈中的个数必须为偶数个。

*特征最小项: 用方框圈住,只有一个数。

*必要质蕴含项: 双环圈

*覆盖:

若一个蕴含项的集合能说明给定逻辑函数f为1

的所有情况,则称次蕴含项集合是函数f的覆盖。覆盖和函数的积之和表达式相对应。

*最小覆盖:

函数的最小覆盖和成本最低的:积之和表达式,相对应,其要求为:

1.最小覆盖中包含的蕴含项最少。

2.每一个蕴含项的文字个数尽量少,即蕴含项的维数尽量大。

*必要质蕴含项必定是最小覆盖的元素。

*冗(rong)余项 (打拼音是因为这个字我不会读(┭┮﹏┭┮)

*无冗余覆盖:

覆盖中每一个蕴含项必须是质蕴含项

覆盖中不含冗余项

1.6 逻辑函数的标准形式

*函数的积之和表达式

*函数的和之积表达式

*和之积与积之和之间的反演规则

注意:在卡诺图当中,画圈圈,画1则是积之和,画0则是和之积。

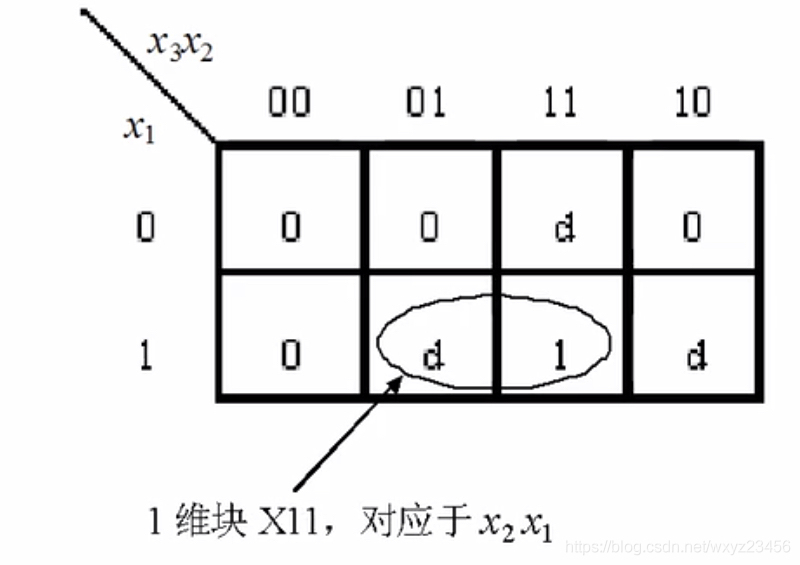

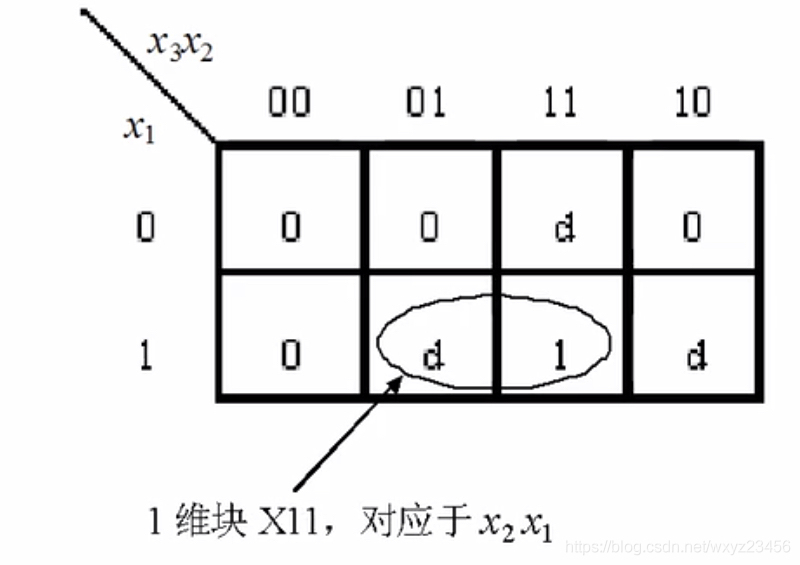

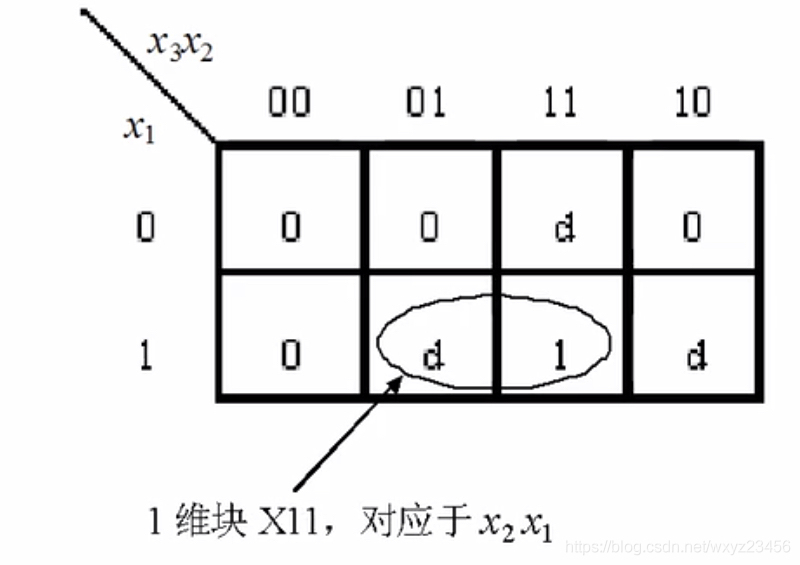

*用卡诺图化简不完全确定的逻辑函数

。d的取值可以为0也可以为1,以化简效果最佳为目的,例如:

下面式子的用卡诺图来表示的样子为:

第二章

2.1 概述

*门电路由晶体管和电阻等元件组成。

》双极晶体管

》金属-氧化物-半导体

*集成电路

几种工作状态

2.2 TTL集成电路

2.2.1 典型的TTL与非门

只需简单了解,知道一些器件高电平和低电平就可以

2.2.2TTL与非门的外特性及其参数

外特性:

1.电压传输特性:

2.驱动负载能力(扇出系数N)

(1)驱动们的输入皆为高电平时,输出为低电平

灌入电流i过大将使输出电平v0抬高,负载个数受限。

(2)驱动门的输入之一为低电平时,输出为高电平。

驱动们通过T4的发射极向负载门供给电流i,负载增多将使拉出电流i加大,导致输出电平降低。

3.传输延迟

t(PHL)–输出电压由高到低的传输延迟时间

t(PLH)–输出电压由低到高的传输延迟时间

t(PD)–平均传输延迟时间

t(PD)=(t(PHL)+t(PLH))/2;

传输延迟时间分析:

晶体管由截止到导通或导通到截止所经历的时间,此延迟和晶体管自身特性有关。

与非门输出电平变化对负载电容充放电所经历的时间。随着负载的增多,此延迟时间增大。

4.功耗

空载功耗:

未带任何负载时的静态功耗称为空载功耗。其典型值为16mW。

浪涌电流引起的功耗:

TTL与非门的输出电平发生变化时,在一个端在的时段里,T3.T4.T5会同时导通,此时会有一个很大的瞬间电流从电源Vcc经T3,T4和T5流向地面,次尖峰称为浪涌电流。

浪涌电流不仅使动态功耗增大,而且会在电源线和地线上造成干扰信号。

2.2.3 集合电极开路的与非门(Open Collecotor Gate)

简称OC门,老师在视频当中说会考到。

主要会考到OC门是怎么用的,其实是前面讲到的与非门并联的一种电路。

但是OC门在使用是一定要外接电源和电阻才能正常工作。

其工作原理如下:

1)当 输入全为高电平时,输出低电平。

2)当输入全为低电平时,输出高电平。

*OC门应用之一:输出端并联形成”线或“逻辑。

*OC门应用之二:驱动其它器件,例如用于驱动显示灯。

2.2.4 TTL三态门

*三态门的其它形式

*用三态门的构建总线

*约束条件

2.3 MOS场效应晶体管

原理:只需了解

主要是它的应用

PMOS晶体管:

*VGS=5V时,PMOS晶体管截止;

*VFS=0V时,PMOS晶体管导通;

2.4 MOS门电路

2.4.1 NMOS门电路

与门,非门,或非门

上拉电阻R对NMOS逻辑门电性能的影响:

R取值偏大有利降低功耗

2.4.2 CMOS门电路

*CMOS门电路是对NMOS门电路的改进

-》既希望降低功耗(加大等效的上拉电阻)

-》又希望减小对计生电容的充放电时间

上下网络为互补关系,下拉网络导通上拉网络必然截止,下拉网络截止必然上拉网络导通。静态功耗为0.

2.4.3 其它类型的CMOS门电路

2.4.4 CMOS逻辑门电性分析

*1驱动负载能力

*2功耗

静态功耗

动态功耗

*3噪声容限和抗干扰能力

2.4.5 不同类型逻辑门的配合问题

*逻辑电平多的配合

2.5 74系列中小规模集成电路芯片

*逻辑器件: 用来实现某种特定逻辑功能的电子器件

2.6 可编程逻辑器件

*可编程逻辑器件

2.6.1 可编程逻辑阵列PLA

2.6.3 复杂2可编程器件 CPLD

第一章

1.1 开关电路数学表示方法初步

1.1.1 真值表

1.1.2 二进制编码

1.1.3 真值表的常见形式

1.1.4 分析与综合

1.2 逻辑代数

1.2.1 逻辑代数的基本运算

与,或,非三种运算

1.2.2 逻辑函数

逻辑函数的等价性判断

逻辑函数的等价性判断

1.2.3 逻辑代数的基本公式和运算规则

基本公式:0律,对合律,1律,重叠律,互补律,交换律,结合律,分配律,吸收律,德摩根律,包含律。

公式具有对偶性:

*把一个公式当中的运算符 “ 。 ”替换成”+“,把运算符”+“替换成” 。 “,把常数0替换成1,把常数1替换成0,将得到对应的公式。

对新产生的公式作同样的替换,将的到原公式。

公式法证明公式的正确性

(1)对偶规则

(2)反演规则

1.3 用与门,或门和非门进行逻辑综合

1.4公式法化简逻辑函数

1.合并乘积项法

2.吸收法

3.消去法

4.添加项法

5.配项法

1.5 卡诺图 化简逻辑函数

1.5.1 卡诺图是是真值表的图形表现形式

1.5.2 用卡诺图化简逻辑函数

名词术语:

* 乘积项

* 文字

*最小项

*最大项

*最小项的性质

1.5.2 用卡诺图化简逻辑函数

名词术语:

*逻辑相邻与几何相邻:

卡诺图可以看作一张纸,将其卷成一个圆筒,则原来两边不相邻的部分就变成了相邻的部分,所以在消除冗余的时候需要考虑。

1.5.3 概念提升

*质蕴含项 :在卡诺图用是圈,圈中的个数必须为偶数个。

*特征最小项: 用方框圈住,只有一个数。

*必要质蕴含项: 双环圈

*覆盖:

若一个蕴含项的集合能说明给定逻辑函数f为1

的所有情况,则称次蕴含项集合是函数f的覆盖。覆盖和函数的积之和表达式相对应。

*最小覆盖:

函数的最小覆盖和成本最低的:积之和表达式,相对应,其要求为:

1.最小覆盖中包含的蕴含项最少。

2.每一个蕴含项的文字个数尽量少,即蕴含项的维数尽量大。

*必要质蕴含项必定是最小覆盖的元素。

*冗(rong)余项 (打拼音是因为这个字我不会读(┭┮﹏┭┮)

*无冗余覆盖:

覆盖中每一个蕴含项必须是质蕴含项

覆盖中不含冗余项

1.6 逻辑函数的标准形式

*函数的积之和表达式

*函数的和之积表达式

*和之积与积之和之间的反演规则

注意:在卡诺图当中,画圈圈,画1则是积之和,画0则是和之积。

*用卡诺图化简不完全确定的逻辑函数

。d的取值可以为0也可以为1,以化简效果最佳为目的,例如:

下面式子的用卡诺图来表示的样子为:

第二章

2.1 概述

*门电路由晶体管和电阻等元件组成。

》双极晶体管

》金属-氧化物-半导体

*集成电路

几种工作状态

2.2 TTL集成电路

2.2.1 典型的TTL与非门

只需简单了解,知道一些器件高电平和低电平就可以

2.2.2TTL与非门的外特性及其参数

外特性:

1.电压传输特性:

2.驱动负载能力(扇出系数N)

(1)驱动们的输入皆为高电平时,输出为低电平

灌入电流i过大将使输出电平v0抬高,负载个数受限。

(2)驱动门的输入之一为低电平时,输出为高电平。

驱动们通过T4的发射极向负载门供给电流i,负载增多将使拉出电流i加大,导致输出电平降低。

3.传输延迟

t(PHL)–输出电压由高到低的传输延迟时间

t(PLH)–输出电压由低到高的传输延迟时间

t(PD)–平均传输延迟时间

t(PD)=(t(PHL)+t(PLH))/2;

传输延迟时间分析:

晶体管由截止到导通或导通到截止所经历的时间,此延迟和晶体管自身特性有关。

与非门输出电平变化对负载电容充放电所经历的时间。随着负载的增多,此延迟时间增大。

4.功耗

空载功耗:

未带任何负载时的静态功耗称为空载功耗。其典型值为16mW。

浪涌电流引起的功耗:

TTL与非门的输出电平发生变化时,在一个端在的时段里,T3.T4.T5会同时导通,此时会有一个很大的瞬间电流从电源Vcc经T3,T4和T5流向地面,次尖峰称为浪涌电流。

浪涌电流不仅使动态功耗增大,而且会在电源线和地线上造成干扰信号。

2.2.3 集合电极开路的与非门(Open Collecotor Gate)

简称OC门,老师在视频当中说会考到。

主要会考到OC门是怎么用的,其实是前面讲到的与非门并联的一种电路。

但是OC门在使用是一定要外接电源和电阻才能正常工作。

其工作原理如下:

1)当 输入全为高电平时,输出低电平。

2)当输入全为低电平时,输出高电平。

*OC门应用之一:输出端并联形成”线或“逻辑。

*OC门应用之二:驱动其它器件,例如用于驱动显示灯。

2.2.4 TTL三态门

*三态门的其它形式

*用三态门的构建总线

*约束条件

2.3 MOS场效应晶体管

原理:只需了解

主要是它的应用

PMOS晶体管:

*VGS=5V时,PMOS晶体管截止;

*VFS=0V时,PMOS晶体管导通;

2.4 MOS门电路

2.4.1 NMOS门电路

与门,非门,或非门

上拉电阻R对NMOS逻辑门电性能的影响:

R取值偏大有利降低功耗

2.4.2 CMOS门电路

*CMOS门电路是对NMOS门电路的改进

-》既希望降低功耗(加大等效的上拉电阻)

-》又希望减小对计生电容的充放电时间

上下网络为互补关系,下拉网络导通上拉网络必然截止,下拉网络截止必然上拉网络导通。静态功耗为0.

2.4.3 其它类型的CMOS门电路

2.4.4 CMOS逻辑门电性分析

*1驱动负载能力

*2功耗

静态功耗

动态功耗

*3噪声容限和抗干扰能力

2.4.5 不同类型逻辑门的配合问题

*逻辑电平多的配合

2.5 74系列中小规模集成电路芯片

*逻辑器件: 用来实现某种特定逻辑功能的电子器件

2.6 可编程逻辑器件

*可编程逻辑器件

2.6.1 可编程逻辑阵列PLA

2.6.3 复杂2可编程器件 CPLD

举报

举报

举报

举报