音频的时间延迟传统上使用延迟线或电荷耦合器件实现,这在民用设备中有着广泛的应用。最常见的是卡拉OK机的混响系统,它使用延迟一定时间的信号产生回声的效果。某些专用的BBE器件,如三菱的M58000系列,内部采用了数模和模数转换技术,内置动态RAM存储数据,某些芯片可以通过调整其时钟频率或有专用引脚调整延时量。可调范围在数百毫秒量级,误差在毫秒量级。这些芯片普遍采用较低的采样速率,仅对输入信号的低频分量进行处理,采样位数也多为8位以下。这在一般应用中,特别是卡拉OK机这类对音频指标要求较低的应用中完全足够了。而在“调频同步广播”项目中,涉及多个发射台干涉区的准确同步问题,要求延迟量精确到微秒数量级并且能依据两发射台间的距离做调整,几个微秒的时延误差就会对干涉区的收听质量产生很大的影响,甚至不能正常收听。并且调频广播对音质有较高的要求,所以设计出来的系统必须达到广播级的音频指标,左右声道的延时应该同步调节,以满足立体声分离度的要求。很明显,前述的各类现有器件远不能满足需要。

受到新型数字混响器件原理的启发,设想采用高指标的数模模数集成电路实现这样一个系统。随着数字集成电路技术特别是大规模可编程逻辑器件技术的发展,一个数字系统已可以集成在一片可编程芯片上,因此采用CPLD设计时序及逻辑电路是最佳方案,考虑音频采样频率达到48KHz即可满足要求,存储器可以采用通用的RAM,速度在150ns的也可满足需要。理论及实践证明,以上方案是完全可行的。

系统设计

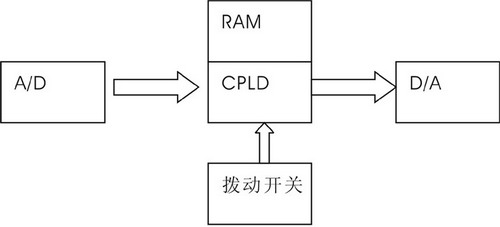

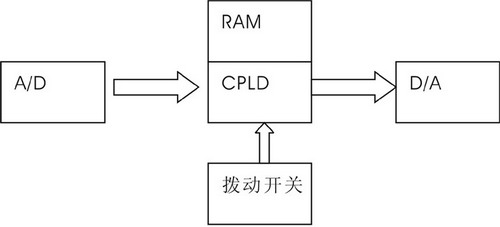

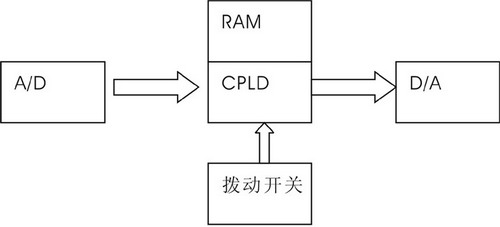

图1 系统框图

系统方框图如图1。前级来的音频模拟信号首先进入A/D转换器变成数字信号,由CPLD产生存储器的读写时序并把音频数据依次存入存储器中。也由CPLD产生存储器读时序,把数据依次读出并送到D/A转换器恢复成模拟的音频信号,经低通滤波器输出。存储器的地址由一个循环计数器产生,控制写入和读出的地址(地址间隔),就可实现定量延时。考虑到当前大部分音频专用A/D、D/A芯片采用串行数字接口,特别是在音频领域占统治地位的Σ-Δ类型的芯片,这样的设计应由以下几部分组成:

*串并转换部分,用以把A/D来的串行数据转变成存储器RAM的并行数据;

*存储器时序产生部分,用以产生存储器的读和写两个地址信号;

*延时调整部分,用DIP拨动开关预置读和写两种情况下的地址之差;

*并串转换部分,用来把RAM的数据转换成D/A需要的标准串行数据流;

*左右声道校正部分,保证左右声道读出的顺序;

*晶体振荡器,产生系统所需的时钟信号,保证系统时钟的准确和稳定。延时量的准确性和稳定性由它保证(使用外频标可以进一步提高其准确度);

*一些辅助电路,用来校正由于门电路的延迟造成的时序和逻辑错误。

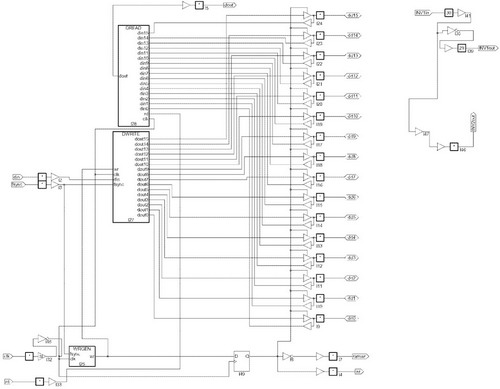

采用自顶向下,逐步细化的设计方法,顶层用电路示于图2a和2b。

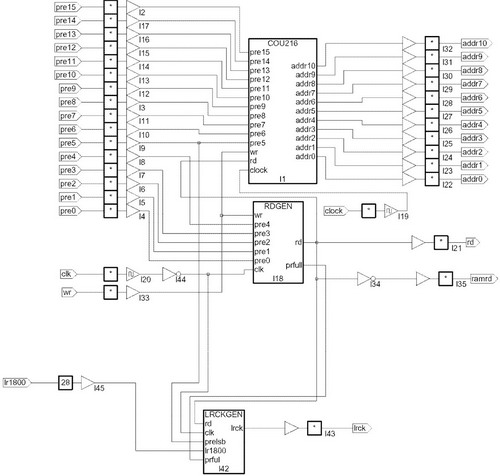

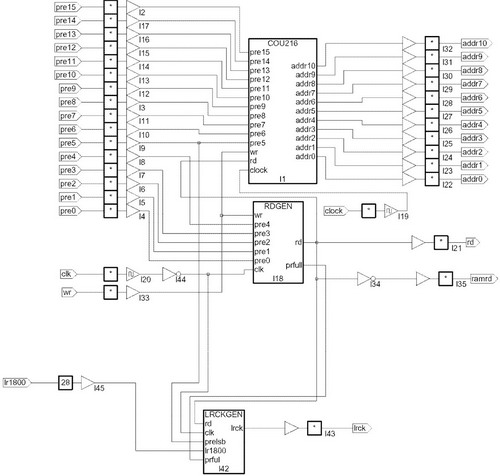

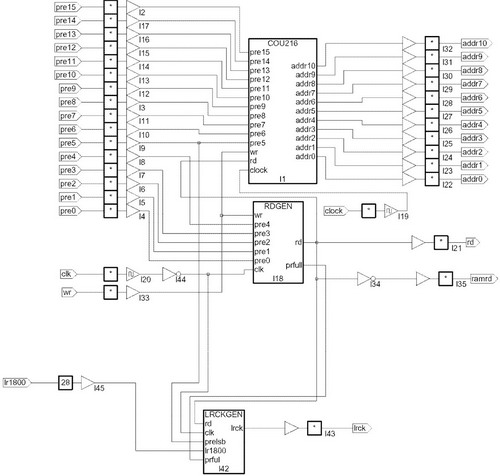

图2a 延时量预置、RAM地址和左右声道同步

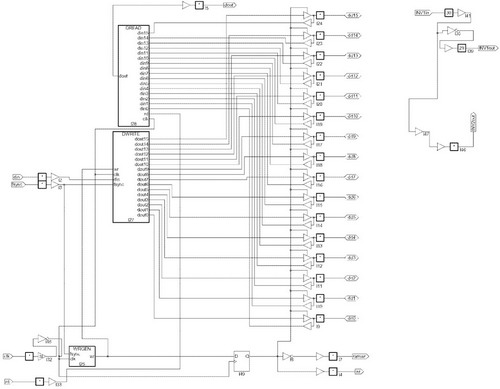

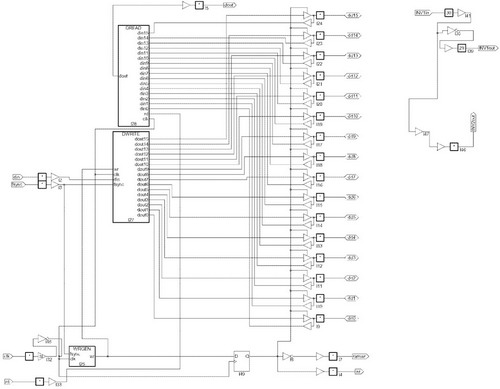

图2b 振荡器、串并转换、RAM接口和和写信号产生

选用元件在保证指标的前提下尽量降低成本。音频领域常用的数模和模数转换芯片有CIRRUS和BURR-BROWN公司的几种型号,例如CS4332、PCM1800系列、PCM1700系列等,采样频率达100KHz,16位或24位的产品价格已降到了一定的水平。此处选用的A/D芯片是Σ-Δ类型的PCM1800,D/A芯片是PCM1725,它们都是B-B公司的新产品,可以达到20位的无误码采样分辨率,采样频率分别是48KHz和96KHz,信噪比和失真指标都较高。CPLD器件选用规模适中,可以ISP在线编程修改的品种,这样可以加快研发速度。选用VATIS的MACH4A系列,PLCC封装,容易小规模试生产,并有ISP功能,不需专用编程器,通过串行下载电缆编程,调试修改都很方便。RAM用一般的100-150纳秒的就足够了。 PCM1800工作于主动模式,按照输入的时钟信号进行A/D转换并输出同步时钟和数据。整个CPLD电路按照PCM1800输出的同步时钟工作。

首先估算所需逻辑规模和引脚数,PCM1800的关键信号有四个引脚,D/A的PCM1725同样需三个引脚,48KHz采样频率时每个采样周期是20.8ms,预定最大延时量要达到80ms左右,外接存储器需要11位地址线。使用16位分辨率,则存储器接口部分共需27个引脚,控制延迟时间的DIP开关需16位,外加一个晶体振荡器需2-3个引脚,两片MACH4-64/32之间的逻辑联系需四个引脚,总计大约57个引脚,其中有输出和输入,以及双向引脚。需要的资源大致可以用两片MACH4-64/32或一片MACH4-128完成。单纯改变存储器的读出地址能达到的最小延时调整步进取决于采样频率,这里是20.8/2=10.4ms,仍满足不了最小调整分辨率的要求。最终系统又加上延时微调部分,通过改变存储器读信号相对于写信号的位置,实现更精确的调整,完成的系统最小步进达到625ns,达到了设计要求。

所有设计文件采用原理图(顶层)和VHDL语言(底层)完成,在LATTICE的ispLEVER软件下编译并适配到两片MACH4-64/32A中,仿真后,下载到器件中去,经过实际系统测试并修改某些逻辑后设计完成。电路板是事先设计好的,MACH器件有强大的布线能力,保证了适配以及实际系统运行的成功。

结语

作为“调频同步广播”项目的关键技术之一,音频精确延时系统把卫星传输的音频信号,在不同接收地点进行精确和稳定的延时,补偿了由于各发射台经纬度不同造成的信号不同步,实现了真正意义上的同步广播。针对我国幅员辽阔,人口分散而频率资源匮乏的实际情况,该方案给出了一种较好的广播覆盖方法。此系统已用于国家广电总局提出的“村村通广播电视”工程,带来了良好的社会效益和经济效益。推而广之,通过增加逻辑规模和存储器容量,这种方法也可用于其他需要高质量音频延迟的场合。

音频的时间延迟传统上使用延迟线或电荷耦合器件实现,这在民用设备中有着广泛的应用。最常见的是卡拉OK机的混响系统,它使用延迟一定时间的信号产生回声的效果。某些专用的BBE器件,如三菱的M58000系列,内部采用了数模和模数转换技术,内置动态RAM存储数据,某些芯片可以通过调整其时钟频率或有专用引脚调整延时量。可调范围在数百毫秒量级,误差在毫秒量级。这些芯片普遍采用较低的采样速率,仅对输入信号的低频分量进行处理,采样位数也多为8位以下。这在一般应用中,特别是卡拉OK机这类对音频指标要求较低的应用中完全足够了。而在“调频同步广播”项目中,涉及多个发射台干涉区的准确同步问题,要求延迟量精确到微秒数量级并且能依据两发射台间的距离做调整,几个微秒的时延误差就会对干涉区的收听质量产生很大的影响,甚至不能正常收听。并且调频广播对音质有较高的要求,所以设计出来的系统必须达到广播级的音频指标,左右声道的延时应该同步调节,以满足立体声分离度的要求。很明显,前述的各类现有器件远不能满足需要。

受到新型数字混响器件原理的启发,设想采用高指标的数模模数集成电路实现这样一个系统。随着数字集成电路技术特别是大规模可编程逻辑器件技术的发展,一个数字系统已可以集成在一片可编程芯片上,因此采用CPLD设计时序及逻辑电路是最佳方案,考虑音频采样频率达到48KHz即可满足要求,存储器可以采用通用的RAM,速度在150ns的也可满足需要。理论及实践证明,以上方案是完全可行的。

系统设计

图1 系统框图

系统方框图如图1。前级来的音频模拟信号首先进入A/D转换器变成数字信号,由CPLD产生存储器的读写时序并把音频数据依次存入存储器中。也由CPLD产生存储器读时序,把数据依次读出并送到D/A转换器恢复成模拟的音频信号,经低通滤波器输出。存储器的地址由一个循环计数器产生,控制写入和读出的地址(地址间隔),就可实现定量延时。考虑到当前大部分音频专用A/D、D/A芯片采用串行数字接口,特别是在音频领域占统治地位的Σ-Δ类型的芯片,这样的设计应由以下几部分组成:

*串并转换部分,用以把A/D来的串行数据转变成存储器RAM的并行数据;

*存储器时序产生部分,用以产生存储器的读和写两个地址信号;

*延时调整部分,用DIP拨动开关预置读和写两种情况下的地址之差;

*并串转换部分,用来把RAM的数据转换成D/A需要的标准串行数据流;

*左右声道校正部分,保证左右声道读出的顺序;

*晶体振荡器,产生系统所需的时钟信号,保证系统时钟的准确和稳定。延时量的准确性和稳定性由它保证(使用外频标可以进一步提高其准确度);

*一些辅助电路,用来校正由于门电路的延迟造成的时序和逻辑错误。

采用自顶向下,逐步细化的设计方法,顶层用电路示于图2a和2b。

图2a 延时量预置、RAM地址和左右声道同步

图2b 振荡器、串并转换、RAM接口和和写信号产生

选用元件在保证指标的前提下尽量降低成本。音频领域常用的数模和模数转换芯片有CIRRUS和BURR-BROWN公司的几种型号,例如CS4332、PCM1800系列、PCM1700系列等,采样频率达100KHz,16位或24位的产品价格已降到了一定的水平。此处选用的A/D芯片是Σ-Δ类型的PCM1800,D/A芯片是PCM1725,它们都是B-B公司的新产品,可以达到20位的无误码采样分辨率,采样频率分别是48KHz和96KHz,信噪比和失真指标都较高。CPLD器件选用规模适中,可以ISP在线编程修改的品种,这样可以加快研发速度。选用VATIS的MACH4A系列,PLCC封装,容易小规模试生产,并有ISP功能,不需专用编程器,通过串行下载电缆编程,调试修改都很方便。RAM用一般的100-150纳秒的就足够了。 PCM1800工作于主动模式,按照输入的时钟信号进行A/D转换并输出同步时钟和数据。整个CPLD电路按照PCM1800输出的同步时钟工作。

首先估算所需逻辑规模和引脚数,PCM1800的关键信号有四个引脚,D/A的PCM1725同样需三个引脚,48KHz采样频率时每个采样周期是20.8ms,预定最大延时量要达到80ms左右,外接存储器需要11位地址线。使用16位分辨率,则存储器接口部分共需27个引脚,控制延迟时间的DIP开关需16位,外加一个晶体振荡器需2-3个引脚,两片MACH4-64/32之间的逻辑联系需四个引脚,总计大约57个引脚,其中有输出和输入,以及双向引脚。需要的资源大致可以用两片MACH4-64/32或一片MACH4-128完成。单纯改变存储器的读出地址能达到的最小延时调整步进取决于采样频率,这里是20.8/2=10.4ms,仍满足不了最小调整分辨率的要求。最终系统又加上延时微调部分,通过改变存储器读信号相对于写信号的位置,实现更精确的调整,完成的系统最小步进达到625ns,达到了设计要求。

所有设计文件采用原理图(顶层)和VHDL语言(底层)完成,在LATTICE的ispLEVER软件下编译并适配到两片MACH4-64/32A中,仿真后,下载到器件中去,经过实际系统测试并修改某些逻辑后设计完成。电路板是事先设计好的,MACH器件有强大的布线能力,保证了适配以及实际系统运行的成功。

结语

作为“调频同步广播”项目的关键技术之一,音频精确延时系统把卫星传输的音频信号,在不同接收地点进行精确和稳定的延时,补偿了由于各发射台经纬度不同造成的信号不同步,实现了真正意义上的同步广播。针对我国幅员辽阔,人口分散而频率资源匮乏的实际情况,该方案给出了一种较好的广播覆盖方法。此系统已用于国家广电总局提出的“村村通广播电视”工程,带来了良好的社会效益和经济效益。推而广之,通过增加逻辑规模和存储器容量,这种方法也可用于其他需要高质量音频延迟的场合。

举报

举报

举报

举报