LONWorks总线是由美国Echelon公司推出的一种现场总线技术,由于LonWorks控制网络的开放性、高速性、互操作性及其对现场环境的适应性,它已广泛应用于楼宇自动化、家庭自动化、保安系统、办公设备、交通运输、工业过程控制等行业。LON总线的现场节点间采用LonTalk协议。当工程师使用便携设备对现场节点进行检测或进行现场数据采集时,往往只能使用RS232串口。众所周知,RS232的传输速度最高只能达到9600kbps,这对实时性要求很高的现场数据采集来说远远不能满足要求。针对这一情况,笔者开发研制了LON总线的USB2.0接口卡。该卡提供的USB2.0接口使得数据的传输速度能提高到480Mbps.并且向下完全兼容流行的USBl.1协议。

1 USB2.0的主要特点

USB协议的2.0版本于2000年4月推出,支持以下3种速度模式:低速模式(low speed)1.5Mb/s;全速模式(full speedl 12Mb/s;高速模式(high speed)480Mb/s。它支持现存的所有US B设备.可以把USB1.1设备插入USB1.1的PC机接口,并且在电气上兼容USB1.1的连接线。

1.1 USB总线特点

◆数据传输速率高;

◆数据传输可靠;

◆同时挂接多个USB设备;

◆USB接口能为设备供电;

◆支持热插拔。

1.2 USB的新特性

USB还具有一些新的特性。如:实时性(可以实现和一个设备之间有效的实时通信)、动态性(可以实现接口间的动态切换)、联合性(不同的而又有相近特性的接口可以联台起来)和多能性(各个不同的接口可以使用不同的供电模式)。

2 LonWorks接口卡硬件设计

2.1 LonWorks接口卡通信原理及硬件结构

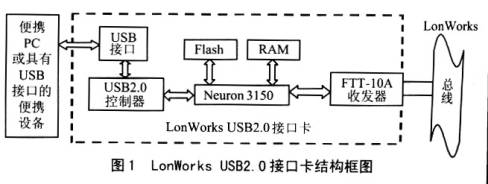

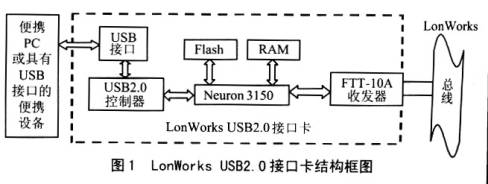

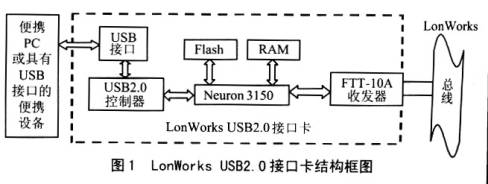

该接口卡的工作原理如下:接口卡由LON网接口模块和USB2.0接口模块组成,如图1所示,它采用双CPU技术,主CPU为USB2.0控制器CY7C68013内置的增强8051内核(该内核的运行速度是普通8051的5倍),主要作为协议的转换模块,用来完成USB2.0协议与LonTalk协议之间的转换,向上与便携PC机(或其它具有USB接口的便携设备)进行通信,向下与3150进行并口通信,辅CPU为TMPN3l50,主要起LON网接口的功能,作为通信协处理器使用,将从主CPU接收到的来自便携PC机(或其它具有USB接口的便携设备)的报文解析成Lontalk协议报文并通过Lonworks收发器传向LON网,或将从LON网上接收到的Lontalk协议报文转发给主CPU,再由主CPU传向便携PC机(或其它具有USB接口的便携设备)。51CPU与Neuron3150采用并行方式通信。Neuron芯片的11个I/O有34种可选工作模式,其中包括并行I/O方式,该方式数据的最大传送速率可达3.3Mbps。并口工作方式在数据传送速度方面的优势,使得Neuron芯片与51CPU完成大数据量的传送成为可能。它们之间的数据传输是通过运用“虚写令牌传递机制”实现的,拥有令牌的一方拥有对数据总线的写控制权。

2. 2 LonWOrks接口卡硬件电路设计

该接口卡中,USB2.O控制器采用Cypress公司推出的USB2.0控制器CY7C68013,它是USB2.0的完整解决方案。该芯片包括带8.5KB片上RAM的高速8051单片机、4KB FIFO存储器以及通用可编程接口(GPIF)、串行接口引擎(SIE)和USB2.O收发器。它无需外加芯片即可完成高速USB传输,性价比较高。智能串行接口引擎(SIE)执行所有基本的USB功能,将嵌入式MCU解放出来用于实现专用的功能,井保证其持续高性能的传输速率。通用可编程接口(GPIF)允许它“无胶粘接”,即可与任何ASIC或DSP进行连接,并且还支持所有通用总线标准,包括ATA、UTOPIA、EPP和PCMCIA。它完全适用于USB2.0,并向下兼容USB1.1。

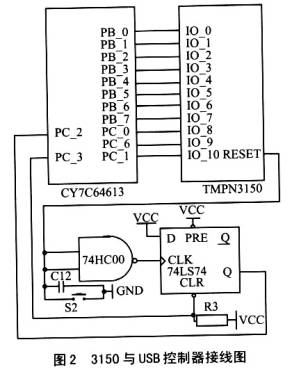

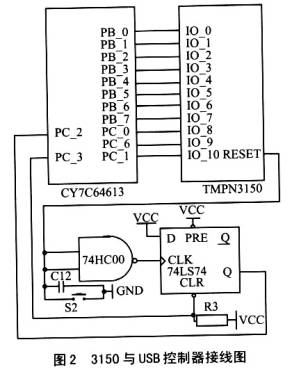

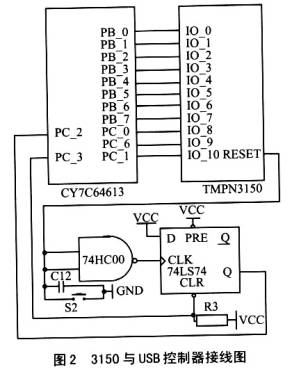

3150芯片选用Toshiba公司生产的TMPN3150。3150片内存储器的地址范围是E800H~FFFH,包括2KB的SRAM和512B的EEPROM。3150可以外接存储器,如RAM、ROM、EEPROM或Flash,其地址范围是0000H~7FFH。根据一般应用的性能和成本要求,3l50的外部存储器采用Flash和RAM。Flash选用IS61C256AH-15N,RAM选用AT29C512。61C256和29C512的地址范围通过逻辑门电路根据Neuron芯片的地址线和控制线E来确定。51与3l50采用3150的并口通信方式,将Neuron芯片的IO0~IO7作为8根数据线与51CPu的PB(PB0-PB7)口相连-108作为片选信号线e§)与51CPU的PCO口相连.IO9作为数据读/写信号线(R/W)与51CPU的PC6口(写信号)相连。IO10作为握手信号线(HS)与51CPU的PC1口相连。

为提高增加接口卡的可靠性及稳定性,本设计增加了一个锁存器,完成复位接口的功能。当3150芯片复位时,通过锁存器将复位信号传送给CY7C68013内置的8051处理器,8051接到复位信号自动复位,并马上清锁存器,其接线如图2所示。在并口通信中,8051与3150同步非常重要,要完成并口通信,8051首先要与3150达到同步且同步操作必须在3150复位时进行。8051只在初始化程序时才与3150进行同步操作。因此完成同步后,每当3l50由于误操作或错误运行而造成复位时,3150与8051将会失去同步,而8051无法检测到,从而造成并口通信失败。加入锁存器之后,8051就能检测到3150的复位信号并自动复位自己的程序,使得8051与3150再次达到同步。这将使适配器的可靠性和稳定性都得到加强。

Neuron芯片与LON网络介质的接口采用一种LonWorks自由拓扑型收发器FTT-IOA。FTT-IOA是一种变压器耦台收发器,可提供一个与双绞线的无极性接口,且支持网络的自由拓扑结构。网络通信介质采用最常用的双绞线。

2.3 接口卡的抗干扰设计

工业现场的环境一般来说较为恶劣.存在多种干扰。为保证通信的准确无误,延长硬件使用寿命,该适配器除采用通常的供电和接地抗干扰措施外,主要是要避免和消除来自网络介质的静电泄放(ESD)和电磁干扰(EMI),即主要针对FTT-IOA来设计抗干扰电路。

对于ESD,在印刷电路板(PCB)设计中应提供一个导入大地的通道.还要不致引起整个PCB电压的升降。具体采用火花放电隙和箝位二极管来实现。对于EMI,因为FTT-IOA对垂直杂散电磁场最不敏感,而对水平杂散电磁场最敏感。所以在PCB设计中应使FTT-IOA尽量远离水平杂散电磁场区域。对于不可避免的杂散电磁场,应使其相对于FTT-IOA垂直分布。

3 LOnWorks接口卡软件设计

3.1 Neuron芯片的编程语言——Neouron C

Neuron芯片有一套专门的开发语言——Neuron C。Neuron C派生于ANSI C,并增加了对I/O、事件处理、报文传送和分市式数据对象的支持,是开发Neuron芯片应用程序的重要工具。其语法扩展包括软件定时器、网络变量、显式报文、多任务调度、EEPROM变量和附加功能等。其中,显示报文的使用为LON节点间的通信及互操作提供了基础。通过对不同节点分配网络地址,即可实现节点之间的数据传递。也就是说,LON接口卡中的3150通过构造和解析报文实现了与LON网用户节点的通信。

3.2 CY7C6801 3的开发工具

Cypress公司对CY7C680 1 3提供了较为完备的开发套件CY3681。它包括带128脚CY7C68013的硬件开发板、相应的控制面板(Control panel)和GPIF代码自动生成软件(GPIFT001)。对于内核8051的开发采用Keil开发工具。

3.3 LonWorks接口卡的软件设计

该接口卡的程序包含两大部分:一是存储在CY7C68013中的USB驱动程序和与3150的并口通信程序:二是存储在3150外部Flash中的并口通信程序以及LonTalk协议转换程序。USB驱动程序在开发套件CY368 1中已有支持用户,只要调用即可。而与31 50的并口通信程序则采用Keil C51语言编写,并通过usB口下载到CY7C68013的8051内核中。3150外部Flash中的并口通信程序以及LonTalk协议转换程序采用Neuron C语言编写,并采用LonWorks开发工具——LonBuilder中的Neuron C编译器对程序进行编译,生成ROM映像文件,最后下载到片外Flash中。

在8051的并口通信程序中,需要模拟3150的并口通信从A方式。以下为并口通信程序中主要模块的C51程序,包括同步模块(sync—loop());握手模块(hndshkO);并口数据传送接收模块(pio read();pio write(void));令牌传递模块(pass token())。

void sync-loop(void)

{unsigned char rb;

do{RW=0;hndshk();PB=CMD RESYNC;CS=0;CS=I;hndshk();

PB=EOM;CS=0;CS=1;hndshk();PB=0xff;RW=I;CS=0;rb=PB;

CS=I;}while(rb!=CMD ACKSYNC);token=MASTER;}

void hndshk(void)

{while((hs=INTO)==1);}

vo id pio_read(void)

{unsigned char cmd;unsigned char i;

PB=0xff;hndshk();RW=1;cmd=PB;CS=0;CS=1;

if(cmd==CMD—XFER){hndshk();pio.1en=PB;CS=0;CS=1;}

else pio.1en=o=pass—token();}

void pio-write(void)

{unsigned char sd;

hndshk();RW=0;PB=CMD—XFER;CS=0;CS=1;hndshk0;PB=pio.

1en;CS=0;CS=1:

for(sd=0;sd

void pass_token(void)

{ifftoken==MASTER){hndshk();RW=0;PB=EOM;CS=0;CS=1:

token=SLAVE;}

else toke;}

根据硬件设计,将3150芯片的I/O定义为并行(parallel)I/O对象类型。定义并行I/O对象的Neuron C源代码为IO 0 parallel slave P BUS,其中,P BUS为所定义的I/O对象名称。Neuron将从并口得到的报文解析,再利用Neuron C的消息传送机制,将解析的消息传送给适配器下层的应用节点。读取数据的Neuron C函数为io_in(),其格式如下:io in(P BUS,addressl);

其中,P_BUS为并口IO对象名称,addressl为接收并口数据的地址。发消息的Neuron C函数为msg send()。

值得注意的是,Neuron芯片的应用CPU在执行该io_in()函数时会处于等待状态,也就是说等待数据时应用CPU不能处理其它I/O事件、定时器终止、网络变量更新或报文到达事件。如果2 0字符时间内尚没有接收到数据,则可能使Wat Chdog定时器产生超时错。在10MHz的输入时钟下,watchdog的超时时间是0.84s(该时间随输入时钟而改变)。通常情况下,调度程序(scheduler)会周期性地对watchdog定时器进行复位,但当程序处理一个较长的任务(task)如io in()时,则有可能终止watChdog定时器,这将导致整个节点的复位。为避免产生这种情况,同时使程序尽可能多地接收到达的数据,本节点程序在接收数据这个任务中周期性地调用函数watchdog update()。

4 结论

本文所设计接口卡的主要目的是为带有USB接口的便携设备进行现场数据测量和现场监测提供高速、安全的通信接口。解决了令工程师头痛的便携设备与现场设备采用通用串口通信时传输速率低、经常掉线、连接不可靠的问题。

LONWorks总线是由美国Echelon公司推出的一种现场总线技术,由于LonWorks控制网络的开放性、高速性、互操作性及其对现场环境的适应性,它已广泛应用于楼宇自动化、家庭自动化、保安系统、办公设备、交通运输、工业过程控制等行业。LON总线的现场节点间采用LonTalk协议。当工程师使用便携设备对现场节点进行检测或进行现场数据采集时,往往只能使用RS232串口。众所周知,RS232的传输速度最高只能达到9600kbps,这对实时性要求很高的现场数据采集来说远远不能满足要求。针对这一情况,笔者开发研制了LON总线的USB2.0接口卡。该卡提供的USB2.0接口使得数据的传输速度能提高到480Mbps.并且向下完全兼容流行的USBl.1协议。

1 USB2.0的主要特点

USB协议的2.0版本于2000年4月推出,支持以下3种速度模式:低速模式(low speed)1.5Mb/s;全速模式(full speedl 12Mb/s;高速模式(high speed)480Mb/s。它支持现存的所有US B设备.可以把USB1.1设备插入USB1.1的PC机接口,并且在电气上兼容USB1.1的连接线。

1.1 USB总线特点

◆数据传输速率高;

◆数据传输可靠;

◆同时挂接多个USB设备;

◆USB接口能为设备供电;

◆支持热插拔。

1.2 USB的新特性

USB还具有一些新的特性。如:实时性(可以实现和一个设备之间有效的实时通信)、动态性(可以实现接口间的动态切换)、联合性(不同的而又有相近特性的接口可以联台起来)和多能性(各个不同的接口可以使用不同的供电模式)。

2 LonWorks接口卡硬件设计

2.1 LonWorks接口卡通信原理及硬件结构

该接口卡的工作原理如下:接口卡由LON网接口模块和USB2.0接口模块组成,如图1所示,它采用双CPU技术,主CPU为USB2.0控制器CY7C68013内置的增强8051内核(该内核的运行速度是普通8051的5倍),主要作为协议的转换模块,用来完成USB2.0协议与LonTalk协议之间的转换,向上与便携PC机(或其它具有USB接口的便携设备)进行通信,向下与3150进行并口通信,辅CPU为TMPN3l50,主要起LON网接口的功能,作为通信协处理器使用,将从主CPU接收到的来自便携PC机(或其它具有USB接口的便携设备)的报文解析成Lontalk协议报文并通过Lonworks收发器传向LON网,或将从LON网上接收到的Lontalk协议报文转发给主CPU,再由主CPU传向便携PC机(或其它具有USB接口的便携设备)。51CPU与Neuron3150采用并行方式通信。Neuron芯片的11个I/O有34种可选工作模式,其中包括并行I/O方式,该方式数据的最大传送速率可达3.3Mbps。并口工作方式在数据传送速度方面的优势,使得Neuron芯片与51CPU完成大数据量的传送成为可能。它们之间的数据传输是通过运用“虚写令牌传递机制”实现的,拥有令牌的一方拥有对数据总线的写控制权。

2. 2 LonWOrks接口卡硬件电路设计

该接口卡中,USB2.O控制器采用Cypress公司推出的USB2.0控制器CY7C68013,它是USB2.0的完整解决方案。该芯片包括带8.5KB片上RAM的高速8051单片机、4KB FIFO存储器以及通用可编程接口(GPIF)、串行接口引擎(SIE)和USB2.O收发器。它无需外加芯片即可完成高速USB传输,性价比较高。智能串行接口引擎(SIE)执行所有基本的USB功能,将嵌入式MCU解放出来用于实现专用的功能,井保证其持续高性能的传输速率。通用可编程接口(GPIF)允许它“无胶粘接”,即可与任何ASIC或DSP进行连接,并且还支持所有通用总线标准,包括ATA、UTOPIA、EPP和PCMCIA。它完全适用于USB2.0,并向下兼容USB1.1。

3150芯片选用Toshiba公司生产的TMPN3150。3150片内存储器的地址范围是E800H~FFFH,包括2KB的SRAM和512B的EEPROM。3150可以外接存储器,如RAM、ROM、EEPROM或Flash,其地址范围是0000H~7FFH。根据一般应用的性能和成本要求,3l50的外部存储器采用Flash和RAM。Flash选用IS61C256AH-15N,RAM选用AT29C512。61C256和29C512的地址范围通过逻辑门电路根据Neuron芯片的地址线和控制线E来确定。51与3l50采用3150的并口通信方式,将Neuron芯片的IO0~IO7作为8根数据线与51CPu的PB(PB0-PB7)口相连-108作为片选信号线e§)与51CPU的PCO口相连.IO9作为数据读/写信号线(R/W)与51CPU的PC6口(写信号)相连。IO10作为握手信号线(HS)与51CPU的PC1口相连。

为提高增加接口卡的可靠性及稳定性,本设计增加了一个锁存器,完成复位接口的功能。当3150芯片复位时,通过锁存器将复位信号传送给CY7C68013内置的8051处理器,8051接到复位信号自动复位,并马上清锁存器,其接线如图2所示。在并口通信中,8051与3150同步非常重要,要完成并口通信,8051首先要与3150达到同步且同步操作必须在3150复位时进行。8051只在初始化程序时才与3150进行同步操作。因此完成同步后,每当3l50由于误操作或错误运行而造成复位时,3150与8051将会失去同步,而8051无法检测到,从而造成并口通信失败。加入锁存器之后,8051就能检测到3150的复位信号并自动复位自己的程序,使得8051与3150再次达到同步。这将使适配器的可靠性和稳定性都得到加强。

Neuron芯片与LON网络介质的接口采用一种LonWorks自由拓扑型收发器FTT-IOA。FTT-IOA是一种变压器耦台收发器,可提供一个与双绞线的无极性接口,且支持网络的自由拓扑结构。网络通信介质采用最常用的双绞线。

2.3 接口卡的抗干扰设计

工业现场的环境一般来说较为恶劣.存在多种干扰。为保证通信的准确无误,延长硬件使用寿命,该适配器除采用通常的供电和接地抗干扰措施外,主要是要避免和消除来自网络介质的静电泄放(ESD)和电磁干扰(EMI),即主要针对FTT-IOA来设计抗干扰电路。

对于ESD,在印刷电路板(PCB)设计中应提供一个导入大地的通道.还要不致引起整个PCB电压的升降。具体采用火花放电隙和箝位二极管来实现。对于EMI,因为FTT-IOA对垂直杂散电磁场最不敏感,而对水平杂散电磁场最敏感。所以在PCB设计中应使FTT-IOA尽量远离水平杂散电磁场区域。对于不可避免的杂散电磁场,应使其相对于FTT-IOA垂直分布。

3 LOnWorks接口卡软件设计

3.1 Neuron芯片的编程语言——Neouron C

Neuron芯片有一套专门的开发语言——Neuron C。Neuron C派生于ANSI C,并增加了对I/O、事件处理、报文传送和分市式数据对象的支持,是开发Neuron芯片应用程序的重要工具。其语法扩展包括软件定时器、网络变量、显式报文、多任务调度、EEPROM变量和附加功能等。其中,显示报文的使用为LON节点间的通信及互操作提供了基础。通过对不同节点分配网络地址,即可实现节点之间的数据传递。也就是说,LON接口卡中的3150通过构造和解析报文实现了与LON网用户节点的通信。

3.2 CY7C6801 3的开发工具

Cypress公司对CY7C680 1 3提供了较为完备的开发套件CY3681。它包括带128脚CY7C68013的硬件开发板、相应的控制面板(Control panel)和GPIF代码自动生成软件(GPIFT001)。对于内核8051的开发采用Keil开发工具。

3.3 LonWorks接口卡的软件设计

该接口卡的程序包含两大部分:一是存储在CY7C68013中的USB驱动程序和与3150的并口通信程序:二是存储在3150外部Flash中的并口通信程序以及LonTalk协议转换程序。USB驱动程序在开发套件CY368 1中已有支持用户,只要调用即可。而与31 50的并口通信程序则采用Keil C51语言编写,并通过usB口下载到CY7C68013的8051内核中。3150外部Flash中的并口通信程序以及LonTalk协议转换程序采用Neuron C语言编写,并采用LonWorks开发工具——LonBuilder中的Neuron C编译器对程序进行编译,生成ROM映像文件,最后下载到片外Flash中。

在8051的并口通信程序中,需要模拟3150的并口通信从A方式。以下为并口通信程序中主要模块的C51程序,包括同步模块(sync—loop());握手模块(hndshkO);并口数据传送接收模块(pio read();pio write(void));令牌传递模块(pass token())。

void sync-loop(void)

{unsigned char rb;

do{RW=0;hndshk();PB=CMD RESYNC;CS=0;CS=I;hndshk();

PB=EOM;CS=0;CS=1;hndshk();PB=0xff;RW=I;CS=0;rb=PB;

CS=I;}while(rb!=CMD ACKSYNC);token=MASTER;}

void hndshk(void)

{while((hs=INTO)==1);}

vo id pio_read(void)

{unsigned char cmd;unsigned char i;

PB=0xff;hndshk();RW=1;cmd=PB;CS=0;CS=1;

if(cmd==CMD—XFER){hndshk();pio.1en=PB;CS=0;CS=1;}

else pio.1en=o=pass—token();}

void pio-write(void)

{unsigned char sd;

hndshk();RW=0;PB=CMD—XFER;CS=0;CS=1;hndshk0;PB=pio.

1en;CS=0;CS=1:

for(sd=0;sd

void pass_token(void)

{ifftoken==MASTER){hndshk();RW=0;PB=EOM;CS=0;CS=1:

token=SLAVE;}

else toke;}

根据硬件设计,将3150芯片的I/O定义为并行(parallel)I/O对象类型。定义并行I/O对象的Neuron C源代码为IO 0 parallel slave P BUS,其中,P BUS为所定义的I/O对象名称。Neuron将从并口得到的报文解析,再利用Neuron C的消息传送机制,将解析的消息传送给适配器下层的应用节点。读取数据的Neuron C函数为io_in(),其格式如下:io in(P BUS,addressl);

其中,P_BUS为并口IO对象名称,addressl为接收并口数据的地址。发消息的Neuron C函数为msg send()。

值得注意的是,Neuron芯片的应用CPU在执行该io_in()函数时会处于等待状态,也就是说等待数据时应用CPU不能处理其它I/O事件、定时器终止、网络变量更新或报文到达事件。如果2 0字符时间内尚没有接收到数据,则可能使Wat Chdog定时器产生超时错。在10MHz的输入时钟下,watchdog的超时时间是0.84s(该时间随输入时钟而改变)。通常情况下,调度程序(scheduler)会周期性地对watchdog定时器进行复位,但当程序处理一个较长的任务(task)如io in()时,则有可能终止watChdog定时器,这将导致整个节点的复位。为避免产生这种情况,同时使程序尽可能多地接收到达的数据,本节点程序在接收数据这个任务中周期性地调用函数watchdog update()。

4 结论

本文所设计接口卡的主要目的是为带有USB接口的便携设备进行现场数据测量和现场监测提供高速、安全的通信接口。解决了令工程师头痛的便携设备与现场设备采用通用串口通信时传输速率低、经常掉线、连接不可靠的问题。

举报

举报

举报

举报