汽车制造业在超高频(UHF)频段的应用要求晶体管不但具有良好的射频性能,还要很好鲁棒性。英飞凌公司生产的BFP460正是一款对应于这种应用的通用的晶体管,它是静电释放(ESD)增强型器件。它受益于具有23GHz转换频率的双极硅加工技术,能够安全地承受任意一对引脚间1500V的ESD脉冲。

这种新型器件的有效性将在一种超高频低噪声放大器LNA中得以展示,这种放大器对在汽车制造业中使用非常理想。

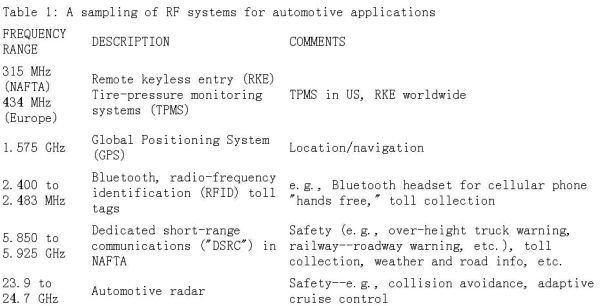

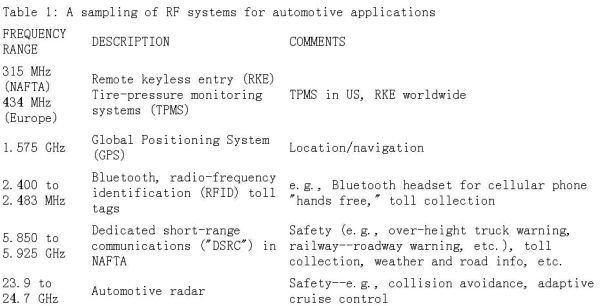

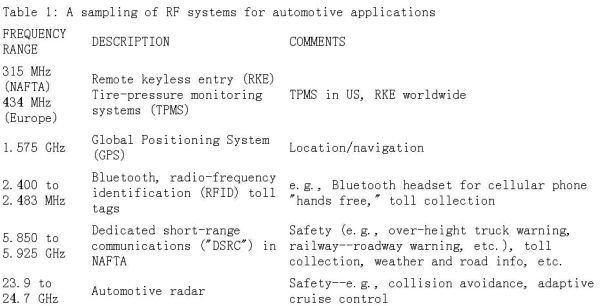

现在各种各样的汽车系统都利用了RF技术,包括无键遥控输入(RKE)、GPS、卫星数字式声频无线电服务(SDARS)和轮胎压力监控系统(TPMS)。这些系统中的每一个都要求射频模块具有成本低、耐用度/强度高的优良性能(表1)。

由于RF器件按照越小的尺寸为越高的频率所使用的这一规定,所以当击穿电压下降(从典型值50 V 到3 V左右)的时候,它们有呈现出更高的电流密度(在一个典型的晶体管的工作点上大约3mA/μm2或300,000A/cm2)的趋势。

击穿电压和最适宜的电流密度是由集电极的厚度和所掺杂质决定的。对于一个高转换频率,集电极必须要薄。为了得到高增益,所有内部寄生电容必须要小,这是横向尺寸规格缩小的推动因素,但是同时也使晶体管的ESD更容易损坏。

严格的晶体管ESD损坏机制研究表明在器件ESD的强度上仍有提升的空间。分立的BFP460晶体管加入了一些这样的研究结果,目的是承受当达到23 GHz的截止频率时1500V的人体模型(HBM)脉冲,在1.8 GHz时有17.5 dB的最大稳定增益和1.1 dB的最小噪声数字。

最广泛被使用的ESD 测试标准是HBM,详见MIL STD 883D 。在这个标准中,一个100pF的电容被参考电压VREF充电。随后参考电压被断开,在测试中,当当电容经过一系列的1,500Ω电阻接到待测器件上的时候又会被充电。这个电路装置可以被看成电流源。

当参考电压为100 V时,被用来作为对ESD来说具有器件体积小和灵敏度更高的低噪声晶体管,而当电压达到5,000 V时,则被用作较旧式的,较低性能的大体积晶体管。DUT被认为是一种评定特殊ESD等级的方式,即在电压值为VREF的时候,它能经受得住这些测试的考验,且其性能没有下降,也没有出现故障。尽管ESD测试如今也可能用到晶片上芯片等级的评定上,但作为代表的是其已在封装器件中得以使用。作为一种对人体标准可供选择的方法,传输线脉冲测量(TLP)经常被用来估计ESD的容限。

一个ESD 脉冲最好被理解成器件内部的一个急剧电流波动。对于第一阶的近似值来说,假设在器件经历这个电流波动期间整个事件发生的非常快以至于热量都来不及传播和消耗的话,它就是有效的。结果,由ESD感应电流波动引起的温度上升与电流密度的平方成正比,而且电流密度存在一个极限值,超过这个值实际上就会使器件中的硅熔化。

事实上,硅材料的融化会导致器件故障。由于电流密度是导致器件故障的关键一条,所以具有较大发射极边缘面或面积的晶体管就比小一些的更耐用。与普遍看法相反,在集电极-发射极之间的击穿电压VCEO与其阻抗和ESD损坏并没有相互关系。

为了提高耐用性,RF集成电路设计师们已经开发了ESD内部保护结构,用来帮助保护ESD灵敏的RF输入和输出端免受有害ESD事件的影响。但比较遗憾的是这些保护结构也在RF端加入了寄生电容,电感和损耗,因此导致其性能下降,同时也使得这种结构不适合与分立器件(对性能要求更高)一起使用。

在一个像双极晶体管这样的三引脚器件中,经由器件的任意两个引脚一共有六种可能的方式来应用ESD 脉冲,而未使用的器件引脚仍然是开路(未连接)。通常当ESD 脉冲反方向接在PN结两端的时候晶体管最容易损坏。而依赖于特殊半导体工艺技术,集电极-基极结通常是微弱的连接在RF晶体管上。

在发生ESD期间,基极-集电极的空间电荷被压入高度掺杂质的底层(或RF IC中的隐埋层)。这种情形与所谓的Kirk效应非常相似。几乎整个晶体管的电压都加在了集电极地层,增强了这个区域的磁场强度(集电极区域的自由电子密度已经超过了掺杂密度)。因为集电极的自由电荷必须被极性相反的电荷补偿,它们能够中和的唯一的区域就是高度掺杂层(或隐埋层)。就硅而言,如果这个磁场达到了大约3×105V/cm的内部击穿磁场强度的时候,那么大量的撞击离子就出现了。形成了更多的自由载体(电子和空穴)并发生逃逸,同时外部电压击穿。在VCEO突变后的这种作用在参考1中被称为“二次激变”。

ESD脉冲包含的大多数能量都被释放在磁场强度最高的地方,这一点增加了局部器件温度。由于具有内在传导机制,这反而又增加了自由载体的数量。借助于一个正反馈机制这个过程就这样周而复始的继续下去,结果,电流会逐渐聚集一个越来越小的点上,随后硅材料会被融化并烧毁。

在某种程度上,电流路径上一系列分布阻抗能够帮助避免ESD感应波动电流的聚集。

一系列的阻抗使得波动电流呈分布状态,并能帮助避免随后的破坏发生。晶体管单元的细心设计也能帮助避免此类破坏作用。例如,晶体残缺不完整,边缘过于锋利,拐角的断开都可以导致局部电场强度增加,这些缺陷都是应该被避免的。

一个减少ESD感应磁场的直接方式是通过选择降低层中掺杂质的密度,用来分散相反极性的电荷更加深入的进入层内。可遗憾的是,这种方法影响了层阻抗(和RF性能)。一种更好的方法是在底层和集电极区域之间插入一个过渡层。这个过渡区域的掺杂质密集度要比活跃的集电极区域高,但是要比底层的低;尽管如此,它必须要足够高到使这个过渡区在正常的工作中可以被当作一个层(图1)。这种设计方法被运用到了BFP460中用来把ESD的容限从300V提升到1500V(具有64um2发射极区域的封装器件)。

仿真性能

利用DESSIS CAE仿真器可以获取更多ESD的机制。过程仿真器DIOS作为基本射频晶体管单元分析的第一步,可用在两种配置下,即带有或者不带缓冲层。在ESD仿真中,要为物理模型设计一个HBM电路,且电容器的放电可以在时域内计算出来。由于反向脉冲负载下的基极-集电极的性能很差,因而常用来做分析。

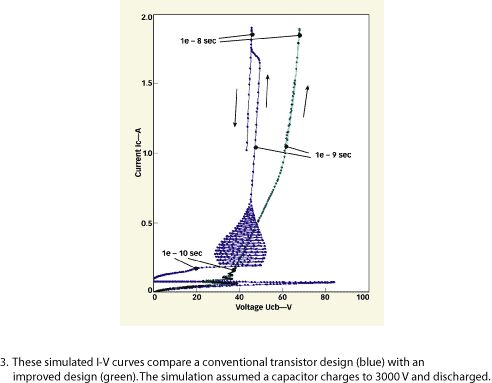

参考电容可以达到3000V并且最高电流密度可达到12.6 mA/μm2(图2)。对于普通的晶体管,场的异常高区域通常在集电极衬底层边缘处,然而可以利用缓冲区来有效的降低它,这是由于ESD电流中的自由电子的补偿作用分布的更深更广。而且在内部基极连接处,很高的电流密度也会导致高能电场的产生。通过对很多案例分析发现,该处的硅已经融化了。

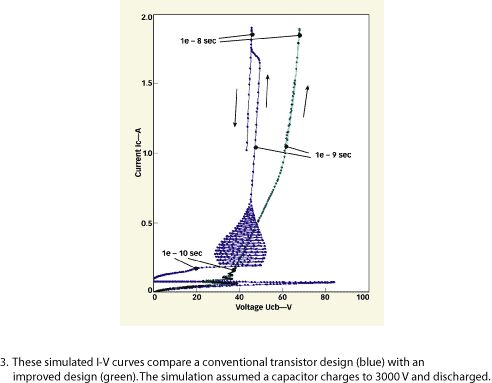

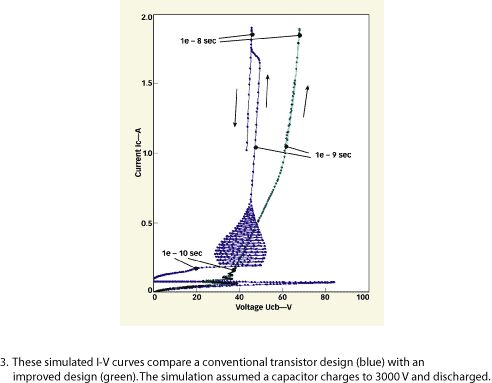

图3中的电流-电压(I-V)曲线显示了缓冲层的作用。曲线是在很多时间段上绘制的,利用箭头合标记来标明时间的发展方向。雪崩效应和电压崩溃的并发造成了曲线前端的不稳定,这是由自由空穴引起的但不影响ESD分析。带有缓冲层的器件具有负斜率的I-V特性:如果雪崩效应在一点变得强烈,该处的电压会上升。如果电压稳定并均衡,就不会出现电流拥挤的现象。

在分散的射频晶体管的生产向英飞凌的新流程“自排列双极性方法”的过渡中,有机会对BFP460做新的设计。在新流程中,发射极是利用对n极层的沉积来取代以前掺杂砷的方法。该方法严格控制生产过程的参数,并在参数的小范围内实现对晶体管高容量运行的控制。

例如平板射频晶体管的直流电流增益(hFE)通常在一个很宽的范围内分布,但在BFP460的生产中,却在很小的范围内(100到150之间)可控。

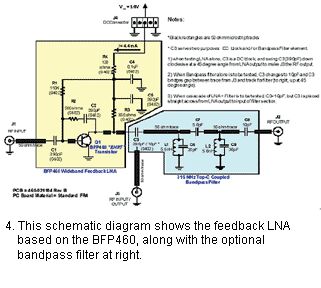

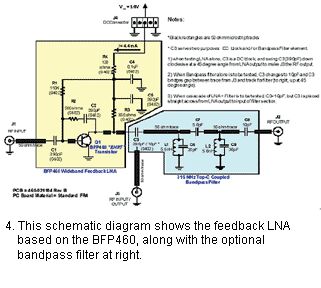

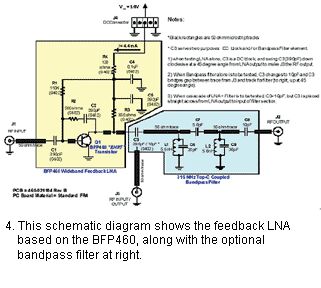

尽管ESD增强的晶体管的适用范围很广(图4),但在超高频的宽带反馈的LNA(低噪声放大器)中仍采用BFP460。这种特殊的LNA可在315和434MHz上增强RKE和TPMS的射频芯片接收器的范围和敏感度,它由九部分组成,其中包括BFP460晶体管。为了降低成本,用电阻和电容来替代贴片电感(感应器)。其应用板上带有一种可选的低功耗极总带通滤波器,中心频率设为315MHz,并可重设为434MHz,可以用来降低通带外被过滤掉的信号对RKE接收器的影响。应用板支持LNA以及滤波器的自测试,或者二者同时测试。

LNA可以无条件的稳定,并在300到1000MHz上具有良好的回波损失、增益以及噪声等有良好的性能。它可以工作在315、434或者900MHz的ISM带宽之内,且无需更改任何设置。

汽车制造业在超高频(UHF)频段的应用要求晶体管不但具有良好的射频性能,还要很好鲁棒性。英飞凌公司生产的BFP460正是一款对应于这种应用的通用的晶体管,它是静电释放(ESD)增强型器件。它受益于具有23GHz转换频率的双极硅加工技术,能够安全地承受任意一对引脚间1500V的ESD脉冲。

这种新型器件的有效性将在一种超高频低噪声放大器LNA中得以展示,这种放大器对在汽车制造业中使用非常理想。

现在各种各样的汽车系统都利用了RF技术,包括无键遥控输入(RKE)、GPS、卫星数字式声频无线电服务(SDARS)和轮胎压力监控系统(TPMS)。这些系统中的每一个都要求射频模块具有成本低、耐用度/强度高的优良性能(表1)。

由于RF器件按照越小的尺寸为越高的频率所使用的这一规定,所以当击穿电压下降(从典型值50 V 到3 V左右)的时候,它们有呈现出更高的电流密度(在一个典型的晶体管的工作点上大约3mA/μm2或300,000A/cm2)的趋势。

击穿电压和最适宜的电流密度是由集电极的厚度和所掺杂质决定的。对于一个高转换频率,集电极必须要薄。为了得到高增益,所有内部寄生电容必须要小,这是横向尺寸规格缩小的推动因素,但是同时也使晶体管的ESD更容易损坏。

严格的晶体管ESD损坏机制研究表明在器件ESD的强度上仍有提升的空间。分立的BFP460晶体管加入了一些这样的研究结果,目的是承受当达到23 GHz的截止频率时1500V的人体模型(HBM)脉冲,在1.8 GHz时有17.5 dB的最大稳定增益和1.1 dB的最小噪声数字。

最广泛被使用的ESD 测试标准是HBM,详见MIL STD 883D 。在这个标准中,一个100pF的电容被参考电压VREF充电。随后参考电压被断开,在测试中,当当电容经过一系列的1,500Ω电阻接到待测器件上的时候又会被充电。这个电路装置可以被看成电流源。

当参考电压为100 V时,被用来作为对ESD来说具有器件体积小和灵敏度更高的低噪声晶体管,而当电压达到5,000 V时,则被用作较旧式的,较低性能的大体积晶体管。DUT被认为是一种评定特殊ESD等级的方式,即在电压值为VREF的时候,它能经受得住这些测试的考验,且其性能没有下降,也没有出现故障。尽管ESD测试如今也可能用到晶片上芯片等级的评定上,但作为代表的是其已在封装器件中得以使用。作为一种对人体标准可供选择的方法,传输线脉冲测量(TLP)经常被用来估计ESD的容限。

一个ESD 脉冲最好被理解成器件内部的一个急剧电流波动。对于第一阶的近似值来说,假设在器件经历这个电流波动期间整个事件发生的非常快以至于热量都来不及传播和消耗的话,它就是有效的。结果,由ESD感应电流波动引起的温度上升与电流密度的平方成正比,而且电流密度存在一个极限值,超过这个值实际上就会使器件中的硅熔化。

事实上,硅材料的融化会导致器件故障。由于电流密度是导致器件故障的关键一条,所以具有较大发射极边缘面或面积的晶体管就比小一些的更耐用。与普遍看法相反,在集电极-发射极之间的击穿电压VCEO与其阻抗和ESD损坏并没有相互关系。

为了提高耐用性,RF集成电路设计师们已经开发了ESD内部保护结构,用来帮助保护ESD灵敏的RF输入和输出端免受有害ESD事件的影响。但比较遗憾的是这些保护结构也在RF端加入了寄生电容,电感和损耗,因此导致其性能下降,同时也使得这种结构不适合与分立器件(对性能要求更高)一起使用。

在一个像双极晶体管这样的三引脚器件中,经由器件的任意两个引脚一共有六种可能的方式来应用ESD 脉冲,而未使用的器件引脚仍然是开路(未连接)。通常当ESD 脉冲反方向接在PN结两端的时候晶体管最容易损坏。而依赖于特殊半导体工艺技术,集电极-基极结通常是微弱的连接在RF晶体管上。

在发生ESD期间,基极-集电极的空间电荷被压入高度掺杂质的底层(或RF IC中的隐埋层)。这种情形与所谓的Kirk效应非常相似。几乎整个晶体管的电压都加在了集电极地层,增强了这个区域的磁场强度(集电极区域的自由电子密度已经超过了掺杂密度)。因为集电极的自由电荷必须被极性相反的电荷补偿,它们能够中和的唯一的区域就是高度掺杂层(或隐埋层)。就硅而言,如果这个磁场达到了大约3×105V/cm的内部击穿磁场强度的时候,那么大量的撞击离子就出现了。形成了更多的自由载体(电子和空穴)并发生逃逸,同时外部电压击穿。在VCEO突变后的这种作用在参考1中被称为“二次激变”。

ESD脉冲包含的大多数能量都被释放在磁场强度最高的地方,这一点增加了局部器件温度。由于具有内在传导机制,这反而又增加了自由载体的数量。借助于一个正反馈机制这个过程就这样周而复始的继续下去,结果,电流会逐渐聚集一个越来越小的点上,随后硅材料会被融化并烧毁。

在某种程度上,电流路径上一系列分布阻抗能够帮助避免ESD感应波动电流的聚集。

一系列的阻抗使得波动电流呈分布状态,并能帮助避免随后的破坏发生。晶体管单元的细心设计也能帮助避免此类破坏作用。例如,晶体残缺不完整,边缘过于锋利,拐角的断开都可以导致局部电场强度增加,这些缺陷都是应该被避免的。

一个减少ESD感应磁场的直接方式是通过选择降低层中掺杂质的密度,用来分散相反极性的电荷更加深入的进入层内。可遗憾的是,这种方法影响了层阻抗(和RF性能)。一种更好的方法是在底层和集电极区域之间插入一个过渡层。这个过渡区域的掺杂质密集度要比活跃的集电极区域高,但是要比底层的低;尽管如此,它必须要足够高到使这个过渡区在正常的工作中可以被当作一个层(图1)。这种设计方法被运用到了BFP460中用来把ESD的容限从300V提升到1500V(具有64um2发射极区域的封装器件)。

仿真性能

利用DESSIS CAE仿真器可以获取更多ESD的机制。过程仿真器DIOS作为基本射频晶体管单元分析的第一步,可用在两种配置下,即带有或者不带缓冲层。在ESD仿真中,要为物理模型设计一个HBM电路,且电容器的放电可以在时域内计算出来。由于反向脉冲负载下的基极-集电极的性能很差,因而常用来做分析。

参考电容可以达到3000V并且最高电流密度可达到12.6 mA/μm2(图2)。对于普通的晶体管,场的异常高区域通常在集电极衬底层边缘处,然而可以利用缓冲区来有效的降低它,这是由于ESD电流中的自由电子的补偿作用分布的更深更广。而且在内部基极连接处,很高的电流密度也会导致高能电场的产生。通过对很多案例分析发现,该处的硅已经融化了。

图3中的电流-电压(I-V)曲线显示了缓冲层的作用。曲线是在很多时间段上绘制的,利用箭头合标记来标明时间的发展方向。雪崩效应和电压崩溃的并发造成了曲线前端的不稳定,这是由自由空穴引起的但不影响ESD分析。带有缓冲层的器件具有负斜率的I-V特性:如果雪崩效应在一点变得强烈,该处的电压会上升。如果电压稳定并均衡,就不会出现电流拥挤的现象。

在分散的射频晶体管的生产向英飞凌的新流程“自排列双极性方法”的过渡中,有机会对BFP460做新的设计。在新流程中,发射极是利用对n极层的沉积来取代以前掺杂砷的方法。该方法严格控制生产过程的参数,并在参数的小范围内实现对晶体管高容量运行的控制。

例如平板射频晶体管的直流电流增益(hFE)通常在一个很宽的范围内分布,但在BFP460的生产中,却在很小的范围内(100到150之间)可控。

尽管ESD增强的晶体管的适用范围很广(图4),但在超高频的宽带反馈的LNA(低噪声放大器)中仍采用BFP460。这种特殊的LNA可在315和434MHz上增强RKE和TPMS的射频芯片接收器的范围和敏感度,它由九部分组成,其中包括BFP460晶体管。为了降低成本,用电阻和电容来替代贴片电感(感应器)。其应用板上带有一种可选的低功耗极总带通滤波器,中心频率设为315MHz,并可重设为434MHz,可以用来降低通带外被过滤掉的信号对RKE接收器的影响。应用板支持LNA以及滤波器的自测试,或者二者同时测试。

LNA可以无条件的稳定,并在300到1000MHz上具有良好的回波损失、增益以及噪声等有良好的性能。它可以工作在315、434或者900MHz的ISM带宽之内,且无需更改任何设置。

举报

举报

举报

举报