1 引言

随着EDA技术的发展,使用硬件语言设计可编程逻辑器件(PLD)/现场可编程门阵列(FPGA)成为一种趋势。FPGA是一种将门阵列的通用结构与PLD的现场可编程特性结合为一体的新型器件,具有集成度高、通用性好、设计灵活、编程方便、产品上市快等诸多优点。美国Xilinx公司于1985年领先推出了FPGA。目前市场上应用较广泛的FPGA产品当数Xilinx公司的Spartan和Virtex系列及Al-tera公司的ACEX和APEX系列。

目前最主要的硬件描述语言是VHDL和Ver-ilog HDL。VHDL发展的较早,语法严格,而VerilogHDL是在C语言的基础上发展起来的硬件描述语言,语法较自由。在工程应用尤其是在有关控制电路的设计中,用VHDL硬件描述语言设计FPGA经常会遇到以下三个问题:实现等占空比、非等占空比整数分频的分频电路;在时钟控制下对同步脉冲信号任意时间量的延迟;使用VHDL语言进行双向电路的设计。

2 常见问题

2.1 分频电路

分频电路是数字系统设计中的基本电路。在硬件电路设计中,时钟信号是最重要的信号之一,经常需要对较高频率的时钟进行分频操作,得到较低频率的时钟信号。分频电路一般分为三种:

第一种是任意占空比的偶数分频及非等占空比的奇数分频,通常由计数器或计数器的级联来完成。

第二种是等占空比的奇数分频电路。要实现占空比为50%的M=2N+1分频电路,本文采用计数器和1个或门来实现。

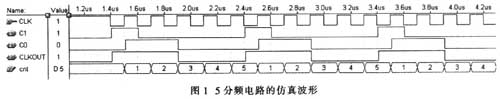

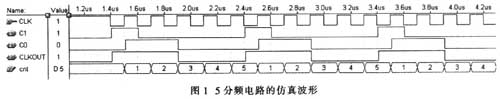

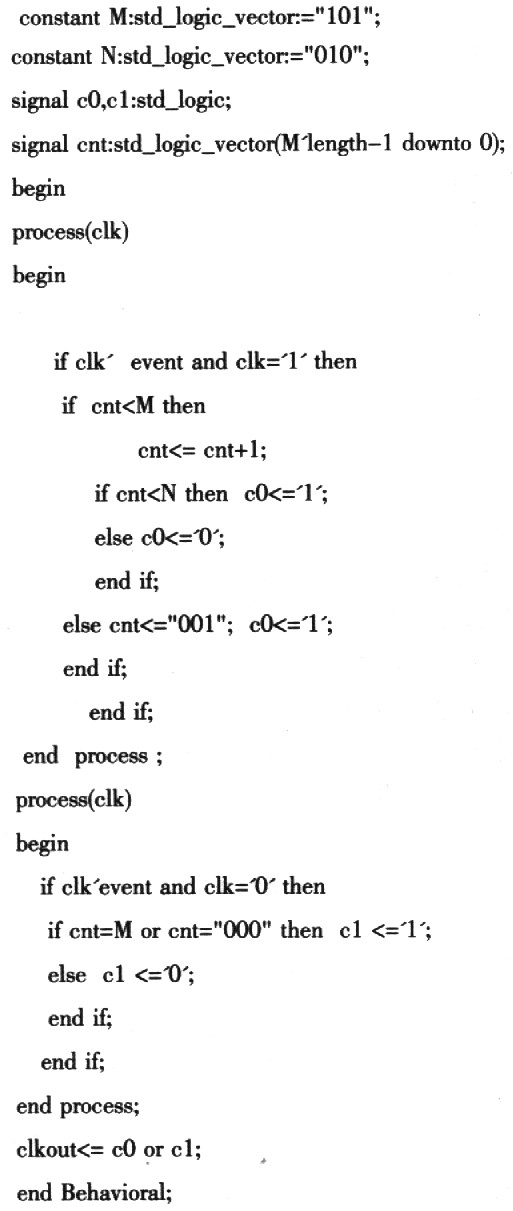

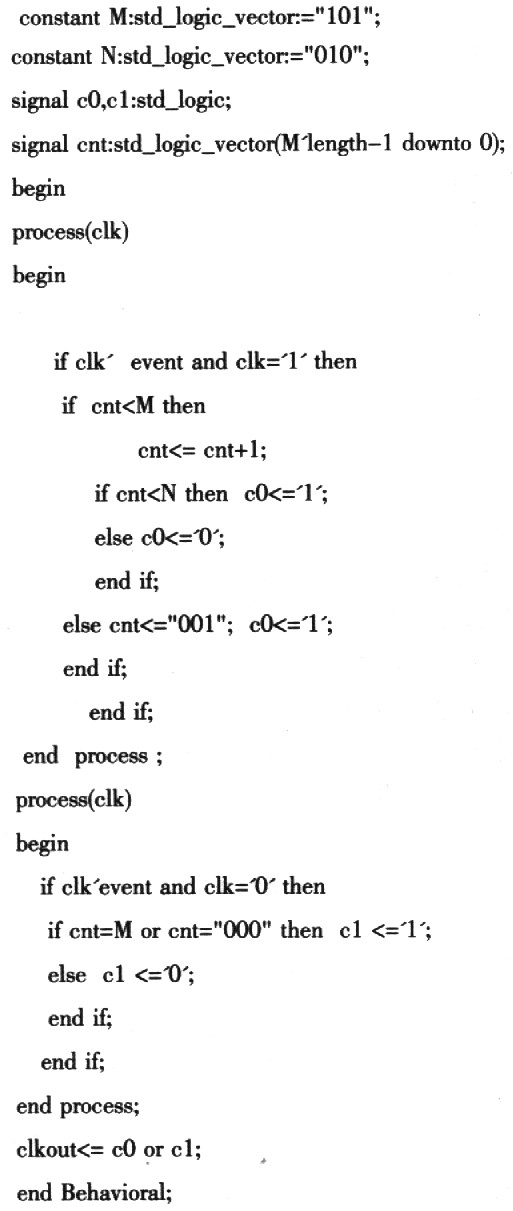

利用时钟的上升沿计数,设计一个模M的计数器:下降沿时判断计数器的值并产生占空比为1:2N的M分频器C1;上升沿时判断计数器的值并产生占空比为N:N+1的M分频器CO。两个分频器的输出端相或既可实现等占空比的M分频器。程序附下。图1为等占空比5分频电路的仿真波形。

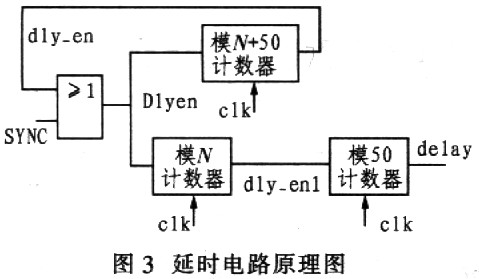

architecture Behavioral of div is

如果在上述程序最后加入判断语句,则该段程序可以实现等占空比的任意分频,判断M-N的奇偶性:M-N为偶数,CO就是所要的分频输出;M-N为奇数.C0+C1为所要的分频输出。

第三种是小数分频电路。实现分频系数为N-0.5的分频器.可以采用1个模N的减法计数器、1个异或门、1个2分频器。要想用同一个电路完成多种形式半分频,可以在半整数分频器原理的基础上对异或门加1个使能控制信号。

2.2 延时电路

延时电路是电子设计中常用的电路。在学习数字电路时采用555型集成定时器来实现脉冲的延迟,而在进行信号处理时,很多设计并不能使用555集成定时器来完成。用VHDL语言设计时一般用计数器或计数器的级联来实现。下面以一个实例来说明如何实现任意时间量的延时。

在5 MHz时钟CLK控制下对同步信号SYNC进行N延时(SYNC脉冲宽度为2 μs,脉冲重复频率为1 kHz;0μs≤N≤998 μs)。要求每次在同步脉冲上升沿到来时开始延时,并在延时结束后产生宽度为10 μs的选通信号。

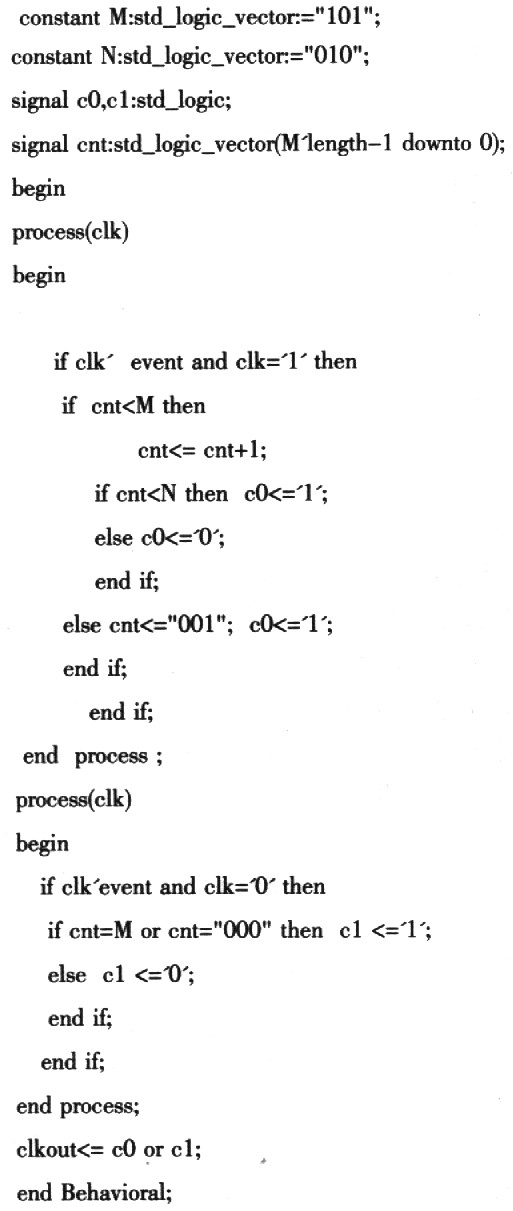

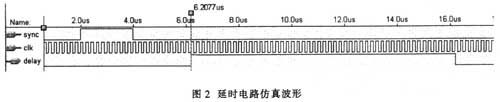

需要产生的延时时序如图2所示(延时量N=4.2μs)。

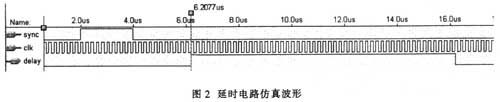

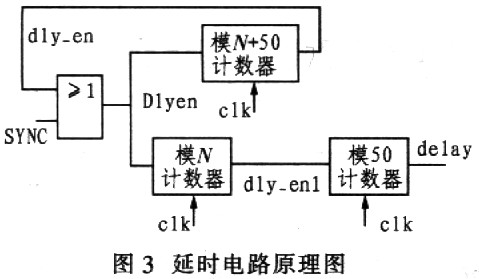

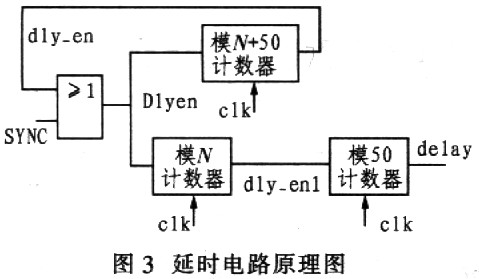

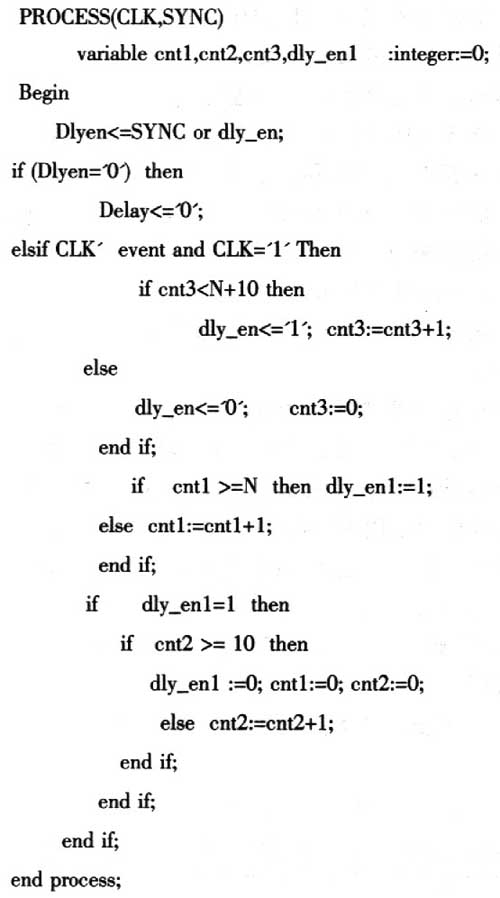

这里采用3个计数器和1个或门产生上述延时信号,如图3所示,模N计数器计延时量;模50计数器计选通信号的宽度;模N+50计数器用于产生使能信号。用VHDL硬件描述语言进行硬件电路设计时,同一个进程中不能用2个时钟来触发,而时序图中又要求在同步脉冲SYNC的上升沿开始延时,为了解决这一问题,采用了模N+50计数器和1个或门。

当同步脉冲为高电平时,模N计数器和模N+50计数器开始计数,并置dly_en为高电平。模N计数器满,置dly_enl为高电平同时产生选通信号。当模N+50计数器计满即选通信号产生完之后置dly_en为低电平。当下一个同步脉冲到来时重复以上过程。这种设计电路的好处是当同步脉冲的宽度改变时对时序控制并无影响,因为在计数过程中只用了SYNC的上升沿,从延时开始到选通信号结束,在或门的作用下SYNC对计数器不起控制作用。

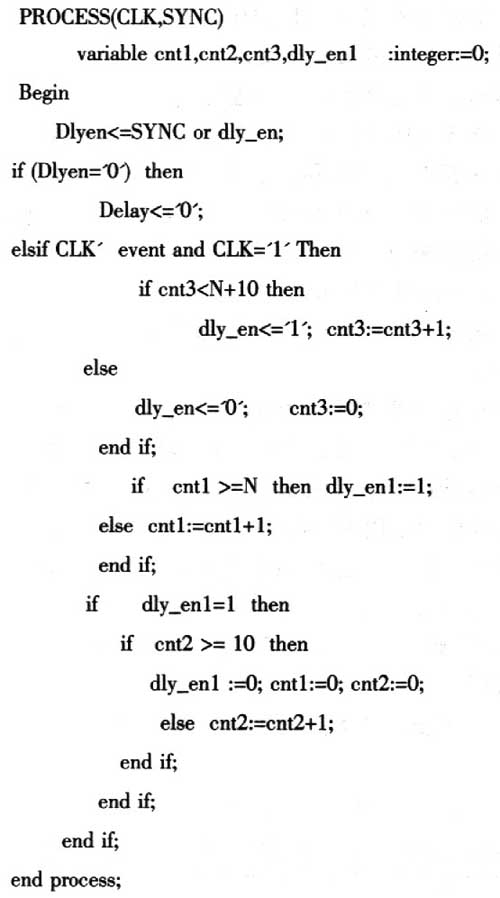

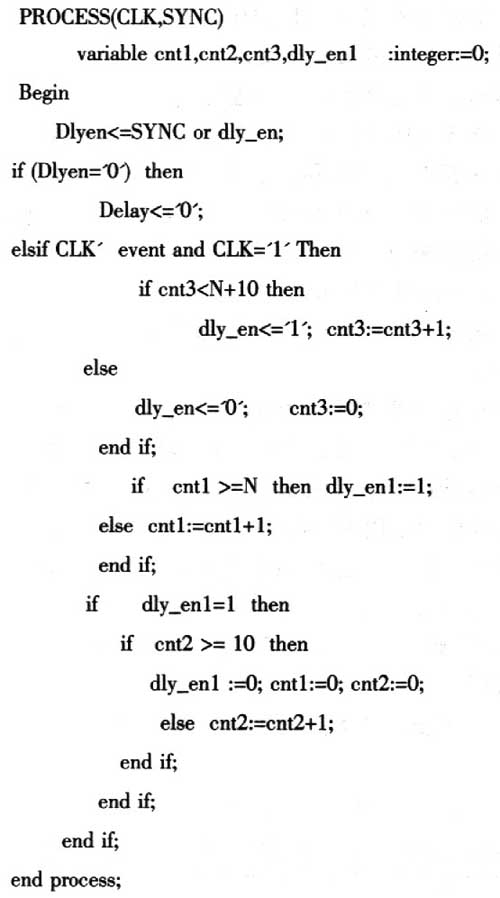

上述电路的VHDL程序如下:

该程序选择N=20,即延时量是4.2 μs,由于要使用时钟来判断SYNC的上升沿情况,因此,如果令N=0,产生的delay信号仍然会有1个时钟的固有延时,在计算延时量时应充分考虑到这一点,延时量=(N+1)×时钟周期。该程序是雷达目标模拟器时序控制程序的一部分,它产生的延时用于模拟目标的距离,随着目标的运动,要求模拟的延时量也要变化,每次同步脉冲上升沿到来之前,DSP会计算出延时量N并通过数据总线送给FPGA。

2.3 双向电路

在工程应用中,双向电路是设计者必须面对的问题。

使用VHDL语言设计FPGA时,经常会遇到很多接口控制电路的设计,例如FPGA与外部存储设备的接口电路设计、FPGA与DSP接口电路的设计、FPGA与CPU接口电路的设计等,其中数据总线的设计是不可避免的,而数据总线往往是双向的。因此,如何正确处理数据总线是进行时序逻辑电路设计的基础。

在程序设计过程中,双向信号既作为信号的输入又作为信号的输出。常见双向信号的模式有二种,第一种是双向信号作为一个信号的输入,作为另一信号的输出;第二种是双向信号既作为输出又作输入。经常用的数据总线就是第二种模式。要很好地进行双向电路的设计,关键在于实体部分必须对端口属性进行说明,端口属性必须为inout类型;在构造体内需要对输出信号进行有条件的高阻控制。

下面结合一段程序说明用VHDL编写数据总线时应注意的问题,第一种模式的双向信号编写与此类似。

DBus为数据总线,datal6(15 downto 0)和SA(18downto 0)为16位和19位的寄存器,dlyL和dlyH为datal6的使能端,AddrLReg、AddrMReg、AddrHReg为SA的使能端。

dlyL或dlyH为高电平时FPGA从数据总线上读取数据(延时量),锁存在数据寄存器datal6里;AddrLReg、AddrMReg、AddrHReg有1个为高电平时FPGA把状态寄存器SA的值送到数据总线上。

在双向电路程序设计中,DBus输入是普通的in类型,而在输出时需要加一定的控制条件来控制高阻状态。最后一句不可省去,它说明了双向信号的三态输出,更要注意when后面语句的条件限制,如果条件限制太宽就会错误占用双向信号总线,引起总线的误操作;如果条件限制太窄,输出寄存器的数据就不能正确地送到数据总线,引起数据的丢失。一般可以使用枚举法一一把用到的地址线罗列出来,表示只有在这样的地址线的情况下才会用到数据总线,否则其他状态对数据总线进高阻,表示不占用数据总线。

3 结束语

DSP技术在许多领域具有广泛的用途,以往经常采用的固定功能的DSP或ASIC可以提供很好的实时性能,但其灵活性差,不适合在实验室或技术开发等场合使用;DSP在软件算法上受到一定的限制,因此使用DSP和FPGA结合是进行数字信号处理的一种趋势,而使用VHDL/VerilogHDL硬件描述语言设计CPLD/FPGA也是电子设计师们应该掌握的一门技术。

1 引言

随着EDA技术的发展,使用硬件语言设计可编程逻辑器件(PLD)/现场可编程门阵列(FPGA)成为一种趋势。FPGA是一种将门阵列的通用结构与PLD的现场可编程特性结合为一体的新型器件,具有集成度高、通用性好、设计灵活、编程方便、产品上市快等诸多优点。美国Xilinx公司于1985年领先推出了FPGA。目前市场上应用较广泛的FPGA产品当数Xilinx公司的Spartan和Virtex系列及Al-tera公司的ACEX和APEX系列。

目前最主要的硬件描述语言是VHDL和Ver-ilog HDL。VHDL发展的较早,语法严格,而VerilogHDL是在C语言的基础上发展起来的硬件描述语言,语法较自由。在工程应用尤其是在有关控制电路的设计中,用VHDL硬件描述语言设计FPGA经常会遇到以下三个问题:实现等占空比、非等占空比整数分频的分频电路;在时钟控制下对同步脉冲信号任意时间量的延迟;使用VHDL语言进行双向电路的设计。

2 常见问题

2.1 分频电路

分频电路是数字系统设计中的基本电路。在硬件电路设计中,时钟信号是最重要的信号之一,经常需要对较高频率的时钟进行分频操作,得到较低频率的时钟信号。分频电路一般分为三种:

第一种是任意占空比的偶数分频及非等占空比的奇数分频,通常由计数器或计数器的级联来完成。

第二种是等占空比的奇数分频电路。要实现占空比为50%的M=2N+1分频电路,本文采用计数器和1个或门来实现。

利用时钟的上升沿计数,设计一个模M的计数器:下降沿时判断计数器的值并产生占空比为1:2N的M分频器C1;上升沿时判断计数器的值并产生占空比为N:N+1的M分频器CO。两个分频器的输出端相或既可实现等占空比的M分频器。程序附下。图1为等占空比5分频电路的仿真波形。

architecture Behavioral of div is

如果在上述程序最后加入判断语句,则该段程序可以实现等占空比的任意分频,判断M-N的奇偶性:M-N为偶数,CO就是所要的分频输出;M-N为奇数.C0+C1为所要的分频输出。

第三种是小数分频电路。实现分频系数为N-0.5的分频器.可以采用1个模N的减法计数器、1个异或门、1个2分频器。要想用同一个电路完成多种形式半分频,可以在半整数分频器原理的基础上对异或门加1个使能控制信号。

2.2 延时电路

延时电路是电子设计中常用的电路。在学习数字电路时采用555型集成定时器来实现脉冲的延迟,而在进行信号处理时,很多设计并不能使用555集成定时器来完成。用VHDL语言设计时一般用计数器或计数器的级联来实现。下面以一个实例来说明如何实现任意时间量的延时。

在5 MHz时钟CLK控制下对同步信号SYNC进行N延时(SYNC脉冲宽度为2 μs,脉冲重复频率为1 kHz;0μs≤N≤998 μs)。要求每次在同步脉冲上升沿到来时开始延时,并在延时结束后产生宽度为10 μs的选通信号。

需要产生的延时时序如图2所示(延时量N=4.2μs)。

这里采用3个计数器和1个或门产生上述延时信号,如图3所示,模N计数器计延时量;模50计数器计选通信号的宽度;模N+50计数器用于产生使能信号。用VHDL硬件描述语言进行硬件电路设计时,同一个进程中不能用2个时钟来触发,而时序图中又要求在同步脉冲SYNC的上升沿开始延时,为了解决这一问题,采用了模N+50计数器和1个或门。

当同步脉冲为高电平时,模N计数器和模N+50计数器开始计数,并置dly_en为高电平。模N计数器满,置dly_enl为高电平同时产生选通信号。当模N+50计数器计满即选通信号产生完之后置dly_en为低电平。当下一个同步脉冲到来时重复以上过程。这种设计电路的好处是当同步脉冲的宽度改变时对时序控制并无影响,因为在计数过程中只用了SYNC的上升沿,从延时开始到选通信号结束,在或门的作用下SYNC对计数器不起控制作用。

上述电路的VHDL程序如下:

该程序选择N=20,即延时量是4.2 μs,由于要使用时钟来判断SYNC的上升沿情况,因此,如果令N=0,产生的delay信号仍然会有1个时钟的固有延时,在计算延时量时应充分考虑到这一点,延时量=(N+1)×时钟周期。该程序是雷达目标模拟器时序控制程序的一部分,它产生的延时用于模拟目标的距离,随着目标的运动,要求模拟的延时量也要变化,每次同步脉冲上升沿到来之前,DSP会计算出延时量N并通过数据总线送给FPGA。

2.3 双向电路

在工程应用中,双向电路是设计者必须面对的问题。

使用VHDL语言设计FPGA时,经常会遇到很多接口控制电路的设计,例如FPGA与外部存储设备的接口电路设计、FPGA与DSP接口电路的设计、FPGA与CPU接口电路的设计等,其中数据总线的设计是不可避免的,而数据总线往往是双向的。因此,如何正确处理数据总线是进行时序逻辑电路设计的基础。

在程序设计过程中,双向信号既作为信号的输入又作为信号的输出。常见双向信号的模式有二种,第一种是双向信号作为一个信号的输入,作为另一信号的输出;第二种是双向信号既作为输出又作输入。经常用的数据总线就是第二种模式。要很好地进行双向电路的设计,关键在于实体部分必须对端口属性进行说明,端口属性必须为inout类型;在构造体内需要对输出信号进行有条件的高阻控制。

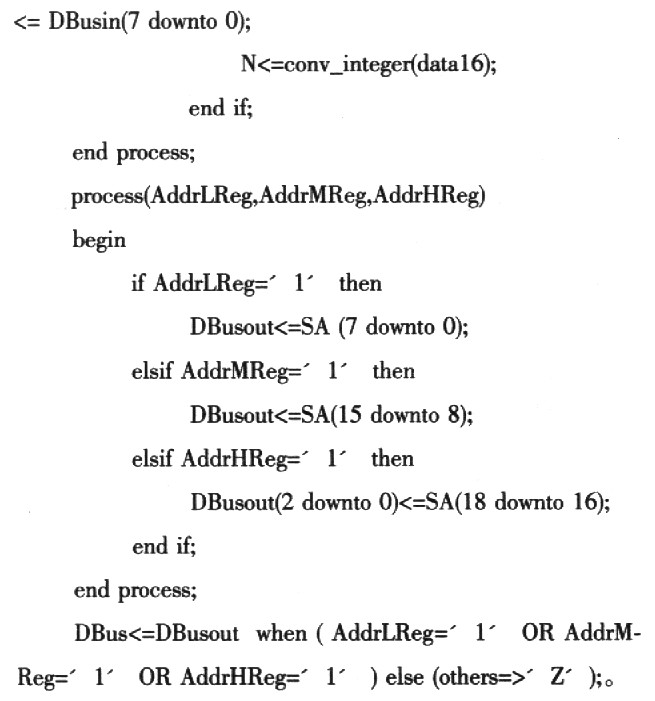

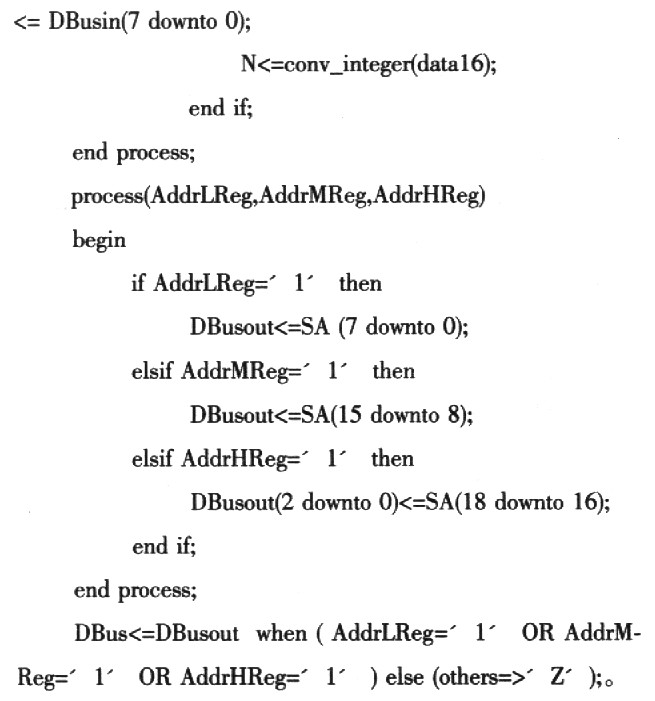

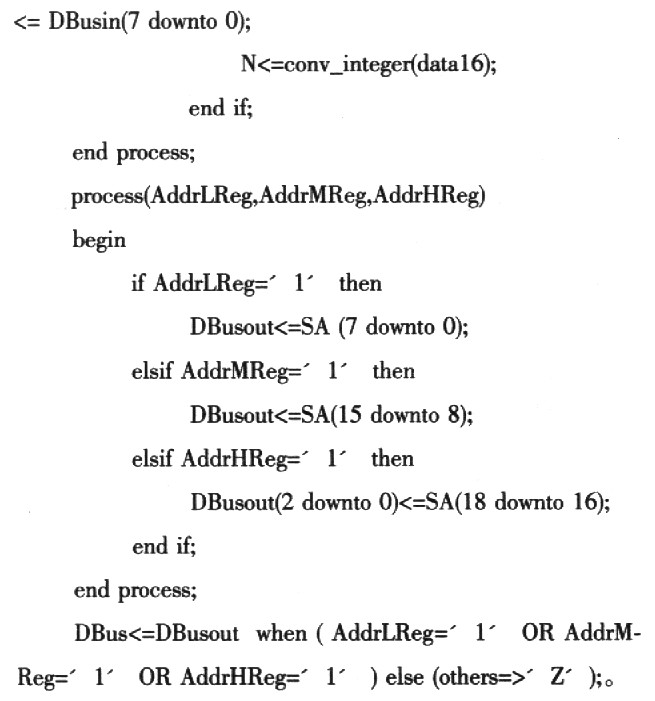

下面结合一段程序说明用VHDL编写数据总线时应注意的问题,第一种模式的双向信号编写与此类似。

DBus为数据总线,datal6(15 downto 0)和SA(18downto 0)为16位和19位的寄存器,dlyL和dlyH为datal6的使能端,AddrLReg、AddrMReg、AddrHReg为SA的使能端。

dlyL或dlyH为高电平时FPGA从数据总线上读取数据(延时量),锁存在数据寄存器datal6里;AddrLReg、AddrMReg、AddrHReg有1个为高电平时FPGA把状态寄存器SA的值送到数据总线上。

在双向电路程序设计中,DBus输入是普通的in类型,而在输出时需要加一定的控制条件来控制高阻状态。最后一句不可省去,它说明了双向信号的三态输出,更要注意when后面语句的条件限制,如果条件限制太宽就会错误占用双向信号总线,引起总线的误操作;如果条件限制太窄,输出寄存器的数据就不能正确地送到数据总线,引起数据的丢失。一般可以使用枚举法一一把用到的地址线罗列出来,表示只有在这样的地址线的情况下才会用到数据总线,否则其他状态对数据总线进高阻,表示不占用数据总线。

3 结束语

DSP技术在许多领域具有广泛的用途,以往经常采用的固定功能的DSP或ASIC可以提供很好的实时性能,但其灵活性差,不适合在实验室或技术开发等场合使用;DSP在软件算法上受到一定的限制,因此使用DSP和FPGA结合是进行数字信号处理的一种趋势,而使用VHDL/VerilogHDL硬件描述语言设计CPLD/FPGA也是电子设计师们应该掌握的一门技术。

举报

举报

举报

举报