在软件无线电的组建中,A/D和D/A起着关键作用,通常要求A/D转换器有足够的工作带宽(2GHz以上)和较高的采样速率(一般在60MHz以上),同时应有较高的A/D转换位数以提高动态范围。AD公司推出的新一代A/D转换器AD6644可以满足其要求。下面将对AD6644器件的特点、原理及应用进行介绍。

1 主要特点

该芯片的主要特点如下:

保持采样率可达到65MHz;

采用完全差动模拟输入;

为了便于和数字ASIC接口,数字输出级可工作在+3.3V电源上;

内含基准电压源和跟踪/保持放大器;

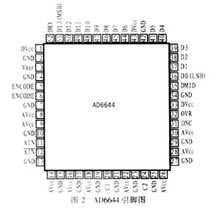

采用小型表面贴装52脚封装(LQFP)。 AD6644的内部电路结构如图1所示。表1所列 为其主要的极限参数。图2所示是其引脚排列,各引脚的功能说明如下:

DVcc:+3.3V功率输出级电源(数字)。

GND:接地端。

VREF:2.4V内部基准电压。使用时应用0.1μF片状电容旁路到地。

ENCODE:编码输入。在上升沿开始转换数据。

ENCODE互补端,可与ENCODE组成差分驱动。

AVcc:+5V模拟电源。 AIN:模拟输入。

:模拟输入互补端。

C1~C2:内部偏置点。应用0.1μF片状电容旁路到地。

DNC:无连接。

OVR:超出额定位,高位指示模拟输入超过±FS。

DMID:输出数据电压中值;近似等于(DVcc)/2。

D0~D13:数据输出位,其中D0为最低有效位LSB,D13为最高有效位MSB;

DRY:数据输出准备。

2 工作原理

AD6644采用的是三级子区式转换结构,这种设计即保证了所需的转换精度和转换速度,又降低了功耗,同时也减小了模片尺寸。AD6644的模拟信号输入方式为差分结构,每个输入的电压范围以2.4V为中心,上下摆动在0.55V以内。由于两个输入的相位相差180°,所以模拟输入信号的最大峰-峰值为2.2V。

从图1可以看出,两个模拟输入端首先经过缓冲,然后进入第一个采样保持器(TH1)。当采样时钟为高时,TH1进入保持状态。TH1的保持值作为粗5位A/D转换器(ADC1)的输入,其输出用于驱动一个5位D/A转换器(DAC1)。如将延迟的模拟信号与DAC1的输出相减,则可在保持器TH3的输入端产生第一剩余信号。保持器TH2的作用是为ADC1数字延迟后的一个模拟信道延迟进行补偿。第一剩余信号用于转换的第二阶段,此阶段包括一个5位A/D转换(ADC2)、5位D/A转换(DAC2)以及信道TH4。将TH4保持的第一剩余信号与DAC2的量化输出相减,所得到的第二剩余信号可作为TH5的输入。

将ADC1、ADC2和ADC3相加,并将修正后的结果传至数字误差校正逻辑,便可输出最终的14位模数转换结果。

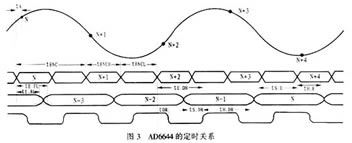

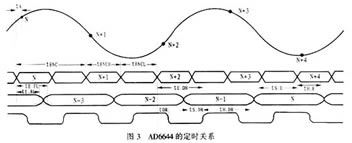

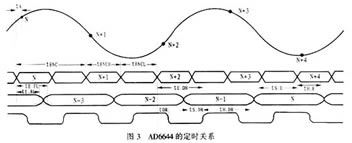

图3所示为AD6644的时序关系图。

3 AD6644的应用

软件无线电是近年来随着计算机及微电子技术高速发展而产生的一种全新的无线电技术,它的出现,是无线电通信从模拟到数字、从固定到移动、从硬件到软件的三次变革的产物。“软件无线电”(Software Radio)的概念由Jeo Mitola于1992年5月在全美通信系统年会上首次明确提出。它是将模块化、标准化的硬件单元以总线方式连接起来构成基本平台,然后通过软件加载来实现各种无线通信功能(包括不同频段、不同制式),并将A/D和D/A (模/数和数/模转换)功能尽可能地靠近天线端研制出的新一代无线电通信系统。因此,软件无线电系统具有开放性、模块化、标准化以及实现灵活、可软件升级、适于大规模制造等诸多优点,这些特点使其不仅在军用和民用无线通信中开始获得应用,而且也正在向其它无线电技术领域推广,因此该技术的研究已悄然成为各国竞相研究的热点。

目前,在A/D和D/A器件上,一些产品已能工作在中频频段。AD6644是一种性能优良,具有14位分辨率、65MSPS抽样率的模数转换器,是继AD9042(12位,41MSPS)和AD6640(12位,65MSPS)之后,宽带ADC家族中的第三代产品。采用AD6644的软件无线电设备体积小,成本低,也易于针对新的无线服务标准来进行编程和设置。AD6644的其它特点还包括采样抖动小于300fs,功率消耗小于1.3瓦等。因此,AD6644的出现为实现新一代通信设备k可编程数字无线电接收机(通称软件无线电)提供了一种业界最佳性能的模数转换器。

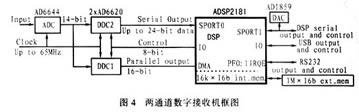

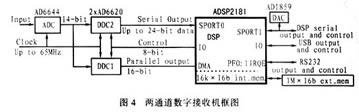

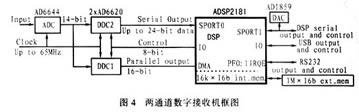

采用AD6644作为模数转换器件(ADC)的数字接收机很多,图4给出了一个两通道数字接收机的结构框图。该接收机充分发挥了AD6644的各项性能,可以很好地实现宽带高速多位采样,并能保证较高的采样速率。其单端ADC的模拟输入带宽为400MHz,输入阻抗为1kΩ,并采用差分输入。接收机中ADC的采样速率最大可达65MSPS,最大动态范围可达到137dB。

在软件无线电的组建中,A/D和D/A起着关键作用,通常要求A/D转换器有足够的工作带宽(2GHz以上)和较高的采样速率(一般在60MHz以上),同时应有较高的A/D转换位数以提高动态范围。AD公司推出的新一代A/D转换器AD6644可以满足其要求。下面将对AD6644器件的特点、原理及应用进行介绍。

1 主要特点

该芯片的主要特点如下:

保持采样率可达到65MHz;

采用完全差动模拟输入;

为了便于和数字ASIC接口,数字输出级可工作在+3.3V电源上;

内含基准电压源和跟踪/保持放大器;

采用小型表面贴装52脚封装(LQFP)。 AD6644的内部电路结构如图1所示。表1所列 为其主要的极限参数。图2所示是其引脚排列,各引脚的功能说明如下:

DVcc:+3.3V功率输出级电源(数字)。

GND:接地端。

VREF:2.4V内部基准电压。使用时应用0.1μF片状电容旁路到地。

ENCODE:编码输入。在上升沿开始转换数据。

ENCODE互补端,可与ENCODE组成差分驱动。

AVcc:+5V模拟电源。 AIN:模拟输入。

:模拟输入互补端。

C1~C2:内部偏置点。应用0.1μF片状电容旁路到地。

DNC:无连接。

OVR:超出额定位,高位指示模拟输入超过±FS。

DMID:输出数据电压中值;近似等于(DVcc)/2。

D0~D13:数据输出位,其中D0为最低有效位LSB,D13为最高有效位MSB;

DRY:数据输出准备。

2 工作原理

AD6644采用的是三级子区式转换结构,这种设计即保证了所需的转换精度和转换速度,又降低了功耗,同时也减小了模片尺寸。AD6644的模拟信号输入方式为差分结构,每个输入的电压范围以2.4V为中心,上下摆动在0.55V以内。由于两个输入的相位相差180°,所以模拟输入信号的最大峰-峰值为2.2V。

从图1可以看出,两个模拟输入端首先经过缓冲,然后进入第一个采样保持器(TH1)。当采样时钟为高时,TH1进入保持状态。TH1的保持值作为粗5位A/D转换器(ADC1)的输入,其输出用于驱动一个5位D/A转换器(DAC1)。如将延迟的模拟信号与DAC1的输出相减,则可在保持器TH3的输入端产生第一剩余信号。保持器TH2的作用是为ADC1数字延迟后的一个模拟信道延迟进行补偿。第一剩余信号用于转换的第二阶段,此阶段包括一个5位A/D转换(ADC2)、5位D/A转换(DAC2)以及信道TH4。将TH4保持的第一剩余信号与DAC2的量化输出相减,所得到的第二剩余信号可作为TH5的输入。

将ADC1、ADC2和ADC3相加,并将修正后的结果传至数字误差校正逻辑,便可输出最终的14位模数转换结果。

图3所示为AD6644的时序关系图。

3 AD6644的应用

软件无线电是近年来随着计算机及微电子技术高速发展而产生的一种全新的无线电技术,它的出现,是无线电通信从模拟到数字、从固定到移动、从硬件到软件的三次变革的产物。“软件无线电”(Software Radio)的概念由Jeo Mitola于1992年5月在全美通信系统年会上首次明确提出。它是将模块化、标准化的硬件单元以总线方式连接起来构成基本平台,然后通过软件加载来实现各种无线通信功能(包括不同频段、不同制式),并将A/D和D/A (模/数和数/模转换)功能尽可能地靠近天线端研制出的新一代无线电通信系统。因此,软件无线电系统具有开放性、模块化、标准化以及实现灵活、可软件升级、适于大规模制造等诸多优点,这些特点使其不仅在军用和民用无线通信中开始获得应用,而且也正在向其它无线电技术领域推广,因此该技术的研究已悄然成为各国竞相研究的热点。

目前,在A/D和D/A器件上,一些产品已能工作在中频频段。AD6644是一种性能优良,具有14位分辨率、65MSPS抽样率的模数转换器,是继AD9042(12位,41MSPS)和AD6640(12位,65MSPS)之后,宽带ADC家族中的第三代产品。采用AD6644的软件无线电设备体积小,成本低,也易于针对新的无线服务标准来进行编程和设置。AD6644的其它特点还包括采样抖动小于300fs,功率消耗小于1.3瓦等。因此,AD6644的出现为实现新一代通信设备k可编程数字无线电接收机(通称软件无线电)提供了一种业界最佳性能的模数转换器。

采用AD6644作为模数转换器件(ADC)的数字接收机很多,图4给出了一个两通道数字接收机的结构框图。该接收机充分发挥了AD6644的各项性能,可以很好地实现宽带高速多位采样,并能保证较高的采样速率。其单端ADC的模拟输入带宽为400MHz,输入阻抗为1kΩ,并采用差分输入。接收机中ADC的采样速率最大可达65MSPS,最大动态范围可达到137dB。

举报

举报

举报

举报