AD9883A是专为个人电脑和工作站的RGB图像信号采集而设计的接口芯片,广泛应用于各类高清CRT、平板电视、微显背投和投影仪等系统。

AD9883A特性

AD9883A内部包含具有300MHz输入带宽的8位140MSPS ADC、PLL和可编程的增益、复位、嵌位控制,用户只需要提供3.3V的电源、模拟输入、Hsync和COAST信号。140MSPS的采样转换率最高支持1280×1024(75Hz刷新)分辨率的信号。

AD9883A包含所需的输入缓冲器,信号直流恢复(采样)、复位、增益(亮度和对比度)调整、像素时钟发生器、采样相位控制和输出数据格式化,所有的控制都可以由双线制串行总线控制。由于电路设计更简洁,芯片受物理和电子环境的影响很小。其典型功率为500mW,使用温度范围为0~70℃。

AD9883A所有的数字输入为3.3V CMOS电平,但5V的输入电平也不会对芯片造成任何损坏。AD9883A 有红、绿和蓝三个高阻抗模拟输入脚,它们的有效信号电平为0.5~1.0VP-P,信号一般先通过DVI连接器、15针D型连接器、RCA同轴连接端子或BNC连接器。AD9883A的内部功能如图1所示,它在PCB上的位置应尽量接近实际输入,信号必须通过适配电阻(一般为75Ω)连到芯片。

图1 AD9883A内部功能框图

AD9883A特殊引脚功能要点

输出

HSOUT:输出行同步经过相位调整的副本,极性和幅度可通过串行总线寄存器控制。行同步取决于串行数据的不断调整。

VSOUT:输出视频场同步经过相位调整的副本,输出极性由串行总线寄存器位控制。它在所有模式图像传输的过程中有效。

SOGOUT:该脚从绿色幅度限制比较器或未处理的行同步副本输出。

RED/GREEN/BLUE:对应R/Cr、G/Y、B/Cb数据输出,最高位为MSB。从像素采样到输出的延时是固定的。

DATACK:该引脚通常为输出数据和HSOUT的外部逻辑提供主时钟输出信号,它由内部时钟产生,并与内部取样时钟同步。

输入

RAIN/GAIN/BAIN:R/Pr/Cr、G/Y、B/Pb/Cb模拟图像信号的高阻抗,独立输入。

HSYNC:该引脚接受一个逻辑信号,用于参考建立行时序,并为图像时钟产生器提供参考频率。其输入还包含噪声抑制施密特触发器,输入极限位1.5V。

SOGIN:嵌入同步提供一个辅助处理信号。该引脚连到一个带有内部阈值的高速比较器,阈值可由程序控制,以10mV为步长,从输入信号波谷上方10~300mV,缺省阈值为150mV。

CLAMP:在嵌位功能脚设置为1时有效。当禁止时,该引脚被忽略,嵌位时序由内部计时器延时决定。不用时,该引脚必须接到地,并且通过程序将该功能设置为0。

COAST:用于在停止行同步输入时继续产生一个和当前频率相位一致的图像时钟信号,该引脚信号一般不由PC产生,不用时必须接地,并且通过程序将该功能设置为1;或接高电平(通过10kΩ的电阻上拉到VD)并通过程序将该功能设置为0,上电时该功能设置缺省值为1。

电源

VDD:大量的输出引脚(共25个)高速(高达110 MHz)触发会产生电源干扰,将这些引脚的电源和VDD分离可以将敏感的模拟电路干扰降到最小。如果AD9883A使用较低的逻辑电平,VDD可以连接2.5V的兼容电源。

REF BYPASS:内部1.25V参考分压电路,它必须通过0.1μF的电容连到地,精确度为4%,温度系数为50ppm/℃,对于AD9883A的大部分应用是足够的,如果需要更高精确度,可以提供一个外部参考。

MIDSCV:内部中级电压参考旁路,必须通过0.1μF的电容连到地,这个精确电压随绿色增益改变,相位时钟发生器PLL需要外部滤波,可将噪声和寄生效应降到最小。

PLL设置

AD9883A的片上PLL可基于行同步频率产生像素时钟,可编程注册器可提供最优的PLL性能,主要用于定义VCO范围注册器、充电脉冲电流注册器和PLL分频注册器。基于行同步频率设计像素时钟频率(采样频率)和回路滤波电容,AD9883A的PLL回路滤波设计如图2所示。

图2 PLL回路滤波设计图

AD9883A有一个双线串行接口,它包括一个时钟(SCL)和一个双向数据(SDA)引脚,AD9883A的初始化与控制由决定工作模式的注册器完成,使用外部控制器通过双线串行接口实现对控制注册器的读写操作,从而完成对ADC的控制设定。SDA传输的是8位数据(含1个R/W控制位和Bit7~Bit1数据位),当寄存器的地址为03H时,Bit7、6设置VCO的范围;Bit5、4、3设置驱动低通滤波器的不同电流,即充电脉冲电流。

表1 VCO范围的选择

VCO范围的选择

依据表1选择VCO的范围,如果像素频率小于125MHz,则KVCO=150;否则KVCO=180。

充电脉冲电流的计算

以下两式用以计算充电脉冲电流Ip。

PLL自然频率=2π×行频/PLL稳态速率=

PLL自然频率=

由上式可得:,其中回路滤波器电容:Ct=Cp=Cz=

0.082μF;PLL分频速率:N=fp/fh。其中SR和传递分频系数P的取值方法如表2所示。

表2 SR和P的取值

充电脉冲电流注册设置根据Ip的大小进行,如表3所示。

表3 充电脉冲电流注册设置

AD9883A的应用

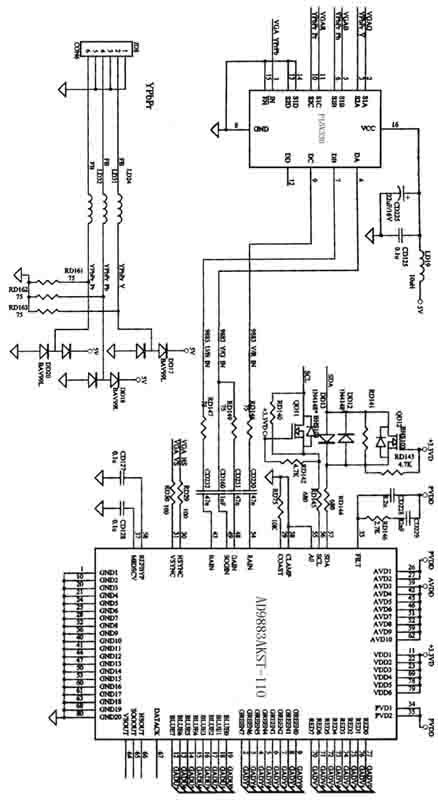

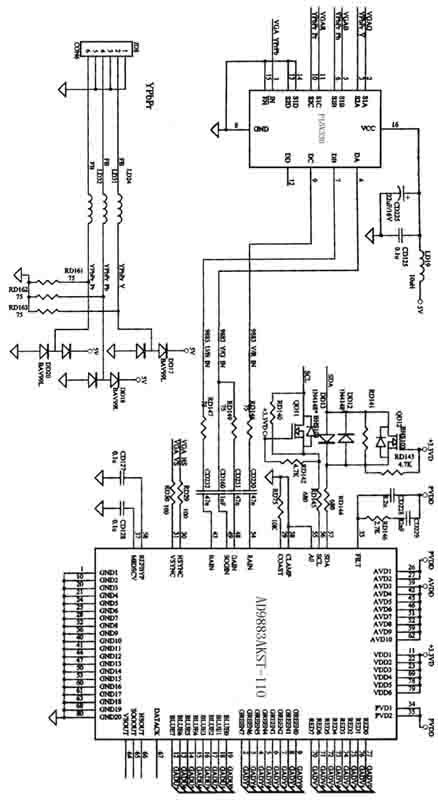

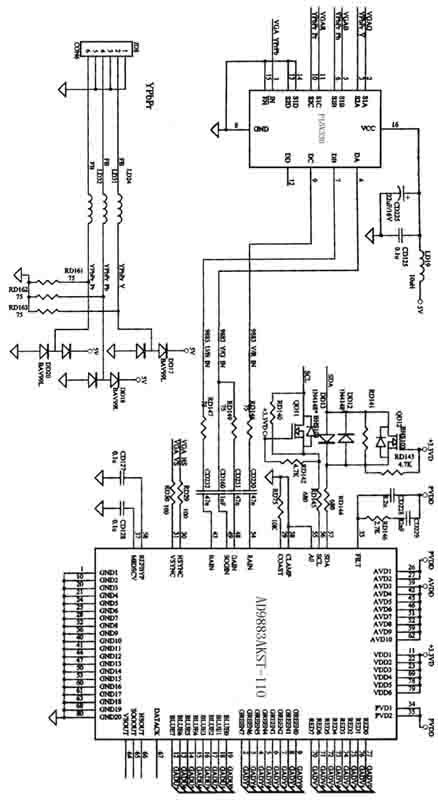

图3是以AD9883AKST-110(AD9883A的一种)为核心的典型高清电视的模拟分量视频信号解码电路。电路中PVDD为PLL供电电源,AVDD为模拟部分供电电源,均为3.3V;“3.3VD”为数字部分供电电源;电路工作原理如下。

图3 AD9883A应用电路图

两组模拟分量视频信号YPbPr(逐行分量576P、480P和高清分量1080i、720P)、RGB(计算机格式VGA—SXGA)经切换选择电路P15V330,由CPU发出的VGA YPrPb控制信号控制P15V330的选择输出。当VGA YPrP,选择RGB输出;当VGA YPrP,选择YPbPr输出。YPbPr的同步脉冲包含在Y信号中。Y/G信号还通过CD160输入SOGIN,以便在SOGOUT脚产生包含行场同步信息的复合同步信号。计算机格式VGA-SXGA的行同步(HSYNC)信号、场同步(VSYNC)信号输入到AD9883A的HSYNC和VSYNC。

从CPU的CLK和DATA输出的I2C控制信号,被外接的QD11、QD12构成的电平转换电路进行电平转换后连接到AD9883A的SCL和SDA,对ADC进行控制设定。

AD9883A在I2C控制信号的控制下,同时根据输入的行、场同步信号的频率及极性,以及第33脚输入的滤波值,将输入的行频信号分频成与输入信号格式变化频率相适应的采样时钟。另一方面, AD9883A根据I2C控制信号设定的相位、钳位电平及增益等,按照新分频得到采样时钟频率对输入的模拟分量视频信号进行数字化采样,转换成数字分量视频信号。

数字化后的数字分量视频信号分别从AD9883A中各自的通道中输出,分别经缓冲后,输出给后级的图像处理芯片。

在ADC内形成的时钟信号从其第67脚输出,G信号复合同步输出SOGOUT、经过相位调整的行同步输出HSOUT和场同步输出VSOUT分别经AD9883A的65、66和64脚输出。这些信号分别输出到后级的图像处理芯片。

AD9883A是专为个人电脑和工作站的RGB图像信号采集而设计的接口芯片,广泛应用于各类高清CRT、平板电视、微显背投和投影仪等系统。

AD9883A特性

AD9883A内部包含具有300MHz输入带宽的8位140MSPS ADC、PLL和可编程的增益、复位、嵌位控制,用户只需要提供3.3V的电源、模拟输入、Hsync和COAST信号。140MSPS的采样转换率最高支持1280×1024(75Hz刷新)分辨率的信号。

AD9883A包含所需的输入缓冲器,信号直流恢复(采样)、复位、增益(亮度和对比度)调整、像素时钟发生器、采样相位控制和输出数据格式化,所有的控制都可以由双线制串行总线控制。由于电路设计更简洁,芯片受物理和电子环境的影响很小。其典型功率为500mW,使用温度范围为0~70℃。

AD9883A所有的数字输入为3.3V CMOS电平,但5V的输入电平也不会对芯片造成任何损坏。AD9883A 有红、绿和蓝三个高阻抗模拟输入脚,它们的有效信号电平为0.5~1.0VP-P,信号一般先通过DVI连接器、15针D型连接器、RCA同轴连接端子或BNC连接器。AD9883A的内部功能如图1所示,它在PCB上的位置应尽量接近实际输入,信号必须通过适配电阻(一般为75Ω)连到芯片。

图1 AD9883A内部功能框图

AD9883A特殊引脚功能要点

输出

HSOUT:输出行同步经过相位调整的副本,极性和幅度可通过串行总线寄存器控制。行同步取决于串行数据的不断调整。

VSOUT:输出视频场同步经过相位调整的副本,输出极性由串行总线寄存器位控制。它在所有模式图像传输的过程中有效。

SOGOUT:该脚从绿色幅度限制比较器或未处理的行同步副本输出。

RED/GREEN/BLUE:对应R/Cr、G/Y、B/Cb数据输出,最高位为MSB。从像素采样到输出的延时是固定的。

DATACK:该引脚通常为输出数据和HSOUT的外部逻辑提供主时钟输出信号,它由内部时钟产生,并与内部取样时钟同步。

输入

RAIN/GAIN/BAIN:R/Pr/Cr、G/Y、B/Pb/Cb模拟图像信号的高阻抗,独立输入。

HSYNC:该引脚接受一个逻辑信号,用于参考建立行时序,并为图像时钟产生器提供参考频率。其输入还包含噪声抑制施密特触发器,输入极限位1.5V。

SOGIN:嵌入同步提供一个辅助处理信号。该引脚连到一个带有内部阈值的高速比较器,阈值可由程序控制,以10mV为步长,从输入信号波谷上方10~300mV,缺省阈值为150mV。

CLAMP:在嵌位功能脚设置为1时有效。当禁止时,该引脚被忽略,嵌位时序由内部计时器延时决定。不用时,该引脚必须接到地,并且通过程序将该功能设置为0。

COAST:用于在停止行同步输入时继续产生一个和当前频率相位一致的图像时钟信号,该引脚信号一般不由PC产生,不用时必须接地,并且通过程序将该功能设置为1;或接高电平(通过10kΩ的电阻上拉到VD)并通过程序将该功能设置为0,上电时该功能设置缺省值为1。

电源

VDD:大量的输出引脚(共25个)高速(高达110 MHz)触发会产生电源干扰,将这些引脚的电源和VDD分离可以将敏感的模拟电路干扰降到最小。如果AD9883A使用较低的逻辑电平,VDD可以连接2.5V的兼容电源。

REF BYPASS:内部1.25V参考分压电路,它必须通过0.1μF的电容连到地,精确度为4%,温度系数为50ppm/℃,对于AD9883A的大部分应用是足够的,如果需要更高精确度,可以提供一个外部参考。

MIDSCV:内部中级电压参考旁路,必须通过0.1μF的电容连到地,这个精确电压随绿色增益改变,相位时钟发生器PLL需要外部滤波,可将噪声和寄生效应降到最小。

PLL设置

AD9883A的片上PLL可基于行同步频率产生像素时钟,可编程注册器可提供最优的PLL性能,主要用于定义VCO范围注册器、充电脉冲电流注册器和PLL分频注册器。基于行同步频率设计像素时钟频率(采样频率)和回路滤波电容,AD9883A的PLL回路滤波设计如图2所示。

图2 PLL回路滤波设计图

AD9883A有一个双线串行接口,它包括一个时钟(SCL)和一个双向数据(SDA)引脚,AD9883A的初始化与控制由决定工作模式的注册器完成,使用外部控制器通过双线串行接口实现对控制注册器的读写操作,从而完成对ADC的控制设定。SDA传输的是8位数据(含1个R/W控制位和Bit7~Bit1数据位),当寄存器的地址为03H时,Bit7、6设置VCO的范围;Bit5、4、3设置驱动低通滤波器的不同电流,即充电脉冲电流。

表1 VCO范围的选择

VCO范围的选择

依据表1选择VCO的范围,如果像素频率小于125MHz,则KVCO=150;否则KVCO=180。

充电脉冲电流的计算

以下两式用以计算充电脉冲电流Ip。

PLL自然频率=2π×行频/PLL稳态速率=

PLL自然频率=

由上式可得:,其中回路滤波器电容:Ct=Cp=Cz=

0.082μF;PLL分频速率:N=fp/fh。其中SR和传递分频系数P的取值方法如表2所示。

表2 SR和P的取值

充电脉冲电流注册设置根据Ip的大小进行,如表3所示。

表3 充电脉冲电流注册设置

AD9883A的应用

图3是以AD9883AKST-110(AD9883A的一种)为核心的典型高清电视的模拟分量视频信号解码电路。电路中PVDD为PLL供电电源,AVDD为模拟部分供电电源,均为3.3V;“3.3VD”为数字部分供电电源;电路工作原理如下。

图3 AD9883A应用电路图

两组模拟分量视频信号YPbPr(逐行分量576P、480P和高清分量1080i、720P)、RGB(计算机格式VGA—SXGA)经切换选择电路P15V330,由CPU发出的VGA YPrPb控制信号控制P15V330的选择输出。当VGA YPrP,选择RGB输出;当VGA YPrP,选择YPbPr输出。YPbPr的同步脉冲包含在Y信号中。Y/G信号还通过CD160输入SOGIN,以便在SOGOUT脚产生包含行场同步信息的复合同步信号。计算机格式VGA-SXGA的行同步(HSYNC)信号、场同步(VSYNC)信号输入到AD9883A的HSYNC和VSYNC。

从CPU的CLK和DATA输出的I2C控制信号,被外接的QD11、QD12构成的电平转换电路进行电平转换后连接到AD9883A的SCL和SDA,对ADC进行控制设定。

AD9883A在I2C控制信号的控制下,同时根据输入的行、场同步信号的频率及极性,以及第33脚输入的滤波值,将输入的行频信号分频成与输入信号格式变化频率相适应的采样时钟。另一方面, AD9883A根据I2C控制信号设定的相位、钳位电平及增益等,按照新分频得到采样时钟频率对输入的模拟分量视频信号进行数字化采样,转换成数字分量视频信号。

数字化后的数字分量视频信号分别从AD9883A中各自的通道中输出,分别经缓冲后,输出给后级的图像处理芯片。

在ADC内形成的时钟信号从其第67脚输出,G信号复合同步输出SOGOUT、经过相位调整的行同步输出HSOUT和场同步输出VSOUT分别经AD9883A的65、66和64脚输出。这些信号分别输出到后级的图像处理芯片。

举报

举报

举报

举报