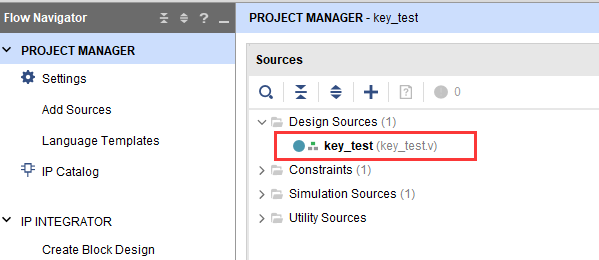

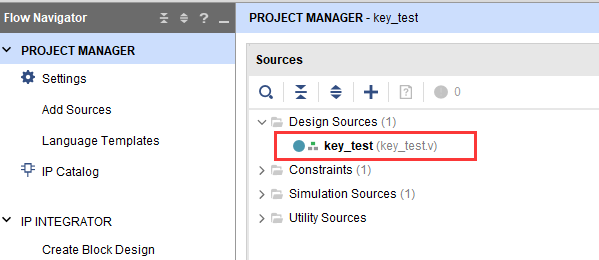

创建Vivado工程

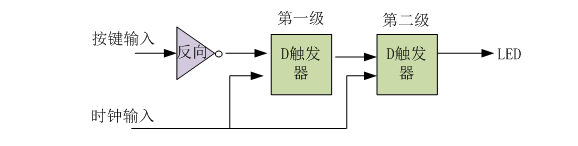

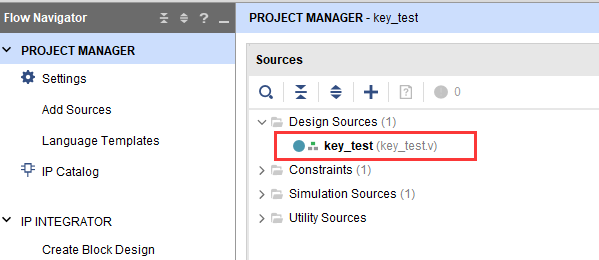

3.1 首先建立按键的测试工程,添加verilog测试代码,完成编译分配管脚等流程。

`timescale1ns/1ps

modulekey_test

(

inputclk,//systemclock25Mhzonboard

input[3:0]key,//inputfourkeysignal,whenthekeydown,thevalueis0

output[3:0]led//LEDdisplay,whenthesiganllow,LEDlighten

);

reg[3:0]led_r;//definethefirststageregister,generatefourDFlip-flop

reg[3:0]led_r1;//definethesecondstageregister,generatefourDFlip-flop

always@(posedgeclk)

begin

led_r《=key;//firststagelatcheddata

end

always@(posedgeclk)

begin

led_r1《=led_r;//secondstagelatcheddata

end

assignled=led_r1;

endmodule

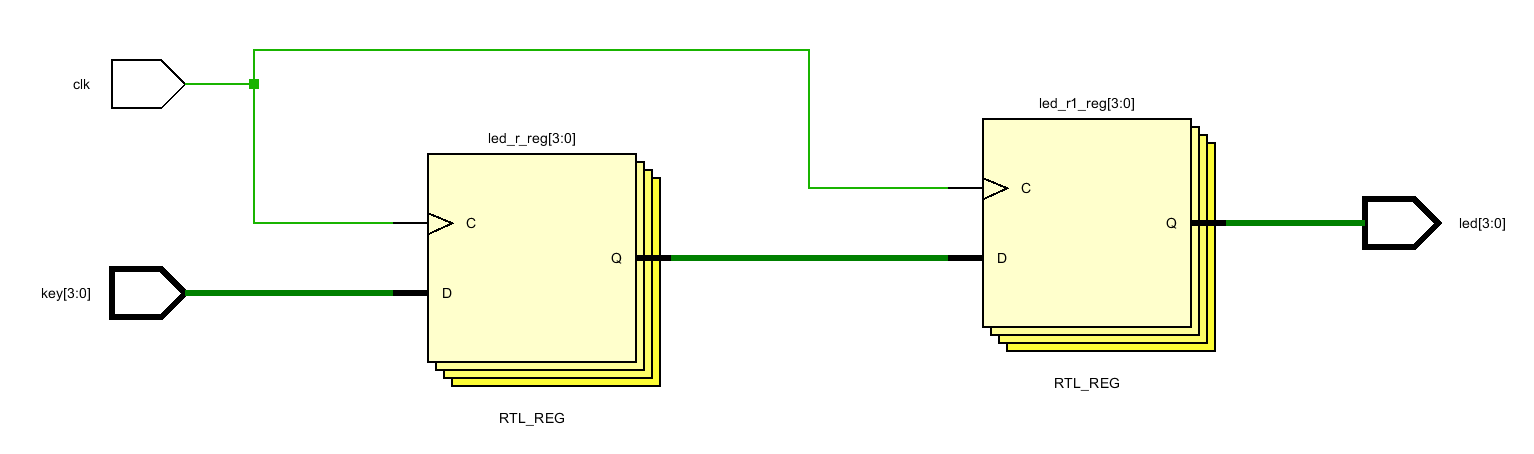

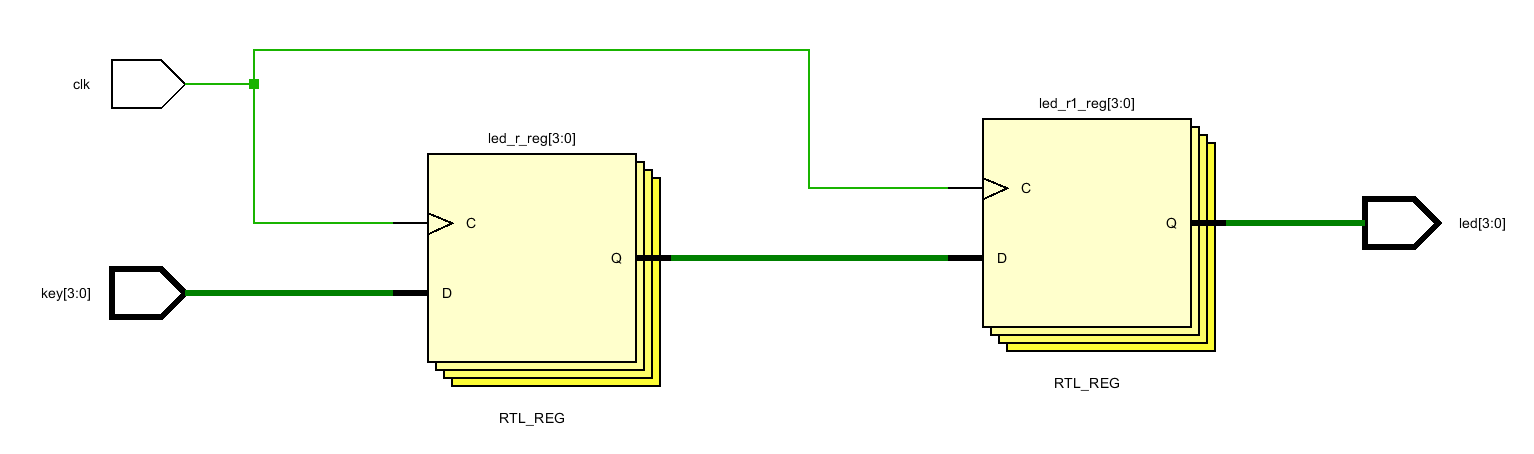

3.2 我们可以使用RTL ANALYSIS工具查看设计

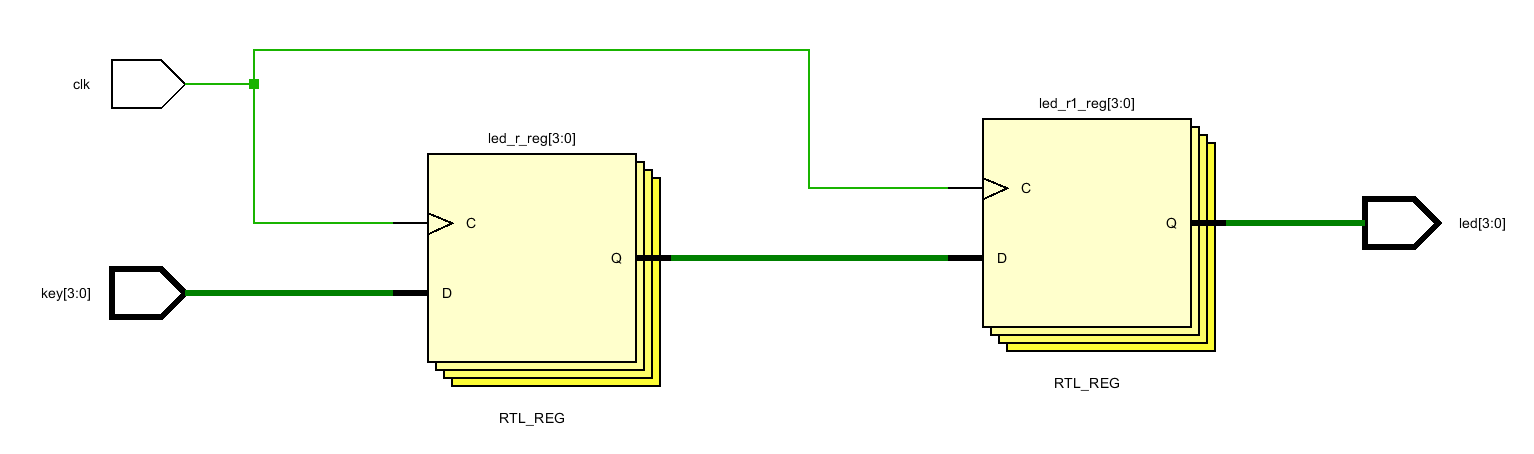

3.3 分析RTL图,可以看出两级D触发器,和预期设计一致。

创建Vivado工程

3.1 首先建立按键的测试工程,添加verilog测试代码,完成编译分配管脚等流程。

`timescale1ns/1ps

modulekey_test

(

inputclk,//systemclock25Mhzonboard

input[3:0]key,//inputfourkeysignal,whenthekeydown,thevalueis0

output[3:0]led//LEDdisplay,whenthesiganllow,LEDlighten

);

reg[3:0]led_r;//definethefirststageregister,generatefourDFlip-flop

reg[3:0]led_r1;//definethesecondstageregister,generatefourDFlip-flop

always@(posedgeclk)

begin

led_r《=key;//firststagelatcheddata

end

always@(posedgeclk)

begin

led_r1《=led_r;//secondstagelatcheddata

end

assignled=led_r1;

endmodule

3.2 我们可以使用RTL ANALYSIS工具查看设计

3.3 分析RTL图,可以看出两级D触发器,和预期设计一致。

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报