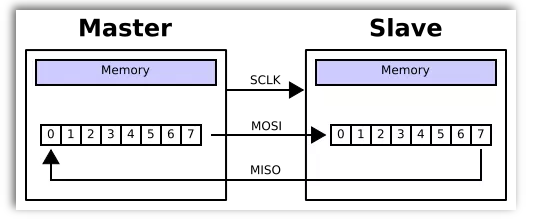

SPI是串行外设接口(Serial Peripheral Interface)的缩写。是 Motorola 公司推出的一 种同步串行接口技术,是一种高速的,全双工,同步的通信总线。

高速和同步可以理解,全双工是什么鬼?

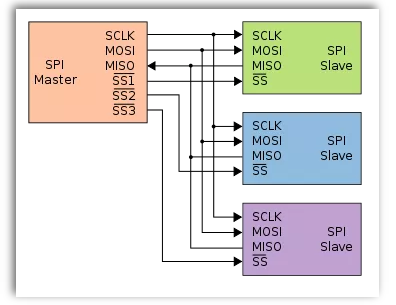

全双工是指host(主设备)与外围从设备之间的发送线和接受线各自独立,发送数据的同时也能够接收数据,两者同步进行。

SPI协议主要用于短距离的通信系统中,特别是嵌入式系统,比如以下芯片:

存储器:RAM,EEPROM,Flash等

数模转换:A/D,D/A转换器等

驱动接口:LED显示驱动器、I/O接口芯片、UART收发器等。

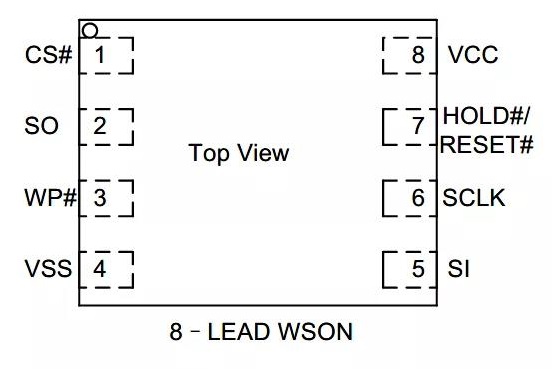

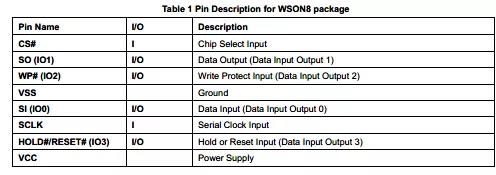

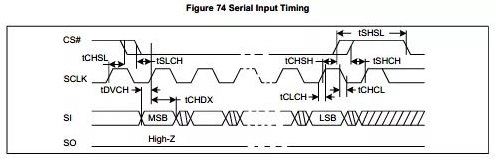

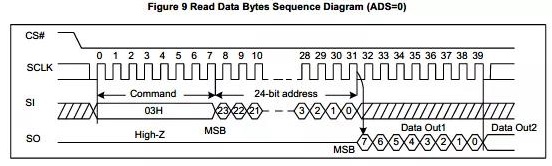

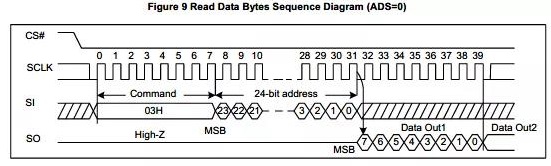

2017年哪类芯片最缺货啊?存储器相关的啊!好吧,就选它了:SPI Flash。SPI Flash的本质就是使用SPI的协议去对Flash 存储器进行各种读写操作。结合Flash有助于我们更好的理解SPI协议。

SPI是串行外设接口(Serial Peripheral Interface)的缩写。是 Motorola 公司推出的一 种同步串行接口技术,是一种高速的,全双工,同步的通信总线。

高速和同步可以理解,全双工是什么鬼?

全双工是指host(主设备)与外围从设备之间的发送线和接受线各自独立,发送数据的同时也能够接收数据,两者同步进行。

SPI协议主要用于短距离的通信系统中,特别是嵌入式系统,比如以下芯片:

存储器:RAM,EEPROM,Flash等

数模转换:A/D,D/A转换器等

驱动接口:LED显示驱动器、I/O接口芯片、UART收发器等。

2017年哪类芯片最缺货啊?存储器相关的啊!好吧,就选它了:SPI Flash。SPI Flash的本质就是使用SPI的协议去对Flash 存储器进行各种读写操作。结合Flash有助于我们更好的理解SPI协议。

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报