时钟源和RF & BB PLL频率综合器

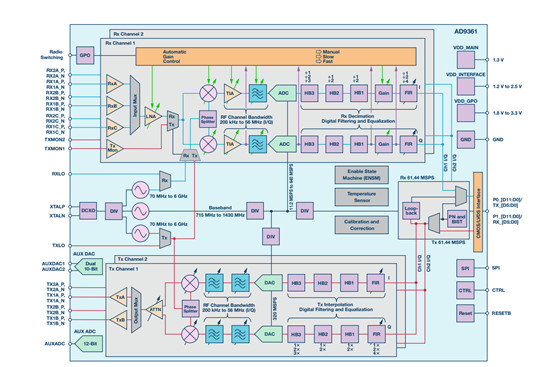

由于时钟是整个芯片的核心,在介绍上节所述五方面之前,我们先详述一下AD9361的时钟、PLL和频率综合器。

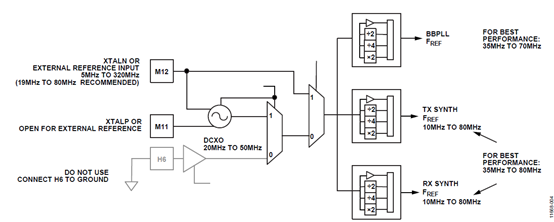

1、参考时钟及DCXO

AD9361使用分数分频锁相环生成一个本地时钟为信号转换、数字滤波器、IO端口提供时钟源。这些PLL均需要一个参考时钟,这个时钟可以通过外部晶振提供,或者由外部晶体加上一个可变电容生成所需频率。在使用外部晶体的情况下,需使用DCXO补偿晶体频率来保证输出参考时钟稳定。

2、RF & BB PLL 频率综合器

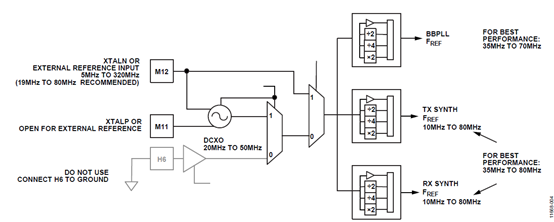

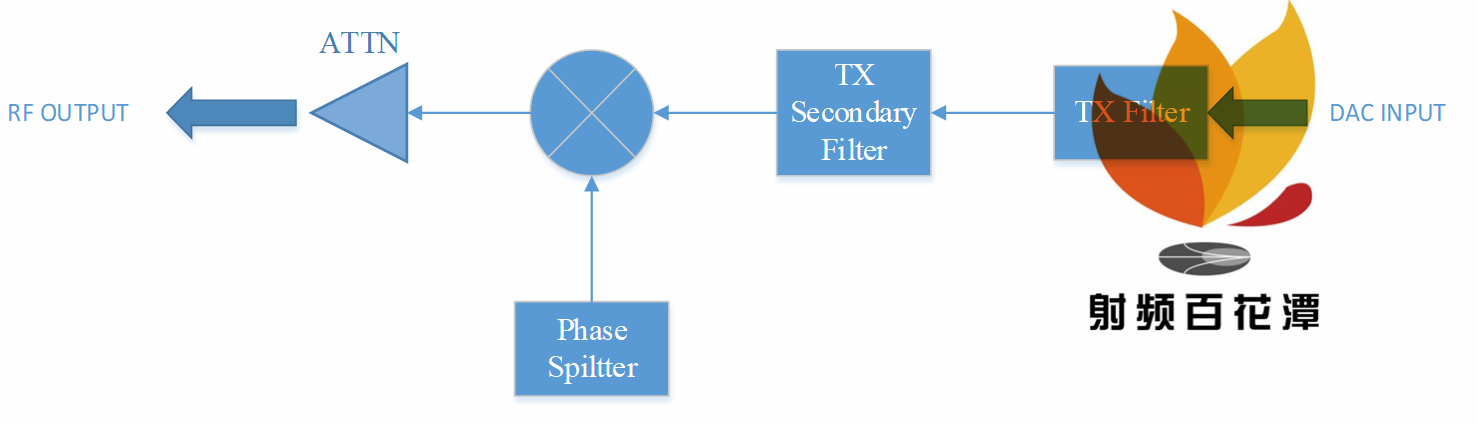

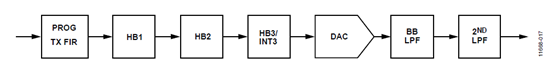

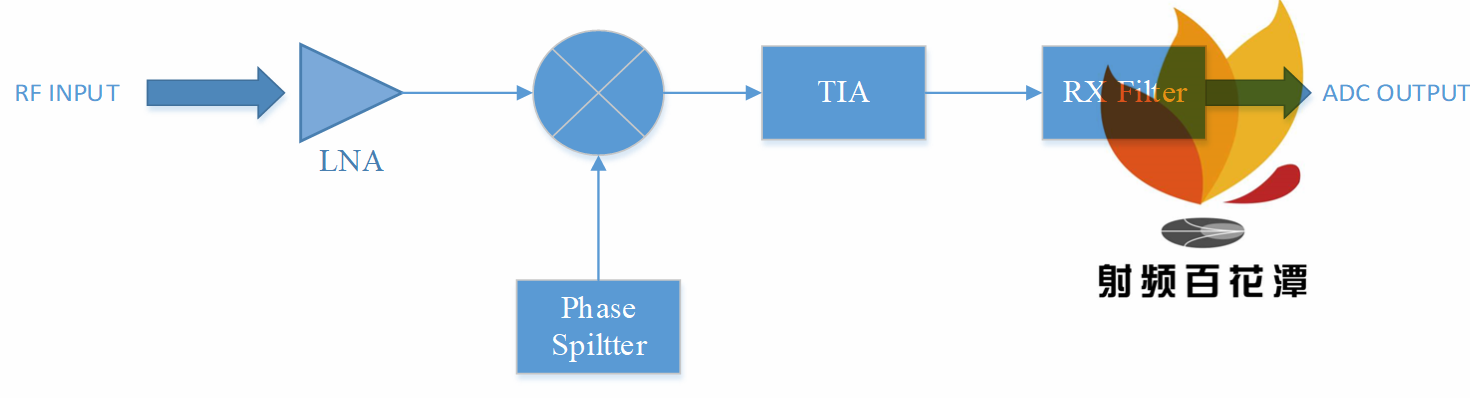

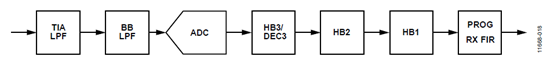

图4-1

参考时钟输入后,分别进入3个独立的PLL(如图4-1所示),分别为T/RX频率综合器、基带PLL提供参考时钟源。3个PLL需各自进行校准。

A)TX、RX PLL的锁定

在FDD模式下,TX和RX的PLL可工作在不同频率下,它们同时开启;TDD模式下,TX和RX的PLL根据收发情况轮流开启。

一般的TDD模式工作状态按照Rx-ALERT-Tx-ALERT-Rx跳转,基带通过跳转TXNRX信号来控制TX、RX状态的跳转,当TXNRX从0跳变到1时,RX PLL关闭,TX PLL开启并进行重新校准锁定,反之TX PLL关闭,RX PLL开启并重新校准锁定。TDD模式下每次PLL校准锁定的时间大概为45us~60us左右。

不过假如系统每次收发帧所使用的载波频率不变,则不需每次打开TX或RX时重新进行校准,而沿用上一次的校准值。此时需要在一次校准过后将寄存器中的VCO Cal比特关闭,这样可以明显得缩短信号收发之前,频率综合器的稳定时间。

B)Fast Lock模式

假如你的系统需要在多个频点上工作,则可以使用Fast Lock模式,它支持保存多个频点的频率控制字,使得频率变化是,PLL的锁定时间更短。然而这种模式TX和RX分别最多只能保存8个频点,还是有一点局限性。

时钟源和RF & BB PLL频率综合器

由于时钟是整个芯片的核心,在介绍上节所述五方面之前,我们先详述一下AD9361的时钟、PLL和频率综合器。

1、参考时钟及DCXO

AD9361使用分数分频锁相环生成一个本地时钟为信号转换、数字滤波器、IO端口提供时钟源。这些PLL均需要一个参考时钟,这个时钟可以通过外部晶振提供,或者由外部晶体加上一个可变电容生成所需频率。在使用外部晶体的情况下,需使用DCXO补偿晶体频率来保证输出参考时钟稳定。

2、RF & BB PLL 频率综合器

图4-1

参考时钟输入后,分别进入3个独立的PLL(如图4-1所示),分别为T/RX频率综合器、基带PLL提供参考时钟源。3个PLL需各自进行校准。

A)TX、RX PLL的锁定

在FDD模式下,TX和RX的PLL可工作在不同频率下,它们同时开启;TDD模式下,TX和RX的PLL根据收发情况轮流开启。

一般的TDD模式工作状态按照Rx-ALERT-Tx-ALERT-Rx跳转,基带通过跳转TXNRX信号来控制TX、RX状态的跳转,当TXNRX从0跳变到1时,RX PLL关闭,TX PLL开启并进行重新校准锁定,反之TX PLL关闭,RX PLL开启并重新校准锁定。TDD模式下每次PLL校准锁定的时间大概为45us~60us左右。

不过假如系统每次收发帧所使用的载波频率不变,则不需每次打开TX或RX时重新进行校准,而沿用上一次的校准值。此时需要在一次校准过后将寄存器中的VCO Cal比特关闭,这样可以明显得缩短信号收发之前,频率综合器的稳定时间。

B)Fast Lock模式

假如你的系统需要在多个频点上工作,则可以使用Fast Lock模式,它支持保存多个频点的频率控制字,使得频率变化是,PLL的锁定时间更短。然而这种模式TX和RX分别最多只能保存8个频点,还是有一点局限性。

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报