目前,随着

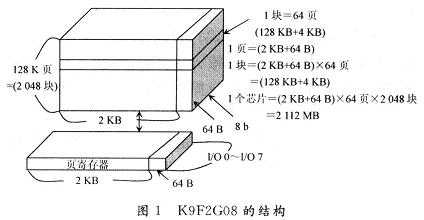

电子技术的不断发展,计算机技术也得到飞速的发展,产生了很多新技术。但就计算机的基本结构来说,还是基本采用了冯·诺依曼结构。然而冯·诺依曼结构的一个中心点就是存储一控制,所以存储器在计算机系统中的作用是非常重要的。嵌入式计算机作为计算机中的一个类别,对执行速度和系统可靠性都有较强的要求,这也决定了嵌入式系统不仅要有实时性很强的操作系统,同时也需要一种安全、快速的存储设备。同时,嵌入式系统经常会涉及到海量数据的存储,这就要求存储设备必须具有可靠性高,功耗低,容量大,掉电数据不丢失等特点,而NAND FLASH芯片正好具有这些优点。

举报

举报

举报

举报

举报

举报

举报

举报