3 结论

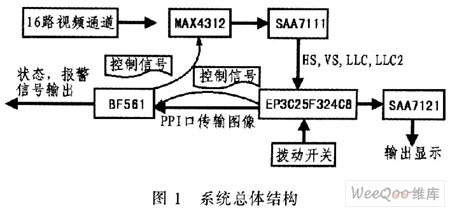

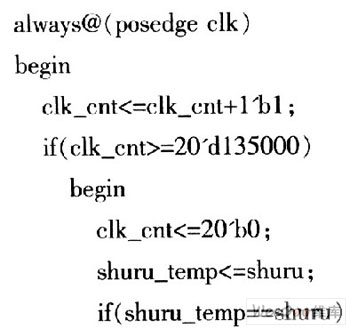

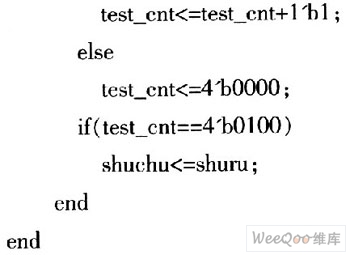

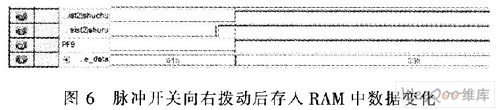

首先介绍了整个系统的工业背景和硬件架构,然后着重阐述了怎样在FPGA中处理开关控制信号,以达到可靠响应每个开关动作的目的。整个设计程序是在QuartusⅡ平台上用Verilog硬件描述语言编写,利用QuartusⅡ中的下载工具和SignalTapⅡLogic Analyzer工具进行下载、实时采样,并多次调试验证。本次设计已经成功应用于布机告警系统中,每次拨动开关都能准确、可靠的切换视频通道。虽然此系统中只有两种开关,但是整个程序的设计思想对多种开关控制也是通用的,只需在细节上稍作改变就能识别多种开关动作。

3 结论

首先介绍了整个系统的工业背景和硬件架构,然后着重阐述了怎样在FPGA中处理开关控制信号,以达到可靠响应每个开关动作的目的。整个设计程序是在QuartusⅡ平台上用Verilog硬件描述语言编写,利用QuartusⅡ中的下载工具和SignalTapⅡLogic Analyzer工具进行下载、实时采样,并多次调试验证。本次设计已经成功应用于布机告警系统中,每次拨动开关都能准确、可靠的切换视频通道。虽然此系统中只有两种开关,但是整个程序的设计思想对多种开关控制也是通用的,只需在细节上稍作改变就能识别多种开关动作。

举报

举报

举报

举报

举报

举报

举报

举报