同样,如果传感器子部分用低功耗模式实现且将关闭所有元件,则MCU可在有运动情况下用比较器中断唤醒。加速计输出可连接到比较器,确保只要一有运动就能唤醒器件,并触发主机处理器的事件。

就基于SoC构建的系统而言,还可采用其它技术来降低平均功耗。举例来说,所有外设的时钟都可设定为最慢的时钟频率,由于动态功耗与开关频率成正比,因此这么做就能节约耗电。再举例来说,SoC中的ADC的时钟频率通常应与所需的采样率成正比。如果ADC设置的采样率高于实际的系统需求,那就会造成不必要的电池负载。

还有其它一些系统级技巧可用来降低整体功耗。举例来说,器件输出可支持较低转换率以降低辐射。不过,较低转换率会导致FET的引脚驱动级消耗更多电流,因为PMOS和NMOS都会开启更长的时间。根据系统允许的辐射量,引脚的转换率高低可进行调节设置。

我们选择的器件如果能提供多种电源模式,而且能实现较高集成度,并对SoC的电源状态实现较好控制,这就能简化低功耗系统的实现过程。根据应用的不同,我们可有效利用不同的电源模式来确保较低的平均电流。虽然时钟频率较高会导致高功耗,但CPU暂时高频工作随后能更快地让器件返回休眠状态,这其实有助于实现更低的平均功耗。开发人员应考虑整体系统,尽可能避免出现漏电流路径。

同样,如果传感器子部分用低功耗模式实现且将关闭所有元件,则MCU可在有运动情况下用比较器中断唤醒。加速计输出可连接到比较器,确保只要一有运动就能唤醒器件,并触发主机处理器的事件。

就基于SoC构建的系统而言,还可采用其它技术来降低平均功耗。举例来说,所有外设的时钟都可设定为最慢的时钟频率,由于动态功耗与开关频率成正比,因此这么做就能节约耗电。再举例来说,SoC中的ADC的时钟频率通常应与所需的采样率成正比。如果ADC设置的采样率高于实际的系统需求,那就会造成不必要的电池负载。

还有其它一些系统级技巧可用来降低整体功耗。举例来说,器件输出可支持较低转换率以降低辐射。不过,较低转换率会导致FET的引脚驱动级消耗更多电流,因为PMOS和NMOS都会开启更长的时间。根据系统允许的辐射量,引脚的转换率高低可进行调节设置。

我们选择的器件如果能提供多种电源模式,而且能实现较高集成度,并对SoC的电源状态实现较好控制,这就能简化低功耗系统的实现过程。根据应用的不同,我们可有效利用不同的电源模式来确保较低的平均电流。虽然时钟频率较高会导致高功耗,但CPU暂时高频工作随后能更快地让器件返回休眠状态,这其实有助于实现更低的平均功耗。开发人员应考虑整体系统,尽可能避免出现漏电流路径。

举报

举报

举报

举报

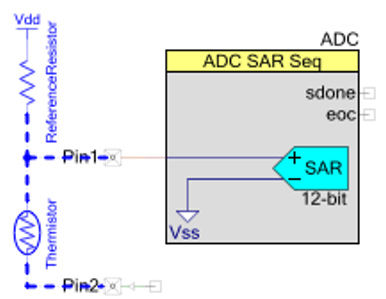

图4:典型的热敏电阻激励电路

图4:典型的热敏电阻激励电路 图5:面向低功耗的热敏电阻激励

图5:面向低功耗的热敏电阻激励

举报

举报

举报

举报