脑电信号采集系统主要包括信号放大与调理、模数转换、信号处理与传输等。由于人体的阻抗高且变化大,脑电信号又很微弱,外部环境的干扰很大,因此脑电信号采集系统的放大与调理电路比较复杂,通常要包括高输入阻抗和高共模抑制比的前级放大、带通滤波、工频陷波、多级放大等,导致体积大功耗高。

模数转换的精度和速率也决定了脑电信号采集系统的性能,采用10位的模数转换芯片,或者采用ADI公司最高采样率1.25 MBPS的12位AD1671芯片,或者采用16位模/数转换芯片。采用单片机、ARM和DSP作为控制器件的系统中,一般只能完成数据采集和处理较为单一的功能,其中以DSP的数据处理能力最强。

相比之下,采用FPGA 作为主控芯片通过硬件描述语言编程可以灵活地进行配置,实现对多通道数据的并行处理,同时能将多个功能在单芯片上实现,基于FGPA和ADS1258设计了集成有视觉、听觉和体感刺激信号源与16通道脑电信号采集功能的诱发电位仪。脑电信号传输的手段以PCI总线、USB等有线方式为主,无线方式传输速率较低,但更易于便携式设计,因此可以针对特定的应用。

ADS1298是TI公司近年推出的一款针对心电和脑电信号采集的24位专用模数转换芯片,本文利用该芯片的高精度,以FPGA为主控制芯片,通过将工频陷波、带通滤波等模拟部分转移到数字侧,在保证性能的前提下简化脑电信号放大与调理的模拟电路,实现便携式脑电信号的采集。

1 系统结构

本文提出的脑电信号采集系统包括信号采集、模数转换和数据传输三个部分。脑电信号采集系统的总体框图如图1所示。

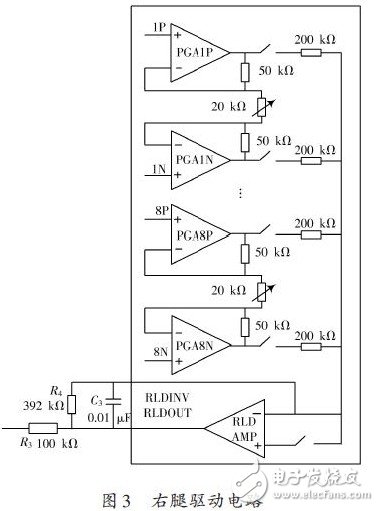

预处理电路包含RC低通滤波和过压保护电路,对脑电极采集到的信号进行低通滤波和过压保护后直接送入到ADS1298模数转换器中进行模/数转换。右腿驱动电路主要是用来抑制共模干扰,由ADS1298 内部的RLD电路以及外部的电容电阻构成的反向放大滤波电路组成。

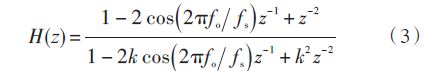

系统采用FPGA作为主控制芯片,利用硬件描述性语言来编写配置I/O 口成通用串行SPI接口,与高精度多通道的模数转换芯片ADS1298 的SPI 接口相连实现通信,从而控制ADS1298 将脑电极采集到的模拟信号转换为数字信号,经过滤波陷波处理后存储在SDRAM中,作为采集数据的缓冲部分,以便为后续的传输模块做准备。

数据传输模块主要是采用FPGA配置I/O口作为以太网接口芯片DM9000A的控制接口,并与DM9000A的控制接口串联,实现其逻辑控制;采用UDP 协议将从SDRAM中读取的数据打包,通过RJ45网络接口,传输到上位机。8个通道1 kHz的采样率,理论上需要192 Kb/s的传输速率,以太网口10/100M的传输速率完全能满足需要。

脑电信号采集系统主要包括信号放大与调理、模数转换、信号处理与传输等。由于人体的阻抗高且变化大,脑电信号又很微弱,外部环境的干扰很大,因此脑电信号采集系统的放大与调理电路比较复杂,通常要包括高输入阻抗和高共模抑制比的前级放大、带通滤波、工频陷波、多级放大等,导致体积大功耗高。

模数转换的精度和速率也决定了脑电信号采集系统的性能,采用10位的模数转换芯片,或者采用ADI公司最高采样率1.25 MBPS的12位AD1671芯片,或者采用16位模/数转换芯片。采用单片机、ARM和DSP作为控制器件的系统中,一般只能完成数据采集和处理较为单一的功能,其中以DSP的数据处理能力最强。

相比之下,采用FPGA 作为主控芯片通过硬件描述语言编程可以灵活地进行配置,实现对多通道数据的并行处理,同时能将多个功能在单芯片上实现,基于FGPA和ADS1258设计了集成有视觉、听觉和体感刺激信号源与16通道脑电信号采集功能的诱发电位仪。脑电信号传输的手段以PCI总线、USB等有线方式为主,无线方式传输速率较低,但更易于便携式设计,因此可以针对特定的应用。

ADS1298是TI公司近年推出的一款针对心电和脑电信号采集的24位专用模数转换芯片,本文利用该芯片的高精度,以FPGA为主控制芯片,通过将工频陷波、带通滤波等模拟部分转移到数字侧,在保证性能的前提下简化脑电信号放大与调理的模拟电路,实现便携式脑电信号的采集。

1 系统结构

本文提出的脑电信号采集系统包括信号采集、模数转换和数据传输三个部分。脑电信号采集系统的总体框图如图1所示。

预处理电路包含RC低通滤波和过压保护电路,对脑电极采集到的信号进行低通滤波和过压保护后直接送入到ADS1298模数转换器中进行模/数转换。右腿驱动电路主要是用来抑制共模干扰,由ADS1298 内部的RLD电路以及外部的电容电阻构成的反向放大滤波电路组成。

系统采用FPGA作为主控制芯片,利用硬件描述性语言来编写配置I/O 口成通用串行SPI接口,与高精度多通道的模数转换芯片ADS1298 的SPI 接口相连实现通信,从而控制ADS1298 将脑电极采集到的模拟信号转换为数字信号,经过滤波陷波处理后存储在SDRAM中,作为采集数据的缓冲部分,以便为后续的传输模块做准备。

数据传输模块主要是采用FPGA配置I/O口作为以太网接口芯片DM9000A的控制接口,并与DM9000A的控制接口串联,实现其逻辑控制;采用UDP 协议将从SDRAM中读取的数据打包,通过RJ45网络接口,传输到上位机。8个通道1 kHz的采样率,理论上需要192 Kb/s的传输速率,以太网口10/100M的传输速率完全能满足需要。

举报

举报

举报

举报

2.3 FPGA接口电路

2.3 FPGA接口电路

举报

举报

举报

举报

举报

举报