RF收发器 基带处理器 无线系统

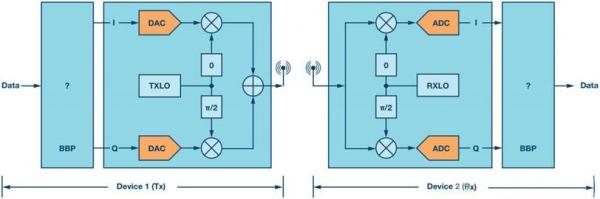

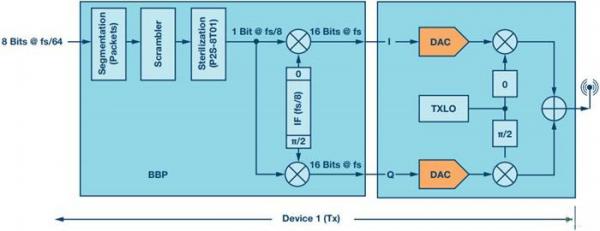

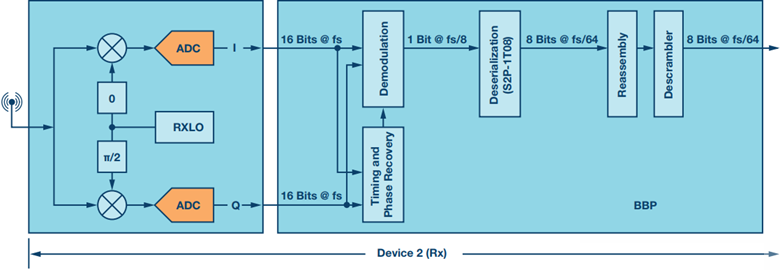

如今,无线系统无处不在,无线设备和服务的数量持续增长。设计完整的RF系统是一项跨学科设计挑战,模拟RF前端是其中最关键的部分。然而, AD9361 等集成RF收发器的推出显著减少了此类设计的RF挑战。这些收发器可为模拟RF信号链提供数字接口,允许轻松集成到ASIC或FPGA ,进行基带处理。基带处理器(BBP)允许在终端应用和收发器设备之间的数字域中处理用户数据。

回帖 (3)

2019-9-19 16:01:40

2019-9-19 16:02:09

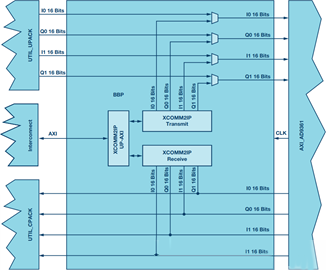

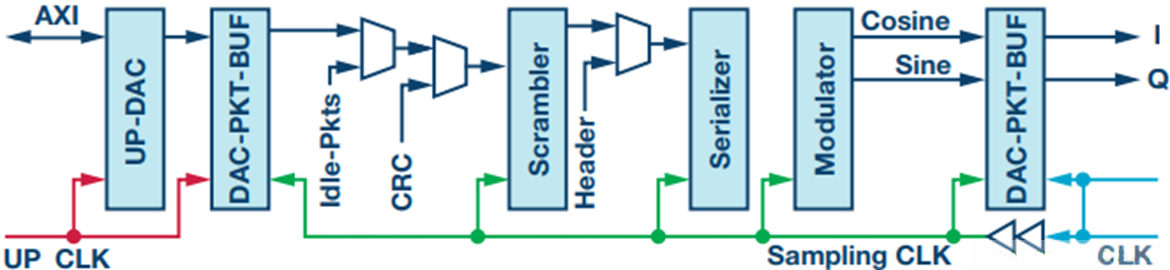

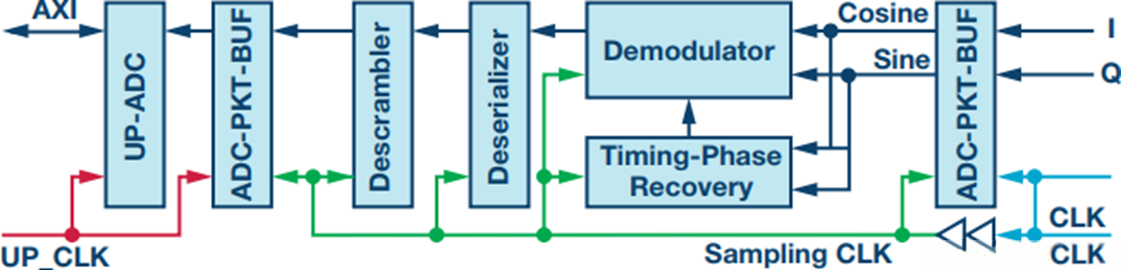

实现 BBP设计在硬件中实施和测试。硬件是两个评估板的组合:具有Zynq FPGA设备的Xilinx ZC706评估板,以及具有AD9361收发器的AD-FMCOMMS3-EBZ评估板。ADI提供支持该硬件的完整参考设计。该开源设计在主要工具版本中免费提供,可获得完全支持和更新。硬件详细信息参见下列URL: ZC706 AD-FMCOMMS3-EBZ Zynq SOC AD9361 ADI GitHub库 ZC706 和 AD-FMCOMMS3-EBZ HDL参考设计 AXI AD9361 IP ADI参考设计是支持Linux®框架的嵌入式系统。包含围绕ARM®处理器的各种外设。AD9361设备连接到 axi_AD9361 IP外设。它在RF设备和系统存储器之间传输原始采样数据。 外设和设备通过Linux内核驱动程序进行初始化和控制。BBP则作为连接到 axi_AD9361的另一个IP外设。出于历史原因,BBP IP命名为 axi_xcomm2ip 。Linux中的用户空间应用程序用于在系统之间控制、发送和接收数据。 在ADI参考设计中,在发送方向,axi_AD9361 IP连接到解包模块(util_upack),在接收方向,连接到打包模块(util_cpack)。 在发送方向,BBP数据插入解包模块和AD9361内核之间。为了使其不影响默认数据路径,BBP支持可选的数据路径多路复用器,以选择解包数据源或BBP数据源。BBP允许参考设计数据路径作为默认路径,并仅在启用时选择BBP数据源。在接收方向,BBP仅连接到AD9361内核。参考设计数据路径不受影响。这允许框架不受妨碍地引导和设置系统。在系统设置后,启用BBP,可通过覆盖默认数据路径来进行数据传输。以ADI参考设计实施的BBP的框图如图4所示。 图4. BBP IP框图 本文中讨论的设计、初始化和数据传输使用一对这种硬件。设置仅需一对HDMI®监视器、键盘和鼠标及天线。系统彼此完全不同步,但需要相同设置。在每个方向,数据在不同载波上传输。设备1的发射载波频率和设备2的接收载波频率相同,但在另一个方向上不同。然而,如果回送中使用单个设备,发射和接收载波必须具有相同的频率。BBP的HDL设计采用ADI库模块。 控制(微处理器)接口 AXI-Lite接口用于通过处理器控制和监控BBP。使用ADI公共库(hdl/library/common/up_axi.v)中的up_axi模块,可以轻松推断该接口模块。该模块将AXI-Lite接口转换为简单内存,如读取和写入总线。和任何其他ADI IP一样,添加内部寄存器和内存。寄存器映射如表1所示。 表1. BBP寄存器映射 up_axi: 模块端口及其端口映射如下所述。 up_rstn: AXI接口复位(异步低电平有效),连接到 s_axi_aresetn. up_clk: AXI接口时钟,连接到 s_axi_aclk. up_axi_*: AXI接口信号,连接到等效 s_axi_* 端口 up_wreq, up_waddr, up_wdata, up_wack: 内部写入接口, the up_wreq 信号与地址和数据一同置位,以指示写入请求。请求需要通过up_wack 端口应答。 如下所示,实施简单的寄存器写入。 always @(negedge up_rstn or posedge up_clk) begin if (up_rstn == 0) begin up_wack <= ''d0; up_reg0 <= UP_REG0_RESET_VALUE; end else begin up_wack <= up_wreq_s; if ((up_wreq_s == 1''b1) && (up_waddr == UP_ REG0_ADDRESS)) begin up_reg0 <= up_wdata[UP_REG0_WIDTH-1:0]; end end end 模块在二者之间执行地址转换。AXI接口使用字节地址,但内部总线使用DWORD地址。结果是,up_axi模块丢弃AXI地址的两个最低有效位,以生成内部DWORD地址。 up_rreq, up_raddr, up_rdata, up_rack: 内部读取接口, up_rreq 信号与地址一同置位,以指示读取请求。请求需要与读取数据一同通过 up_rack 端口应答。 如下所示,实施与上述相同的寄存器用于读取。 always @(negedge up_rstn or posedge up_clk) begin if (up_rstn == 0) begin up_rack <= ''d0; up_rdata <= ''d0; end else begin up_rack <= up_rreq_s; if ((up_rreq_s == 1''b1) && (up_raddr == UP_ REG0_ADDRESS)) begin up_rdata <= up_reg0; end else begin up_rdata <= 32''d0; end end end 相同地址转换也适用于读取。读取数据仅在请求时驱动,否则设置为零。这是因为up_axi模块将单个读取数据从各个地址组传递到OR门。因此,未选择的地址组需要驱动读取数据零。 如上方寄存器映射表中所列,BBP有三个地址空间。常见寄存器空间映射至0x000、发送(DAC)映射至0x800 (0x200),接收(ADC)映射至0xC00 (0x300)。软件(Linux用户空间应用程序)应当将发送数据包数据写入缓冲器,并从另一个缓冲器中读取接收到的数据包数据。数据包大小选择为32字节,带有3字节前同步码和1字节CRC。 数据接口 对于接收和发送方向的两个通道,AD9361接口内核包含两对16位I/Q数据。内核按照与AD9361数字接口相同的时钟运行。在2R2T模式下,这是采样速率的4倍。在1R1T模式下,这是采样速率的2倍。有效数据速率由有效信号控制。因此在2R2T模式下,每4个时钟置位一次有效。在1R1T模式下,每2个时钟置位一次有效。BBP旨在支持2R2T和1R1T模式。它使用单个发送和接收通道。内部逻辑在2R2T和1R1T模式下以采样速率运行。然后,BBP在其时钟频率下,通过接口内核传输数据。这样是为了在BBP内演示时钟转换。在许多情况下,用户可能希望无论收发器的接口速率如何,都能在采样速率下运行BBP逻辑。 使用Xilinx基元BUFR和BUFG,生成采样频率内部时钟。BUFR是分压器,BUFG是高扇出时钟缓冲器。为此,也可以使用MMCM。如下所示,生成内部时钟。 parameter XCOMM2IP_1T1R_OR_2T2R_N = 0; localparam XCOMM2IP_SCLK_DIVIDE = (XCOMM2IP_1T1R_OR_2T2R_N == 1) ? "2" : "4"; BUFR #(.BUFR_DIVIDE(XCOMM2IP_SCLK_DIVIDE)) i_bufr ( .CLR (1''b0), .CE (1''b1), .I (clk), .O (s_clk_s)); BUFG i_bufg ( .I (s_clk_s), .O (s_clk)); 使用BUFR和BUFG可确保时钟频率锁定,但会影响相位确定性。最大相位不确定性是单个接口时钟周期。通过带有同步信号的四级寄存器阵列,可以轻松补偿该不确定性。然而,设计采用了双端口RAM模块来实现数据传输。这也是为了展示常见信号处理要求的应用实例。使用ADI库内存模块(ad_mem)可以推断出双端口RAM元件。

实现 BBP设计在硬件中实施和测试。硬件是两个评估板的组合:具有Zynq FPGA设备的Xilinx ZC706评估板,以及具有AD9361收发器的AD-FMCOMMS3-EBZ评估板。ADI提供支持该硬件的完整参考设计。该开源设计在主要工具版本中免费提供,可获得完全支持和更新。硬件详细信息参见下列URL: ZC706 AD-FMCOMMS3-EBZ Zynq SOC AD9361 ADI GitHub库 ZC706 和 AD-FMCOMMS3-EBZ HDL参考设计 AXI AD9361 IP ADI参考设计是支持Linux®框架的嵌入式系统。包含围绕ARM®处理器的各种外设。AD9361设备连接到 axi_AD9361 IP外设。它在RF设备和系统存储器之间传输原始采样数据。 外设和设备通过Linux内核驱动程序进行初始化和控制。BBP则作为连接到 axi_AD9361的另一个IP外设。出于历史原因,BBP IP命名为 axi_xcomm2ip 。Linux中的用户空间应用程序用于在系统之间控制、发送和接收数据。 在ADI参考设计中,在发送方向,axi_AD9361 IP连接到解包模块(util_upack),在接收方向,连接到打包模块(util_cpack)。 在发送方向,BBP数据插入解包模块和AD9361内核之间。为了使其不影响默认数据路径,BBP支持可选的数据路径多路复用器,以选择解包数据源或BBP数据源。BBP允许参考设计数据路径作为默认路径,并仅在启用时选择BBP数据源。在接收方向,BBP仅连接到AD9361内核。参考设计数据路径不受影响。这允许框架不受妨碍地引导和设置系统。在系统设置后,启用BBP,可通过覆盖默认数据路径来进行数据传输。以ADI参考设计实施的BBP的框图如图4所示。 图4. BBP IP框图 本文中讨论的设计、初始化和数据传输使用一对这种硬件。设置仅需一对HDMI®监视器、键盘和鼠标及天线。系统彼此完全不同步,但需要相同设置。在每个方向,数据在不同载波上传输。设备1的发射载波频率和设备2的接收载波频率相同,但在另一个方向上不同。然而,如果回送中使用单个设备,发射和接收载波必须具有相同的频率。BBP的HDL设计采用ADI库模块。 控制(微处理器)接口 AXI-Lite接口用于通过处理器控制和监控BBP。使用ADI公共库(hdl/library/common/up_axi.v)中的up_axi模块,可以轻松推断该接口模块。该模块将AXI-Lite接口转换为简单内存,如读取和写入总线。和任何其他ADI IP一样,添加内部寄存器和内存。寄存器映射如表1所示。 表1. BBP寄存器映射 up_axi: 模块端口及其端口映射如下所述。 up_rstn: AXI接口复位(异步低电平有效),连接到 s_axi_aresetn. up_clk: AXI接口时钟,连接到 s_axi_aclk. up_axi_*: AXI接口信号,连接到等效 s_axi_* 端口 up_wreq, up_waddr, up_wdata, up_wack: 内部写入接口, the up_wreq 信号与地址和数据一同置位,以指示写入请求。请求需要通过up_wack 端口应答。 如下所示,实施简单的寄存器写入。 always @(negedge up_rstn or posedge up_clk) begin if (up_rstn == 0) begin up_wack <= ''d0; up_reg0 <= UP_REG0_RESET_VALUE; end else begin up_wack <= up_wreq_s; if ((up_wreq_s == 1''b1) && (up_waddr == UP_ REG0_ADDRESS)) begin up_reg0 <= up_wdata[UP_REG0_WIDTH-1:0]; end end end 模块在二者之间执行地址转换。AXI接口使用字节地址,但内部总线使用DWORD地址。结果是,up_axi模块丢弃AXI地址的两个最低有效位,以生成内部DWORD地址。 up_rreq, up_raddr, up_rdata, up_rack: 内部读取接口, up_rreq 信号与地址一同置位,以指示读取请求。请求需要与读取数据一同通过 up_rack 端口应答。 如下所示,实施与上述相同的寄存器用于读取。 always @(negedge up_rstn or posedge up_clk) begin if (up_rstn == 0) begin up_rack <= ''d0; up_rdata <= ''d0; end else begin up_rack <= up_rreq_s; if ((up_rreq_s == 1''b1) && (up_raddr == UP_ REG0_ADDRESS)) begin up_rdata <= up_reg0; end else begin up_rdata <= 32''d0; end end end 相同地址转换也适用于读取。读取数据仅在请求时驱动,否则设置为零。这是因为up_axi模块将单个读取数据从各个地址组传递到OR门。因此,未选择的地址组需要驱动读取数据零。 如上方寄存器映射表中所列,BBP有三个地址空间。常见寄存器空间映射至0x000、发送(DAC)映射至0x800 (0x200),接收(ADC)映射至0xC00 (0x300)。软件(Linux用户空间应用程序)应当将发送数据包数据写入缓冲器,并从另一个缓冲器中读取接收到的数据包数据。数据包大小选择为32字节,带有3字节前同步码和1字节CRC。 数据接口 对于接收和发送方向的两个通道,AD9361接口内核包含两对16位I/Q数据。内核按照与AD9361数字接口相同的时钟运行。在2R2T模式下,这是采样速率的4倍。在1R1T模式下,这是采样速率的2倍。有效数据速率由有效信号控制。因此在2R2T模式下,每4个时钟置位一次有效。在1R1T模式下,每2个时钟置位一次有效。BBP旨在支持2R2T和1R1T模式。它使用单个发送和接收通道。内部逻辑在2R2T和1R1T模式下以采样速率运行。然后,BBP在其时钟频率下,通过接口内核传输数据。这样是为了在BBP内演示时钟转换。在许多情况下,用户可能希望无论收发器的接口速率如何,都能在采样速率下运行BBP逻辑。 使用Xilinx基元BUFR和BUFG,生成采样频率内部时钟。BUFR是分压器,BUFG是高扇出时钟缓冲器。为此,也可以使用MMCM。如下所示,生成内部时钟。 parameter XCOMM2IP_1T1R_OR_2T2R_N = 0; localparam XCOMM2IP_SCLK_DIVIDE = (XCOMM2IP_1T1R_OR_2T2R_N == 1) ? "2" : "4"; BUFR #(.BUFR_DIVIDE(XCOMM2IP_SCLK_DIVIDE)) i_bufr ( .CLR (1''b0), .CE (1''b1), .I (clk), .O (s_clk_s)); BUFG i_bufg ( .I (s_clk_s), .O (s_clk)); 使用BUFR和BUFG可确保时钟频率锁定,但会影响相位确定性。最大相位不确定性是单个接口时钟周期。通过带有同步信号的四级寄存器阵列,可以轻松补偿该不确定性。然而,设计采用了双端口RAM模块来实现数据传输。这也是为了展示常见信号处理要求的应用实例。使用ADI库内存模块(ad_mem)可以推断出双端口RAM元件。

举报

2019-9-19 16:02:16

更多回帖

举报

举报

举报

举报

举报

举报