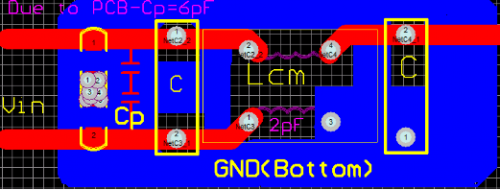

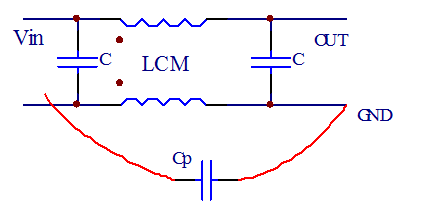

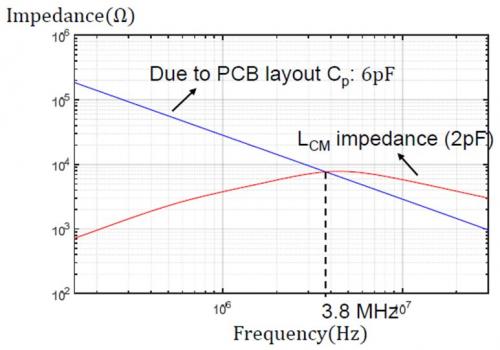

2.比如系统的设计LCM器件的杂散电容为2pF;其谐振频率点在4MHZ左右;进行PCB的铺地铜的设计由于PCB的布线,其输入的走线与PCB的铺地铜带来有6pF的耦合电容参数;在其LCM的谐振点后就会降低其阻抗值-如上图的频率&阻抗特性曲线参考数据;在进行EMI测试时就会带来高频>4MHZ的高频EMI的问题!

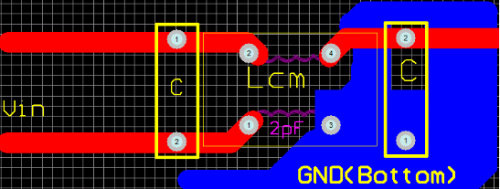

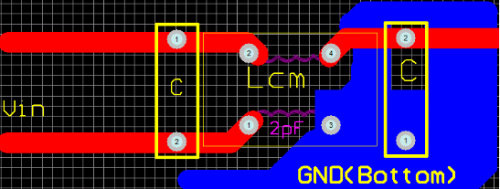

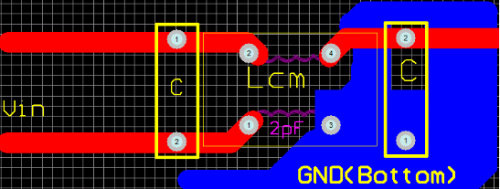

3.在进行PCB双面板布线铺铜地的设计时;在某些电路设计中改进PCB布局及走线就可以降低高频的EMI电磁干扰;简单优化的PCB设计参考如下:

注意:如果接地层存在噪声耦合源,则接地层不应靠近敏感输入电路。

2.比如系统的设计LCM器件的杂散电容为2pF;其谐振频率点在4MHZ左右;进行PCB的铺地铜的设计由于PCB的布线,其输入的走线与PCB的铺地铜带来有6pF的耦合电容参数;在其LCM的谐振点后就会降低其阻抗值-如上图的频率&阻抗特性曲线参考数据;在进行EMI测试时就会带来高频>4MHZ的高频EMI的问题!

3.在进行PCB双面板布线铺铜地的设计时;在某些电路设计中改进PCB布局及走线就可以降低高频的EMI电磁干扰;简单优化的PCB设计参考如下:

注意:如果接地层存在噪声耦合源,则接地层不应靠近敏感输入电路。

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报