实验结果

从本质上讲,文中所述的嵌入式自动指纹识别系统是一种高性能图像处理应用,因为它拥有大量的并行性,且需要实时认证响应。从人机工程角度上讲,此系统可使每位用户的认证时间不超过2s或3s。

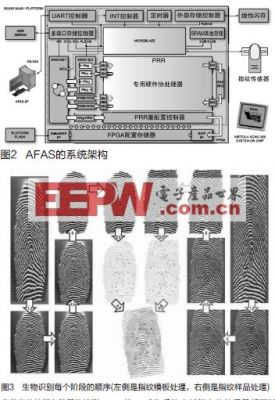

该设计流程涉及多个开发环路。首先,我们在PC平台上的MATLAB的软件里开发算法。随后,我们将软件代码用C编程语言导入到嵌入式软件中,并且首先在同一PC上执行,以确认我们能够获得同样的结果,然后在FPGA器件内合成的MicroBlaze嵌入式微处理器上执行。

通过这种方式,Virtex-4器件可在不使用任何定制硬件协处理器和不达到实时性能要求的情况下实施基于MicroBlaze的纯软件解决方案。为缩短运行时间,我们根据任务概要,下一步工作是引入PRR,并在上面构建各种定制生物识别协处理器,使用硬件/软件协同设计解决方案。此刻,我们已经采用C编程语言和VHDL硬件描述语言完成了此系统的开发工作。

我们采用268x460像素的8位灰度指纹图像进行了一些识别测试。同时,我们在基于Virtex-4的PR系统上和运行速度为1.83GHz的IntelCore2DuoT5600处理器的个人电脑上也进行了相同的测试。然后,我们运行相同的算法,包括纯软件实施方式和软硬件混合实施方式,以比较登录和识别阶段的性能。

如果不考虑采集工作(由于扫描传感器的性能限制,需以5ms积分时间采集100片并在运行中重构图像,故采集时间固定为500ms),PR方法可以把运行其他处理任务所形成的延迟降低到205ms。与在PC上运行纯软件方法的3,274ms的延迟相比,PR方法可提高16倍速度。

因此,表1说明运用并行和流水线技术进行软硬件协同设计,同时配合低重配置延迟的PR技术,明显实现实时认证是可行的。另外,在动态重配置时,可以指定模块运行的频率,这个频率是由新模块的特性所决定。在我们的设计中,所有模块运行在50MHz或者100MHz的频率下。

此外,重配置流程一直以100MHz运行,在每个时钟周期里传输32位比特,从而保证Virtex-4上的最低重配置延迟。根据每个PRR硬件环境的比特流复杂性,每个重配置流程花费的时间在0.8ms(例如标准化)和1.1ms(例如二进制化)之间。与生物识别应用的总体运行时间相比,该重配置时间可忽略不计。

由于我们已经成功完成了概念验证工作,我们准备把原型导出到新一代赛灵思低端具有PR功能的28纳米FPGA器件中(Artix-7系列)。我们的目标是以最低的成本设计出一款能够在任何消费类电子产品中嵌入高性能且真正安全的生物识别系统。

实验结果

从本质上讲,文中所述的嵌入式自动指纹识别系统是一种高性能图像处理应用,因为它拥有大量的并行性,且需要实时认证响应。从人机工程角度上讲,此系统可使每位用户的认证时间不超过2s或3s。

该设计流程涉及多个开发环路。首先,我们在PC平台上的MATLAB的软件里开发算法。随后,我们将软件代码用C编程语言导入到嵌入式软件中,并且首先在同一PC上执行,以确认我们能够获得同样的结果,然后在FPGA器件内合成的MicroBlaze嵌入式微处理器上执行。

通过这种方式,Virtex-4器件可在不使用任何定制硬件协处理器和不达到实时性能要求的情况下实施基于MicroBlaze的纯软件解决方案。为缩短运行时间,我们根据任务概要,下一步工作是引入PRR,并在上面构建各种定制生物识别协处理器,使用硬件/软件协同设计解决方案。此刻,我们已经采用C编程语言和VHDL硬件描述语言完成了此系统的开发工作。

我们采用268x460像素的8位灰度指纹图像进行了一些识别测试。同时,我们在基于Virtex-4的PR系统上和运行速度为1.83GHz的IntelCore2DuoT5600处理器的个人电脑上也进行了相同的测试。然后,我们运行相同的算法,包括纯软件实施方式和软硬件混合实施方式,以比较登录和识别阶段的性能。

如果不考虑采集工作(由于扫描传感器的性能限制,需以5ms积分时间采集100片并在运行中重构图像,故采集时间固定为500ms),PR方法可以把运行其他处理任务所形成的延迟降低到205ms。与在PC上运行纯软件方法的3,274ms的延迟相比,PR方法可提高16倍速度。

因此,表1说明运用并行和流水线技术进行软硬件协同设计,同时配合低重配置延迟的PR技术,明显实现实时认证是可行的。另外,在动态重配置时,可以指定模块运行的频率,这个频率是由新模块的特性所决定。在我们的设计中,所有模块运行在50MHz或者100MHz的频率下。

此外,重配置流程一直以100MHz运行,在每个时钟周期里传输32位比特,从而保证Virtex-4上的最低重配置延迟。根据每个PRR硬件环境的比特流复杂性,每个重配置流程花费的时间在0.8ms(例如标准化)和1.1ms(例如二进制化)之间。与生物识别应用的总体运行时间相比,该重配置时间可忽略不计。

由于我们已经成功完成了概念验证工作,我们准备把原型导出到新一代赛灵思低端具有PR功能的28纳米FPGA器件中(Artix-7系列)。我们的目标是以最低的成本设计出一款能够在任何消费类电子产品中嵌入高性能且真正安全的生物识别系统。

举报

举报

举报

举报

举报

举报

举报

举报