4. 小结

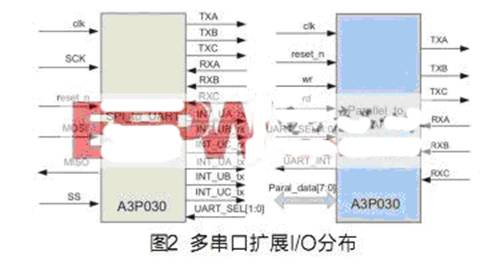

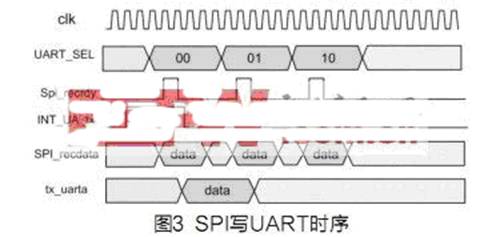

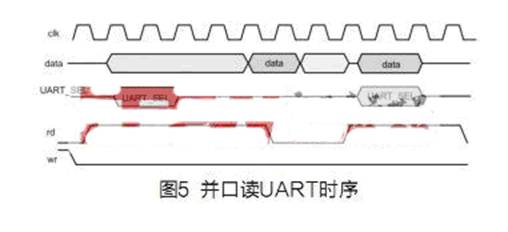

本文主要介绍了基于Actel A3P030的多串口扩展设计,可实现并行总线或SPI接口的UART扩展,该方案具有体积小、低功耗、低系统成本、高度可靠性和安全性以及高度的设计灵活性等特点,是在多串口应用中取代其他花费高昂成本的专用UART扩展芯片的最佳解决方案。我们有着一个接近30人的FPGA团队提供强有力的售后服务和技术支持,解决用户在产品使用和研发过程中遇到的困难。若有更多的需求可以与我们联系,我们将会竭诚为您服务,敬请关注下期的FPGA专题技术讲座。

4. 小结

本文主要介绍了基于Actel A3P030的多串口扩展设计,可实现并行总线或SPI接口的UART扩展,该方案具有体积小、低功耗、低系统成本、高度可靠性和安全性以及高度的设计灵活性等特点,是在多串口应用中取代其他花费高昂成本的专用UART扩展芯片的最佳解决方案。我们有着一个接近30人的FPGA团队提供强有力的售后服务和技术支持,解决用户在产品使用和研发过程中遇到的困难。若有更多的需求可以与我们联系,我们将会竭诚为您服务,敬请关注下期的FPGA专题技术讲座。

举报

举报

举报

举报

举报

举报

举报

举报