时隔不到一年,赛灵思即宣布推出领域目标设计平台(即六大针对特定领域的优化开发套件),令设计人员更直观的感受目标设计平台带来的优势,并让一些从未使用过FPGA的工程师可以借助FPGA进行开发。

全新套件面向Virtex-6 和 Spartan-6 系列产品线,主要针对嵌入式处理、DSP以及连接功能三大领域,并集合了最新优化的ISE开发工具及开发板、全功能 IP 以及适合设计人员专业技术领域的通用的目标参考设计。区别于基础平台,领域设计平台所提供的参考设计更接近产品本身。赛灵思平台市场营销总监 Brent Przybus表示:“客户在设计时可以直接把这个参考设计量产,它是非常接近量产的一种参考设计。”

Brent Przybus还指出:“每款新套件都提供了经验证的设计出发点,设计人员借此可以加速产品上市进程,同时还能获得他们所需的工具,以确保能专注于产品的创新工作。赛灵思为设计人员提供了全套精心优化的开发资源,可帮助他们快速启动设计工作,并最大限度地利用 Virtex-6 和 Spartan-6 FPGA 系列的真正创新功能和特性。”

连接功能套件

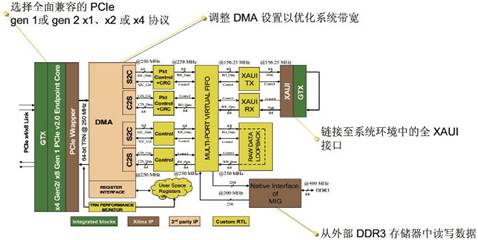

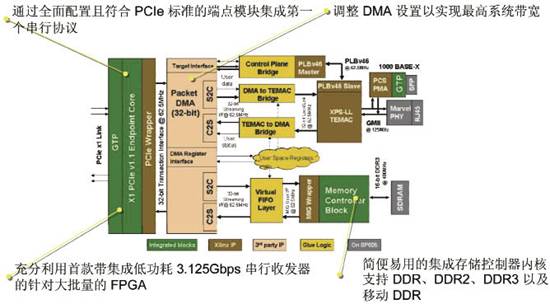

连接开发套件包含目标参考设计,其将FPGA 内的硬件模块、赛灵思连接 IP 以及赛灵思联盟计划重要成员Northwest Logic公司提供的DMA IP整合在一起,提供全面可扩展的 PCIe 到 XAUI 或千兆位以太网的桥接器。

嵌入式开发套件

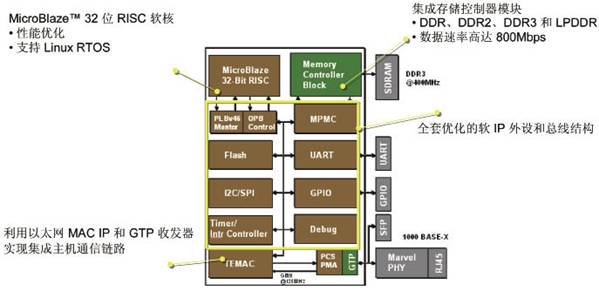

嵌入式开发套件帮助软件开发人员利用与ISE 11.4嵌入式版本一起提供的赛灵思 SDK(软件开发套件)环境立即启动开发工作。开发人员能运行并修改作为目标参考设计的一部分所提供的代码样本,充分利用全面实施的 MicroBlaze 32 位 RISC 软处理器内核和全套常见处理器外设,包括 UART、多端口存储控制器 (MPMC)、闪存、三态以太网 MAC (TEMAC)、通用 IP (GPIO)、I2C/SPI、定时器/中断控制器及调试端口等。

时隔不到一年,赛灵思即宣布推出领域目标设计平台(即六大针对特定领域的优化开发套件),令设计人员更直观的感受目标设计平台带来的优势,并让一些从未使用过FPGA的工程师可以借助FPGA进行开发。

全新套件面向Virtex-6 和 Spartan-6 系列产品线,主要针对嵌入式处理、DSP以及连接功能三大领域,并集合了最新优化的ISE开发工具及开发板、全功能 IP 以及适合设计人员专业技术领域的通用的目标参考设计。区别于基础平台,领域设计平台所提供的参考设计更接近产品本身。赛灵思平台市场营销总监 Brent Przybus表示:“客户在设计时可以直接把这个参考设计量产,它是非常接近量产的一种参考设计。”

Brent Przybus还指出:“每款新套件都提供了经验证的设计出发点,设计人员借此可以加速产品上市进程,同时还能获得他们所需的工具,以确保能专注于产品的创新工作。赛灵思为设计人员提供了全套精心优化的开发资源,可帮助他们快速启动设计工作,并最大限度地利用 Virtex-6 和 Spartan-6 FPGA 系列的真正创新功能和特性。”

连接功能套件

连接开发套件包含目标参考设计,其将FPGA 内的硬件模块、赛灵思连接 IP 以及赛灵思联盟计划重要成员Northwest Logic公司提供的DMA IP整合在一起,提供全面可扩展的 PCIe 到 XAUI 或千兆位以太网的桥接器。

嵌入式开发套件

嵌入式开发套件帮助软件开发人员利用与ISE 11.4嵌入式版本一起提供的赛灵思 SDK(软件开发套件)环境立即启动开发工作。开发人员能运行并修改作为目标参考设计的一部分所提供的代码样本,充分利用全面实施的 MicroBlaze 32 位 RISC 软处理器内核和全套常见处理器外设,包括 UART、多端口存储控制器 (MPMC)、闪存、三态以太网 MAC (TEMAC)、通用 IP (GPIO)、I2C/SPI、定时器/中断控制器及调试端口等。

举报

举报

举报

举报

举报

举报