设计优化

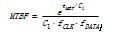

MTBF 方程中的指数因子意味着增大设计相关tMET 值能够指数增大同步器MTBF。例如,如果某一器件的常数C2,设置工作条件为50 ps,那么, tMET 只需要增大200 ps,就能够实现指数200/50,提高MTBF e4 倍,即50 多倍,而增大400 ps,提高MTBF e8 倍,即3000 倍。

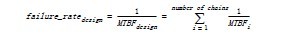

另一方面,最差MTBF 链对设计MTBF 的影响最大。例如,考虑具有10 个同步链的两个不同设计。一个设计的10 个链有相同的10,000 年MTBF,另一设计的9 个链有一百万年的MTBF,但是一个链的MTBF为100 年。设计失败概率是每一链的失败概率之和,失败概率为1/MTBF。第一个设计的亚稳态失败概率为10 个链× 1/10,000 年 = 0.001,因此,设计MTBF是1000 年。第二个设计的失败概率为9 个链 × 1/1,000,000 +1/100 = 0.01009,设计MTBF 为99 年,略小于最差链的MTBF。

换言之,设计较差的同步链决定了设计的亚稳态总MTBF。由于这一效应,对所有异步信号和时钟域传输进行亚稳态分析非常重要。设计人员或者工具供应商提高最差MTBF 同步链的tMET ,会对设计MTBF 有很大的影响。

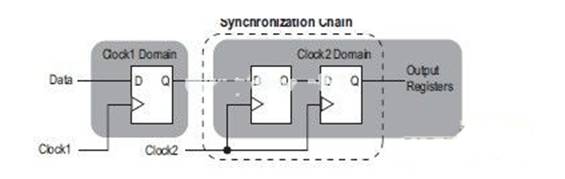

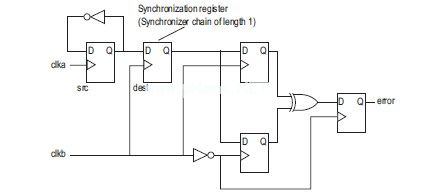

为提高亚稳态MTBF,设计人员可以在同步寄存器链上增加额外的寄存器级,以提高tMET 。增加的每一寄存器至寄存器连接时序余量被加到tMET 值中。设计人员一般使用两个寄存器来同步信号,而Altera 建议使用三个寄存器作为标准,以实现更好的亚稳态保护。然而,增加一个寄存器会在同步逻辑中加入额外的延时级,因此,设计人员必须综合考虑这是否可行。

如果设计使用Altera FIFO 宏功能,跨时钟域使用单独的读写时钟,那么,设计人员可以增强亚稳态保护(和延时),实现更好的MTBF。Altera Quartus II MegaWizard™ 插件管理器提供增强亚稳态保护选项,包括三个甚至更多的同步级 。

Quartus II 软件还提供业界最好的亚稳态分析和优化功能,以增大同步寄存器链的tMET。确定同步器后,软件将同步寄存器靠近放置,以增加同步链的输出时序余量,然后报告亚稳态MTBF。 function ImgZoom(Id)//重新设置图片大小 防止撑破表格 { var w = $(Id).width; var m = 650; if(w

结论

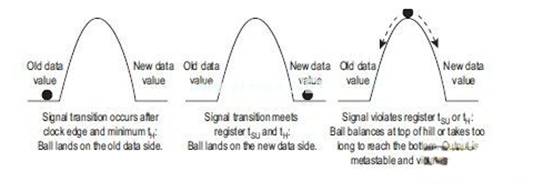

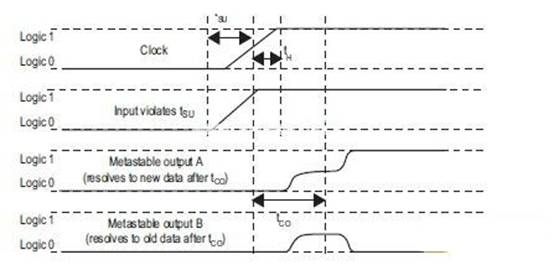

信号在不相关或者异步时钟域电路之间传输时,会出现压稳态问题。亚稳态失败平均时间间隔与器件工艺技术、设计规范和同步逻辑的时序余量有关。FPGA 设计人员可以通过增大tMET ,采用增加同步寄存器时序余量等设计方法来提高系统可靠性,增大亚稳态MTBF。Altera 确定了其 FPGA 的MTBF 参数,改进器件技术,从而增大了亚稳态MTBF。使用Altera FPGA 的设计人员可以利用Quartus II 软件功能来报告设计的亚稳态MTBF,优化设计布局以增大MTBF。

设计优化

MTBF 方程中的指数因子意味着增大设计相关tMET 值能够指数增大同步器MTBF。例如,如果某一器件的常数C2,设置工作条件为50 ps,那么, tMET 只需要增大200 ps,就能够实现指数200/50,提高MTBF e4 倍,即50 多倍,而增大400 ps,提高MTBF e8 倍,即3000 倍。

另一方面,最差MTBF 链对设计MTBF 的影响最大。例如,考虑具有10 个同步链的两个不同设计。一个设计的10 个链有相同的10,000 年MTBF,另一设计的9 个链有一百万年的MTBF,但是一个链的MTBF为100 年。设计失败概率是每一链的失败概率之和,失败概率为1/MTBF。第一个设计的亚稳态失败概率为10 个链× 1/10,000 年 = 0.001,因此,设计MTBF是1000 年。第二个设计的失败概率为9 个链 × 1/1,000,000 +1/100 = 0.01009,设计MTBF 为99 年,略小于最差链的MTBF。

换言之,设计较差的同步链决定了设计的亚稳态总MTBF。由于这一效应,对所有异步信号和时钟域传输进行亚稳态分析非常重要。设计人员或者工具供应商提高最差MTBF 同步链的tMET ,会对设计MTBF 有很大的影响。

为提高亚稳态MTBF,设计人员可以在同步寄存器链上增加额外的寄存器级,以提高tMET 。增加的每一寄存器至寄存器连接时序余量被加到tMET 值中。设计人员一般使用两个寄存器来同步信号,而Altera 建议使用三个寄存器作为标准,以实现更好的亚稳态保护。然而,增加一个寄存器会在同步逻辑中加入额外的延时级,因此,设计人员必须综合考虑这是否可行。

如果设计使用Altera FIFO 宏功能,跨时钟域使用单独的读写时钟,那么,设计人员可以增强亚稳态保护(和延时),实现更好的MTBF。Altera Quartus II MegaWizard™ 插件管理器提供增强亚稳态保护选项,包括三个甚至更多的同步级 。

Quartus II 软件还提供业界最好的亚稳态分析和优化功能,以增大同步寄存器链的tMET。确定同步器后,软件将同步寄存器靠近放置,以增加同步链的输出时序余量,然后报告亚稳态MTBF。 function ImgZoom(Id)//重新设置图片大小 防止撑破表格 { var w = $(Id).width; var m = 650; if(w

结论

信号在不相关或者异步时钟域电路之间传输时,会出现压稳态问题。亚稳态失败平均时间间隔与器件工艺技术、设计规范和同步逻辑的时序余量有关。FPGA 设计人员可以通过增大tMET ,采用增加同步寄存器时序余量等设计方法来提高系统可靠性,增大亚稳态MTBF。Altera 确定了其 FPGA 的MTBF 参数,改进器件技术,从而增大了亚稳态MTBF。使用Altera FPGA 的设计人员可以利用Quartus II 软件功能来报告设计的亚稳态MTBF,优化设计布局以增大MTBF。

举报

举报

举报

举报

举报

举报

举报

举报