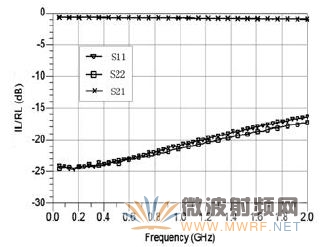

设计了一种低插入损耗、高隔离度的全集成超宽带CMOS射频收发开关芯片。该电路采用深N阱体悬浮技术,在1.8V电压供电下,该射频开关收发两路在0.1-1.2GHz内的测试结果具有0.7dB的插入损耗、优于-20dB的回波损耗以及-37dB以下的隔离度。

目前,全球无线通信系统正处于快速发展进程中,无线通信“行业专网”系统也正处于飞速发展的黄金时期。我国无线通信行业专网所用频点和带宽种类繁多,其频率 主要集中在0.1-1.2GHz。各专网使用不同的频点、射频带宽和信号带宽,标准不统一,导致各行业专网设备所用的射频芯片不同,同时对各个窄带射频前 端芯片的需求难以形成规模效应,且成本高、配套困难。目前行业专网所用的窄带射频前端芯片多数被国外公司所垄断,因此我们国家迫切的需要一套面向 0.1-1.2GHz行业专网频段的无线宽带射频收发芯片,以满足新一代宽带无线移动通信网的基本需求。

射频无线收发芯片已经在手机、 雷达、无线局域网(WLAN)及广播等多个窄带或宽带无线收发系统中得到了广泛应用。从频域来看,超宽带与传统的窄带和宽带有着明显的区别,超宽带的相对 带宽(信号带宽与中心频率之比)通常要在25%以上。此,0.1-1.2GHz频段无线宽带射频收发芯片属于超宽带电路。目前,在CMOS工艺下,国 际、国内尚无成熟商用超宽带射频收发芯片解决方案可以满足该频段的设计需求。

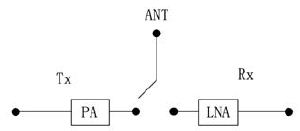

无线超宽带射频收发芯片由射频收发开关(T/R Switch)、低噪声放大器(LNA)、混频器(Mixer)、功率放大器(PA)、滤波器等多个电路模块组成。射频收发开关(T/R switch)作为无线宽带收发芯片的最前端电路,主要作用是控制整个收发机芯片的接收与发射状态的切换(如图1所示),它连接着收发天线、低噪声放大器和 功率放大器,是收发芯片中的关键模块。传统射频收发开关的制造工艺有很多,目前市场常见的产品绝大部分采用的是III-V族工艺或者PIN二极管等分立器 件。这类开关的优点是功耗较低,并且隔离度较好。然而它们的缺点是成本高、功耗大,并且占用面积也较大。随着工艺技术的不断发展,CMOS技术因其具有高 集成度、低成本和低功耗等突出优点,使得采用CMOS工艺实现射频收发开关已经成为一种必然的趋势。

图1 射频收发开关工作原理图

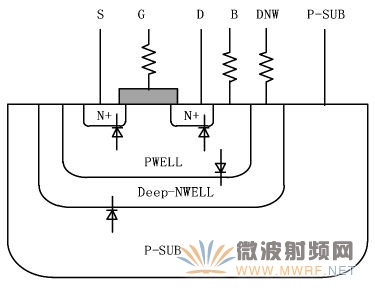

插入损耗、隔离度和线性度,是衡量射频收发开关特性的三个关键指标,除此之外,回波损耗也是一项主要指标。传统的对称式射频收发开关普遍采用普通的四个 NMOS管串并联结构进行设计。这种结构的优点是隔离度较好,但是一定程度上会恶化插入损耗和线性度,其典型仿真插入损耗为1dB左右。2008年,在基本的NMOS管串联结构基础上,采用深N阱工艺的NMOS器件,运用一种改进型的体悬浮(body-floating)技术,实现了 一个宽带射频收发开关。与传统的串并联结构开关电路相比,该结构具有更高的线性度以及更低的插入损耗等优点。

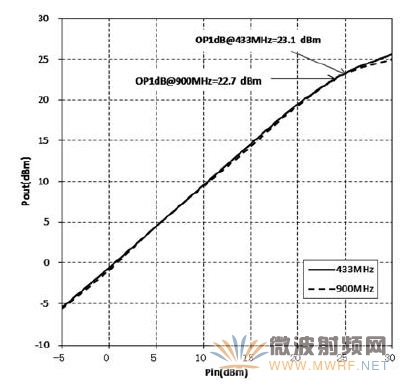

本文中所设计的 射频收发开关是在典型的串并联结构的电路基础上,结合参考文献中所述的衬底悬浮技术,实现了各项指标的良好折中。本文中的开关电路不仅具有较高的隔 离度特性,并且在线性度上也会有较大的改善。测试结果显示,该射频开关在0.1-1.2GHz频段内实现了低于-37dB隔离度和0.7dB的插入损耗, 基于RFID 433MHz及GSM-R 900MHz典型应用频段中,具有高于22dBm的1dB压缩点。

那么我们具体该如何设计0.1-1.2GHz的CMOS射频收发开关芯片呢?

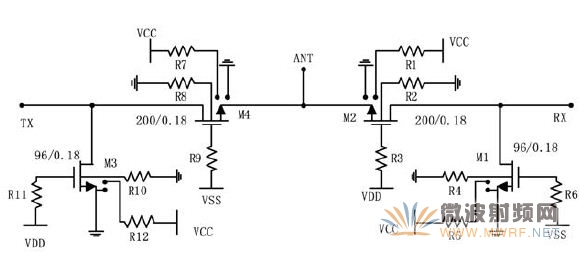

图3 宽带射频收发开关设计原理图

图3 宽带射频收发开关设计原理图

举报

举报

举报

举报

更多回帖