带模数前端的低成本微控制器近年来得到迅速推广,人们通常称之为“混合信号微控制器”。当然,赛普拉斯的 PSoC3 和新近推出的 PSoC5 器件集成了强大的 CPU 和业界领先的 ADC,其性能可超过分离式外部转换器。不过,PSoC3 和PSoC5 并不仅仅是一般的混合信号微控制器。传统设备当然可以将外部模拟信号转换为数字信号。数据采集进程并不是全部目的之所在,它只是通过数据采集提取所采集数据背后含义并确定如何处理数据的一种方式。如果提取含义所需的信号处理工作量非常大的话,就会对固件工程师构成挑战,因为这种提取工作要与一般性工作任务使用相同的处理器,而处理器在支持终端设备所需的一般性任务之外还要完成新的工作任务。

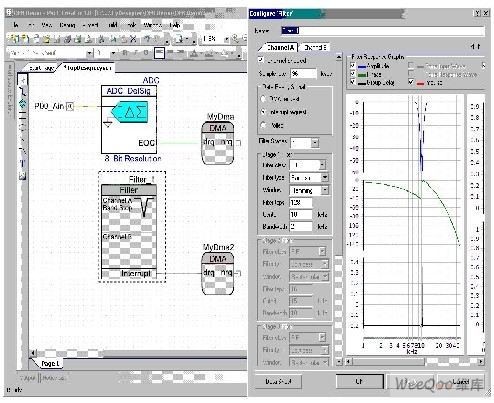

在定义关系密切的 PSoC3 和 PSoC5 系列产品时,赛普拉斯的架构师决定不再在竞争激烈的市场中仅仅提供一款同质化的产品。不管采取什么架构,硬件的功能都应重点用于高效地实现有用的工作目的。我们希望 PSoC 真正成为片上可编程解决方案,能够解决实际客户遇到的实际问题。为了给新一代 PSoC 器件提供更强的解决问题的功能,我们采用了一系列独特的外设和信号处理块,既有模拟的,也有数字的。本文将重点讨论这些大幅简化采集信号数字滤波工作的信号处理块,并讨论PSoC3和PSoC5的嵌入式数字滤波技术有哪些应用?

举报

举报

举报

举报

举报

举报

更多回帖