从理论上来说,DAC可以将数字信号正确无误的转换成等效的模拟信号,但实际上,转换过程几乎不可能是完美的。DAC的数字分辨率会引入量化误差,当将DAC的输出信号通过频谱分析仪显示时,这种误差表现为本底噪声。此外,其它误差,例如线性度误差,会造成DAC输出频谱上出现不期望的谐波分量,这些谐波往往是限制DAC无杂散动态范围(SFDR)性能的一个因素。

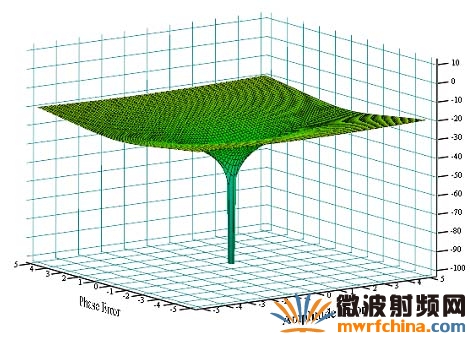

一般说来,谐波并不是一个严重的问题,因为人们往往不费多大气力就可以将其从输出频谱中滤除。不过,通过DAC将数字信号转换为模拟信号的过程属于采样理论所支配的研究领域,根据大量记载的数字信号处理的各种定理可以得知,谐波信号并不总是出现在容易观察到的频率点上。例如,假定一个以100 MHz采样的DAC可以产生一路频率为26MHz的正弦信号,可以预料到,其三次谐波会出现在78 MHz频率处,这可以轻松地滤除。事实上,由于采样的影响,在22 MHz处还会出现一个三次谐波的镜像。该镜像距离26 MHz的基频信号只有4 MHz的间隔,这使得滤除谐波信号的工作难度大大增加。显然,如果谐波可以有选择性的衰减,则DAC的SFDR性能将得到极大的提升。

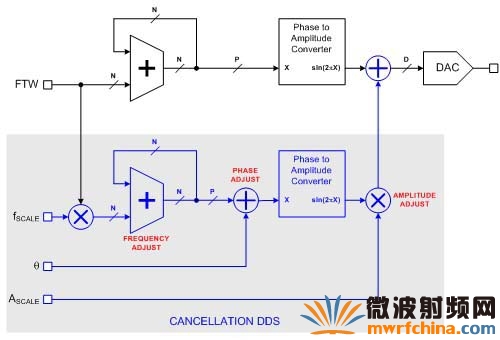

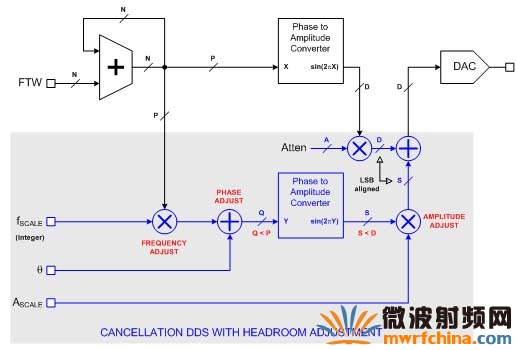

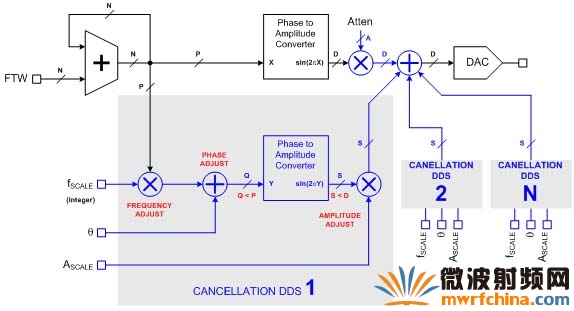

DDS的主要功能是产生正弦波。合成正弦波的质量的一个关键衡量标准是谐波失真。正如上面所解释的那样,DAC所引入的谐波失真往往是限制DDS中SFDR性能提高的因素。目前改善SFDR的解决方案是频率规划和/或在DAC输出端添加外部滤波电路,但这些方法往往并不适用,尤其在采样的影响下,谐波非常接近基频信号。

从理论上来说,DAC可以将数字信号正确无误的转换成等效的模拟信号,但实际上,转换过程几乎不可能是完美的。DAC的数字分辨率会引入量化误差,当将DAC的输出信号通过频谱分析仪显示时,这种误差表现为本底噪声。此外,其它误差,例如线性度误差,会造成DAC输出频谱上出现不期望的谐波分量,这些谐波往往是限制DAC无杂散动态范围(SFDR)性能的一个因素。

一般说来,谐波并不是一个严重的问题,因为人们往往不费多大气力就可以将其从输出频谱中滤除。不过,通过DAC将数字信号转换为模拟信号的过程属于采样理论所支配的研究领域,根据大量记载的数字信号处理的各种定理可以得知,谐波信号并不总是出现在容易观察到的频率点上。例如,假定一个以100 MHz采样的DAC可以产生一路频率为26MHz的正弦信号,可以预料到,其三次谐波会出现在78 MHz频率处,这可以轻松地滤除。事实上,由于采样的影响,在22 MHz处还会出现一个三次谐波的镜像。该镜像距离26 MHz的基频信号只有4 MHz的间隔,这使得滤除谐波信号的工作难度大大增加。显然,如果谐波可以有选择性的衰减,则DAC的SFDR性能将得到极大的提升。

DDS的主要功能是产生正弦波。合成正弦波的质量的一个关键衡量标准是谐波失真。正如上面所解释的那样,DAC所引入的谐波失真往往是限制DDS中SFDR性能提高的因素。目前改善SFDR的解决方案是频率规划和/或在DAC输出端添加外部滤波电路,但这些方法往往并不适用,尤其在采样的影响下,谐波非常接近基频信号。

举报

举报

举报

举报

举报

举报

举报

举报