2 DSP电路设计

DSP选用TI公司的DM648处理器,DM648是TI公司为视频处理应用开发的一款高性能低功耗处理器,它集成了5个视频端口和图像协处理器,主要具有以下特性:

(1)处理内部主频1.1GHz,处理速度达到8800MIPS,每个时钟周期可以执行8个32位C64Xx+指令;

(2)具有32kb的LIPProgramRAM和32kb的L1DDataRAM:

(3)具有支持512kbyte的L2UnifiedMappedRAM;

(4)支持小端模式;

(5)具有5个可配置的视频口;

(6)集成外部EMIFS存储器管理接口,可管理512Mbytes的DDR2SDRAM和128Mbytes的FLASH;

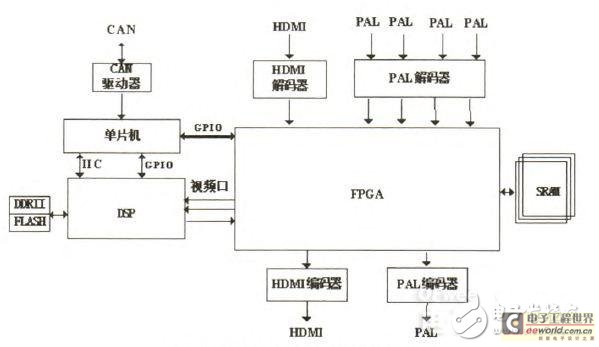

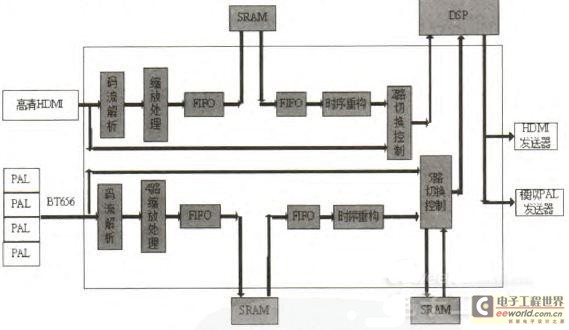

本设计中,DSP通过专用的DDRII接口外接512MB的DDRII存储器,通过EMIF接口外接32MB的FLASH。DSP的专用视频口,配置成 2个输入视频端口和1个视频输出端口,输入视频端口接收FPGA送来的视频数据,输入视频端口既可以接收16bit的高清YCrCb数据,也可以接收符合 BT656标准的8bit标清YCrCb数据;输出视频端口输出符合BT656标准的8bit标清YCrCb数据,DSP将输出的视频数据送给FPGA。

2 DSP电路设计

DSP选用TI公司的DM648处理器,DM648是TI公司为视频处理应用开发的一款高性能低功耗处理器,它集成了5个视频端口和图像协处理器,主要具有以下特性:

(1)处理内部主频1.1GHz,处理速度达到8800MIPS,每个时钟周期可以执行8个32位C64Xx+指令;

(2)具有32kb的LIPProgramRAM和32kb的L1DDataRAM:

(3)具有支持512kbyte的L2UnifiedMappedRAM;

(4)支持小端模式;

(5)具有5个可配置的视频口;

(6)集成外部EMIFS存储器管理接口,可管理512Mbytes的DDR2SDRAM和128Mbytes的FLASH;

本设计中,DSP通过专用的DDRII接口外接512MB的DDRII存储器,通过EMIF接口外接32MB的FLASH。DSP的专用视频口,配置成 2个输入视频端口和1个视频输出端口,输入视频端口接收FPGA送来的视频数据,输入视频端口既可以接收16bit的高清YCrCb数据,也可以接收符合 BT656标准的8bit标清YCrCb数据;输出视频端口输出符合BT656标准的8bit标清YCrCb数据,DSP将输出的视频数据送给FPGA。

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报