library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

en

tity test is

port(

clkin:in std_logic;

en:in std_logic;

data_in:in std_logic_vector(15 downto 0);

clk_outut std_logic;

data_outut std_logic);

end entity;

architecture behave of test is

signal ien:std_logic;

signal clk_temp:std_logic;

signal clk_out_temp:std_logic;

signal reset:std_logic;

signal icnt:std_logic;

signal iicnt:std_logic;

signal cnt:integer;

begin

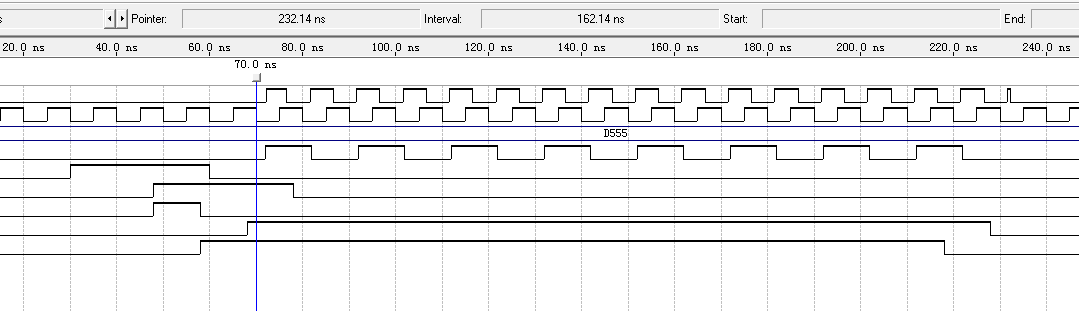

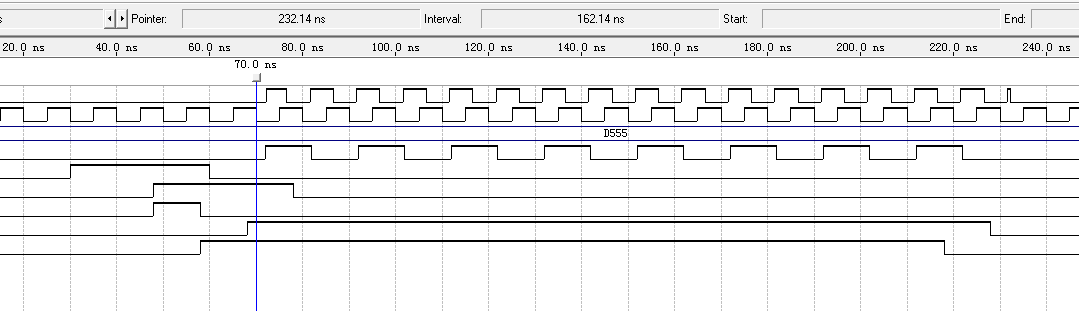

clk_out<=iicnt and clkin;

process(clkin)

begin

if rising_edge(clkin) then

ien<=en;

end if;

end process;

process(clkin)

begin

if rising_edge(clkin) then

iicnt<=icnt;

end if;

end process;

process(clkin,en)

begin

if rising_edge(clkin) then

if en='1' and ien='0' then

reset<='1';

else

reset<='0';

end if;

end if;

end process;

process(clkin,en,reset)

begin

if rising_edge(clkin) then

if reset='1' then

cnt<=0;

icnt<='1';

elsif icnt='1' then

data_out<=data_in(cnt);

cnt<=cnt+1;

if cnt>=15 then

icnt<='0';

cnt<=cnt;

end if;

else

if icnt='0' then

data_out<='0';

end if;

end if;

end if;

end process;

end behave;

举报

举报

举报

举报

举报

举报

举报

举报