我写的很长很细。希望了解的朋友能帮助我一下。做不出来就毕不了业了。如果能得到大家的帮助,等我调试完成,会在网站上上传相应的文件盒详细调试记录。谢谢大家。

[size=11.818181991577148px]最近调试AD9957+FPGA

[size=11.818181991577148px]打算先调单音模式

结果调试不出来。

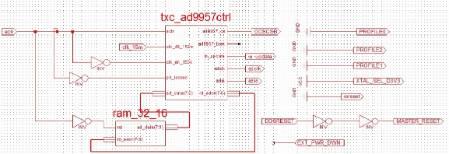

先上一张AD9957配置的相关信息:

这是我FPGA内的AD9957的配置方式

SPI的时钟用的是16M的。

PROFILE<0:2>拉低

芯片的ioreset拉低

晶振工作模式选择管脚XTAL_SEL拉高到3.3V)(我要用无源晶振)

芯片复位管脚MASTER_RESET接到外部开关,进行复位操作

EXT_PWR_DWN信号硬件

电路上做了拉低,因此只在FPGA内设置为输入,以防影响工作

以上是我对硬件的所有配置了。

目前使用的晶振为官网电路中用的无源晶振:HC49SD_25MHZ,电容也用的官网值39pF

问题1 首先是SPI时序

主要信号对应为

sdclk--sclk

io_updata--

io_updata

sdio--sdio

ad9957_CS(DDSCSB)--CSB

上图是我写的SPI时序的开头部分。SCLK初始时是常高的。采用的是默认格式是MSB 优先格式

开头的00是CFR1的写入指令0000-0000,01是CFR1<31-24>0000-0001,写完CFR1全部字节后紧接着是CFR2的地址和全部配置字节,如此从地址0x00写到0x19.

[size=11.818181991577148px] [size=11.818181991577148px]上图是SPI写完自后一个字节的时序。sclk拉高,io_updata拉高。

[size=11.818181991577148px]问题1、我想确认一下这样的时序到底对不对?我现在调试下来感觉没配置进去。

[size=11.818181991577148px]我看芯片手册上说,“I/O_UPDATE 在上升沿有效,脉冲宽度必须大于1 个SYNC_CLK 周期”

[size=11.818181991577148px]是不是意味着,要想SPI能将配置信息写进芯片,前提必须是AD9957的内部时钟工作正常?

[size=11.818181991577148px]问题2

[size=11.818181991577148px]无源晶振的问题

[size=11.818181991577148px]首先说一下寄存器配置方面的信息

[size=11.818181991577148px]CFR1 : 0x00010000 只选择了单音工作模式,其他默认值

[size=11.818181991577148px]CFR2 :0x00004020 只将22位设置为1,SYNC_CLK 使能,输出1/4的fsysclk,其他均默认值

[size=11.818181991577148px]CFR3 :0x3A3F8130

[size=11.818181991577148px]CFR3<7:0>=0x30:因为是25M的外部无源晶振,因此设置为24倍频,这样fsysclk时钟为600MHZ

[size=11.818181991577148px]CFR3<15:8>=0x81:使能PLL,旁路 输入分频器

[size=11.818181991577148px]CFR3<23:16>=0x3F:选取REFCLK PLL 中的电荷泵电流值为111b

[size=11.818181991577148px]CFR3<31:24>=0x3A:选取REFCLK PLL VCO 的频段:010 VCO2(468~709)

[size=11.818181991577148px]控制REFCLK_OUT 引脚 :11高电流值输出

[size=11.818181991577148px]Profile0寄存器:0xA0FF000015555555

[size=11.818181991577148px]幅度比例因子:0XFF00

[size=11.818181991577148px]相位偏移字:0,无偏移

[size=11.818181991577148px]频率调谐字:0x15555555,这样换算下来,输出的单音频率为50MHZ

[size=11.818181991577148px]其他寄存器均为默认值。

[size=11.818181991577148px]以上是配置信息

[size=11.818181991577148px]目前调试出来的结果很简单:

[size=11.818181991577148px]晶振不起振

[size=11.818181991577148px]单音无输出

[size=11.818181991577148px]每次AD9957复位后,SYNC_CLK 上会有很乱的波形。,但是一写SPI后,就常为低。

[size=11.818181991577148px]ADT1-1WT也是按照官网电路设计的,每次AD9957复位后,输出端会有约200mv的杂波,但是写SPI后,就消失了。

[size=11.818181991577148px]我想请教

[size=11.818181991577148px]0、我的SPI时序和AD9957的硬件配置是否正确,是否有遗漏?

[size=11.818181991577148px]1、XTAL_SEL拉高,是拉到3.3v吗

[size=11.818181991577148px]2、无源晶振起振,除了使能PLL,设置PLL频率区间和XTAL_SEL拉高外,是不是一定要把“外部PLL环路滤波器元件”的电路配置起来才行?我个人感觉,“外部PLL环路滤波器元件”只是优化PLL性能,不应该会影响无源晶振的起振。目前无源晶振两个管脚上都各有约1.13V的电压。但示波器量,无起振

[size=11.818181991577148px]4、我如果打算接外部有源晶振,那么我应该选择输出电压是多少的晶振。

[size=11.818181991577148px]事实上,我尝试向AD9957送入1.8V,16MHZ的晶振,并将配置信息进行改动,旁路PLL,使能输入分频器,拉低XTAL_SEL,但是依旧无法输出单音。

[size=11.818181991577148px]整个儿就感觉AD9957不想好好干活。(两块板,均如此)

[size=11.818181991577148px]我写的很长很细。希望了解的朋友能帮助我一下。做不出来就毕不了业了。如果能得到大家的帮助,等我调试完成,会在网站上上传相应的文件盒详细调试记录。谢谢大家。

[size=11.818181991577148px]上图是SPI写完自后一个字节的时序。sclk拉高,io_updata拉高。

[size=11.818181991577148px]问题1、我想确认一下这样的时序到底对不对?我现在调试下来感觉没配置进去。

[size=11.818181991577148px]我看芯片手册上说,“I/O_UPDATE 在上升沿有效,脉冲宽度必须大于1 个SYNC_CLK 周期”

[size=11.818181991577148px]是不是意味着,要想SPI能将配置信息写进芯片,前提必须是AD9957的内部时钟工作正常?

[size=11.818181991577148px]问题2

[size=11.818181991577148px]无源晶振的问题

[size=11.818181991577148px]首先说一下寄存器配置方面的信息

[size=11.818181991577148px]CFR1 : 0x00010000 只选择了单音工作模式,其他默认值

[size=11.818181991577148px]CFR2 :0x00004020 只将22位设置为1,SYNC_CLK 使能,输出1/4的fsysclk,其他均默认值

[size=11.818181991577148px]CFR3 :0x3A3F8130

[size=11.818181991577148px]CFR3<7:0>=0x30:因为是25M的外部无源晶振,因此设置为24倍频,这样fsysclk时钟为600MHZ

[size=11.818181991577148px]CFR3<15:8>=0x81:使能PLL,旁路 输入分频器

[size=11.818181991577148px]CFR3<23:16>=0x3F:选取REFCLK PLL 中的电荷泵电流值为111b

[size=11.818181991577148px]CFR3<31:24>=0x3A:选取REFCLK PLL VCO 的频段:010 VCO2(468~709)

[size=11.818181991577148px]控制REFCLK_OUT 引脚 :11高电流值输出

[size=11.818181991577148px]Profile0寄存器:0xA0FF000015555555

[size=11.818181991577148px]幅度比例因子:0XFF00

[size=11.818181991577148px]相位偏移字:0,无偏移

[size=11.818181991577148px]频率调谐字:0x15555555,这样换算下来,输出的单音频率为50MHZ

[size=11.818181991577148px]其他寄存器均为默认值。

[size=11.818181991577148px]以上是配置信息

[size=11.818181991577148px]目前调试出来的结果很简单:

[size=11.818181991577148px]晶振不起振

[size=11.818181991577148px]单音无输出

[size=11.818181991577148px]每次AD9957复位后,SYNC_CLK 上会有很乱的波形。,但是一写SPI后,就常为低。

[size=11.818181991577148px]ADT1-1WT也是按照官网电路设计的,每次AD9957复位后,输出端会有约200mv的杂波,但是写SPI后,就消失了。

[size=11.818181991577148px]我想请教

[size=11.818181991577148px]0、我的SPI时序和AD9957的硬件配置是否正确,是否有遗漏?

[size=11.818181991577148px]1、XTAL_SEL拉高,是拉到3.3v吗

[size=11.818181991577148px]2、无源晶振起振,除了使能PLL,设置PLL频率区间和XTAL_SEL拉高外,是不是一定要把“外部PLL环路滤波器元件”的电路配置起来才行?我个人感觉,“外部PLL环路滤波器元件”只是优化PLL性能,不应该会影响无源晶振的起振。目前无源晶振两个管脚上都各有约1.13V的电压。但示波器量,无起振

[size=11.818181991577148px]4、我如果打算接外部有源晶振,那么我应该选择输出电压是多少的晶振。

[size=11.818181991577148px]事实上,我尝试向AD9957送入1.8V,16MHZ的晶振,并将配置信息进行改动,旁路PLL,使能输入分频器,拉低XTAL_SEL,但是依旧无法输出单音。

[size=11.818181991577148px]整个儿就感觉AD9957不想好好干活。(两块板,均如此)

[size=11.818181991577148px]我写的很长很细。希望了解的朋友能帮助我一下。做不出来就毕不了业了。如果能得到大家的帮助,等我调试完成,会在网站上上传相应的文件盒详细调试记录。谢谢大家。