你好,

下面提供的是模拟锁相环(PLLYSCM)的自定义实现。

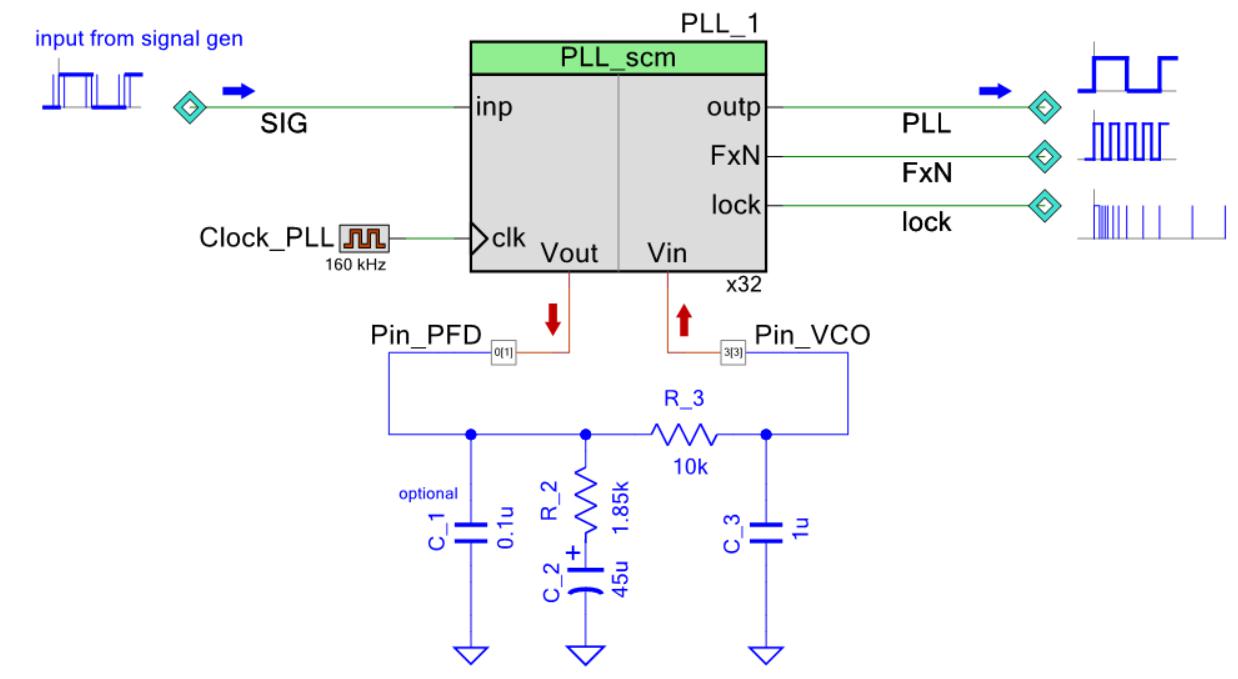

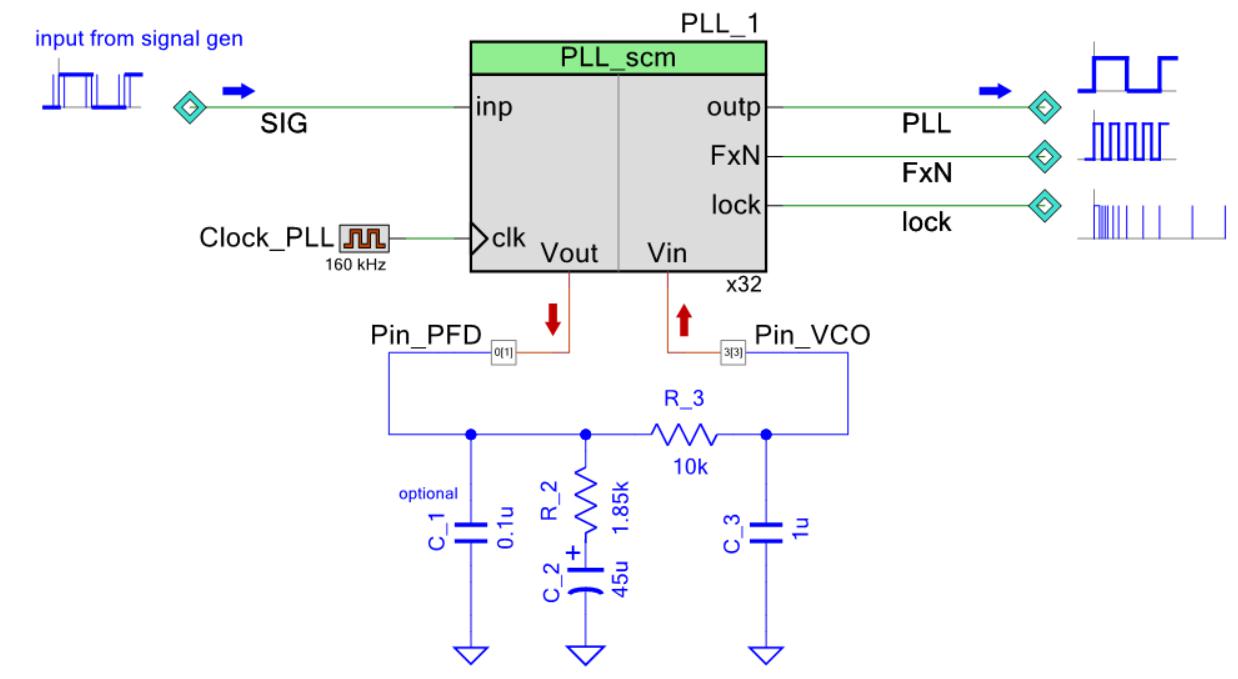

器件采用相位频率检测器(PFD)作为相位比较器和基于开关电容Δ∑调制器的压控振荡器。低通滤波器只需要很少的外部电容器和电阻器。PLLYSCM可以锁定数字信号,产生同一频率的一个输出,另一个乘以频率,两者都与输入相位对齐。该组件被设计为在低频(10Hz~10kHz)下工作,主要目标是跟踪交流

电源线(50-60Hz)。

组件作为RMS检测项目的一部分开发。它可以用于频率倍增,正交生成,电机控制,吉他音效等。

使用CY8KIT-059 PSOC5原型试剂盒进行了测试。提供了几个演示项目。

主要特点:

用II型鉴频器实现模拟锁相环。

使用第一阶Δ∑调制器作为VCO。

初级输出在频率和相位上都是锁定的。

倍频的二次输出。

输出用于可选的锁定检测。

不消耗CPU。

附加存档包含组件库、组件数据表和几个用于PSoC5的演示项目。请阅读Read M.TXT中的安装说明。

所提供的组成部分是,没有负债。它可以自由使用和修改。

YouTube视频显示组件在行动:

自定义锁相环(PLL)演示使用PSOC5微控制器-YouTube

当做,

奥迪赛1

拉链

3.4兆字节

邮编

2.1兆字节

PLLY-SMCMV0.0A.PDF

1.8兆字节

拉链

872字节

以上来自于百度翻译

以下为原文

Hi,

Provided below is a custom implementa

tion of analog Phase-Locked Loop (PLL_scm).

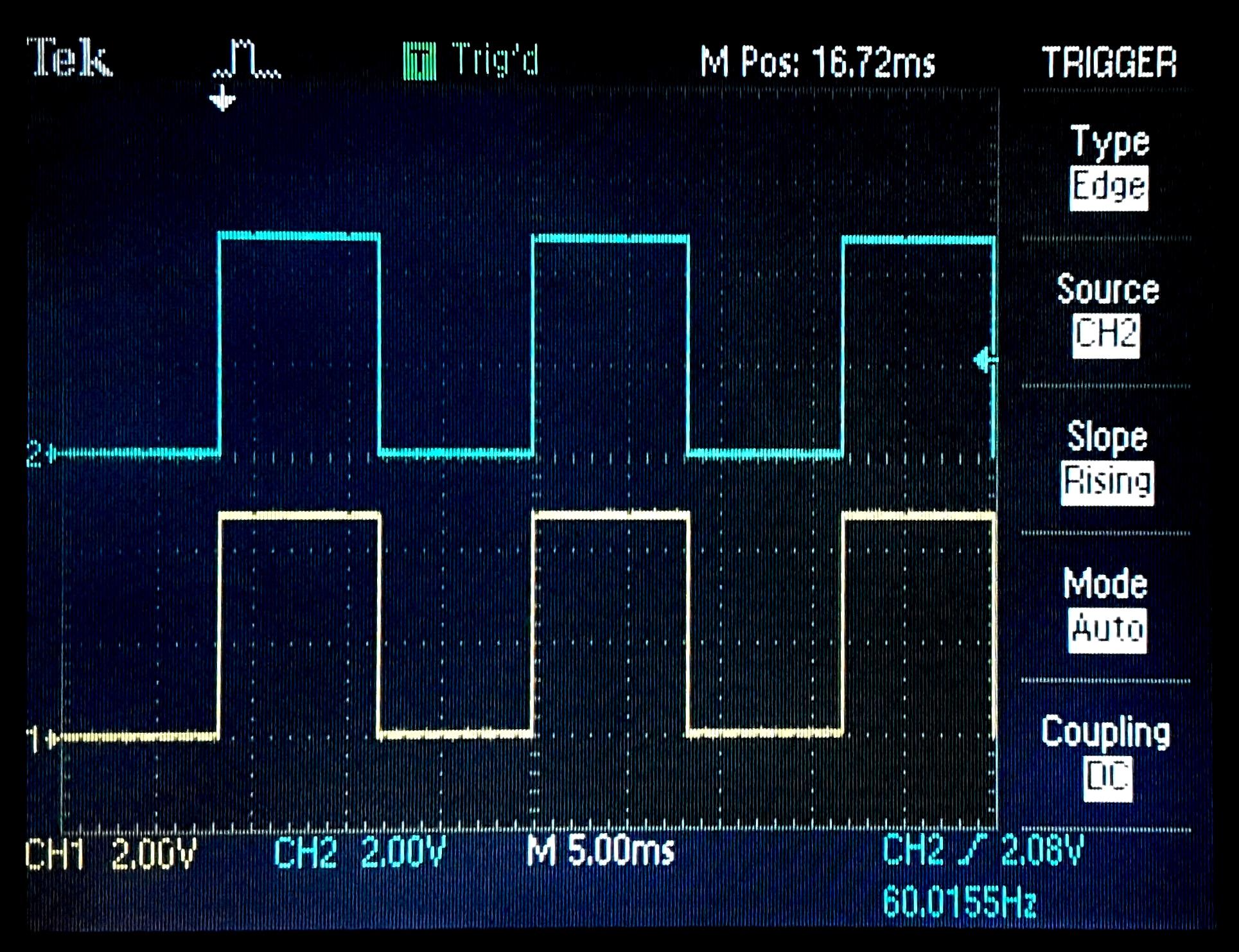

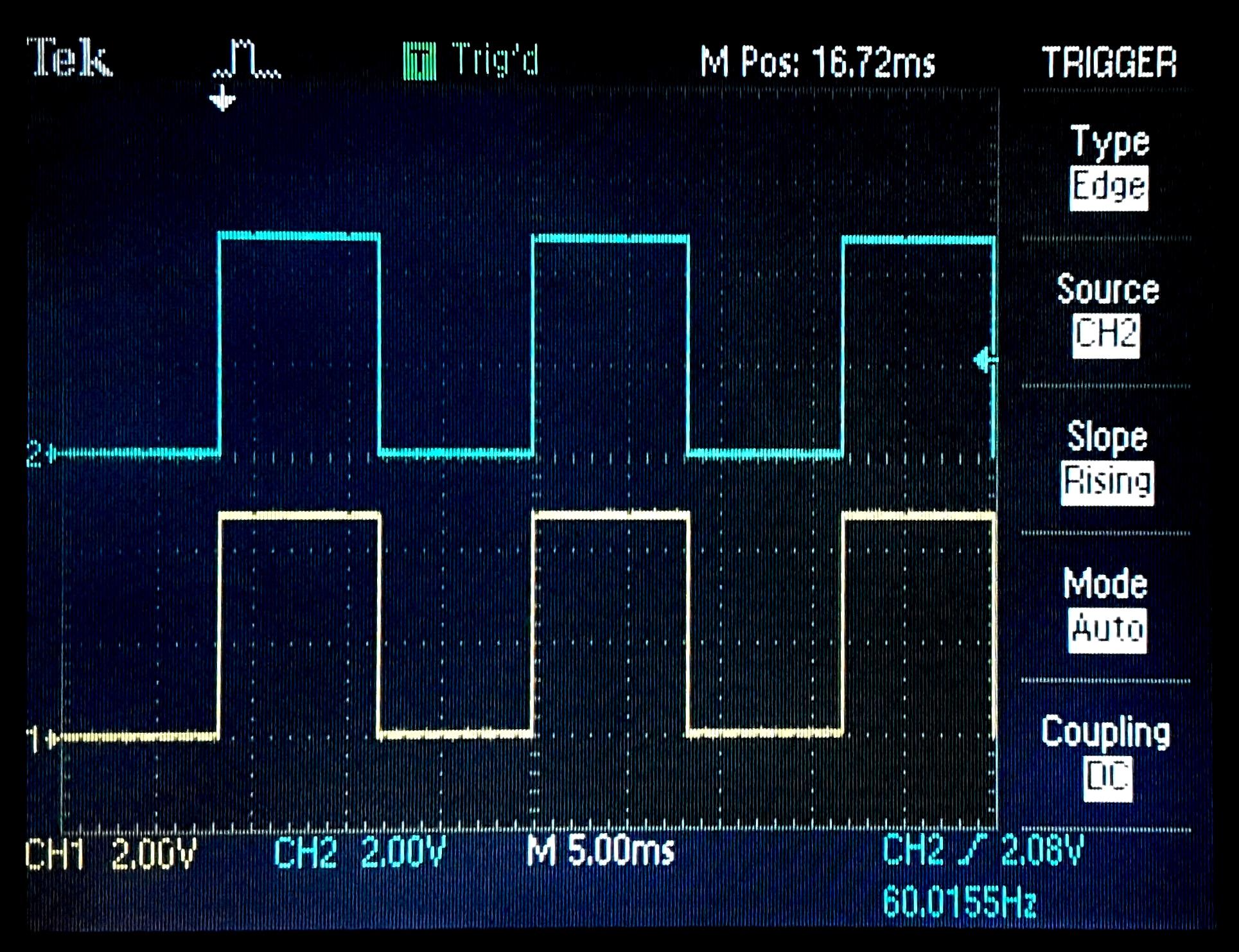

Component implements Phase-Frequency Detector (PFD) as phase comparator and voltage-controlled oscillator based on switched-capacitor delta-sigma modulator. Only few external capacitors and resistors required for low-pass filter. PLL_scm can lock to digital signal, producing one output of the same frequency, and another one of multiplied frequency, both are phase-aligned with the input. The component was designed to operate at low frequencies (10Hz–10kHz), with primary goal of tracking AC power lines (50-60 Hz).

Component was developed as part of RMS detection project. It can be useful for frequency multiplication, quadrature generation, motor control, guitar sound effects, etc.

It was tested using CY8KIT-059 PSoC5 prototyping kit. Several demo projects are provided.

Component Major features:

Implements analog PLL using Type-II Phase Frequency Detector.

Uses 1st-order delta-sigma modulator as VCO.

Primary output is locked in both frequency and phase.

Secondary output for multiplied frequency.

Output for optional lock detection.

Does not consume CPU.

Attached archive contains component library, component datasheet and several demo projects for PSoC5. Please read installation instructions in the readme.txt.

The component provided as-is, no liabilities. It is free to use and modify.

YouTube video showing component in action:

Custom Phase Lock Loop (PLL) demo using PSoC5 microcontroller - YouTube

regards,

odissey1

举报

举报

举报

举报