|

[]()

使用SF1的硬核

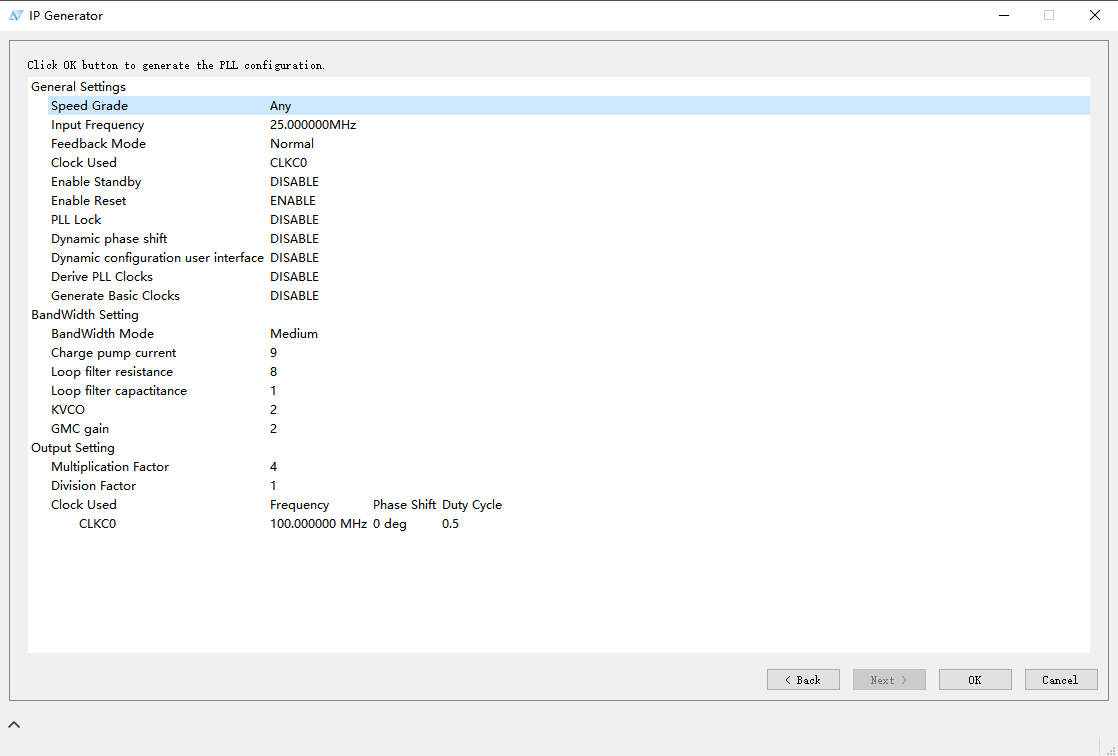

使用IP Generator生成RISC-V硬核和PLL核

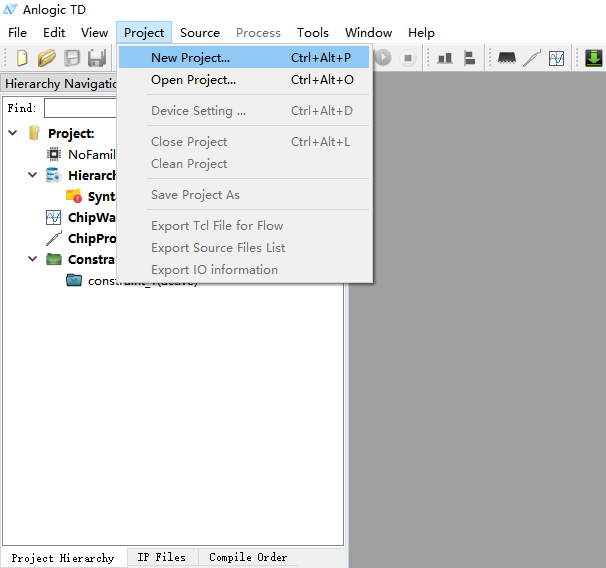

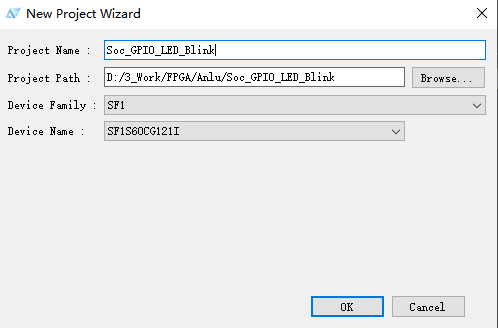

创建工程并选择器件为SF160CG121I。

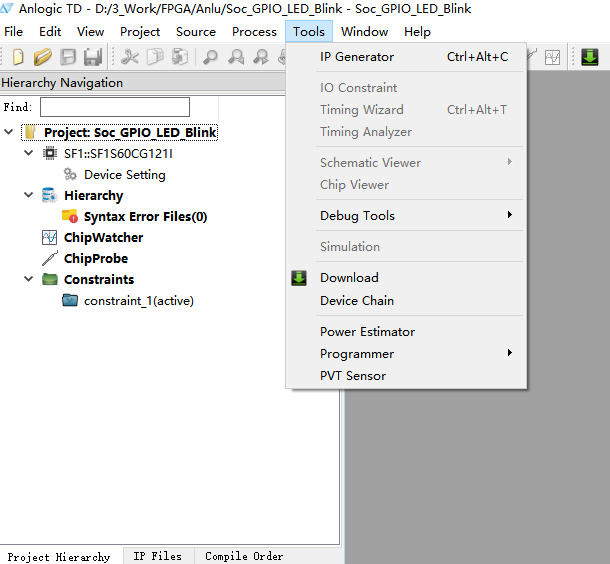

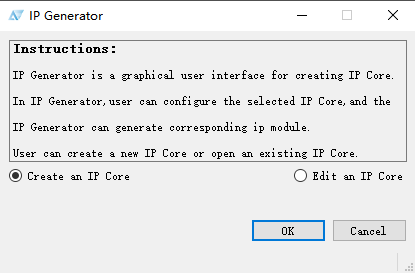

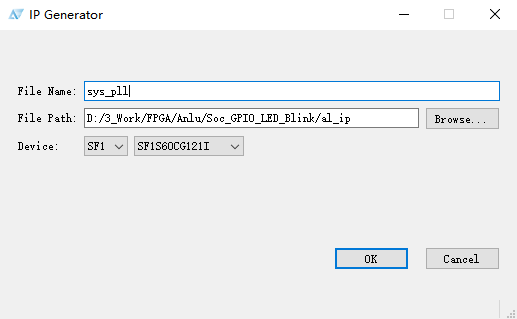

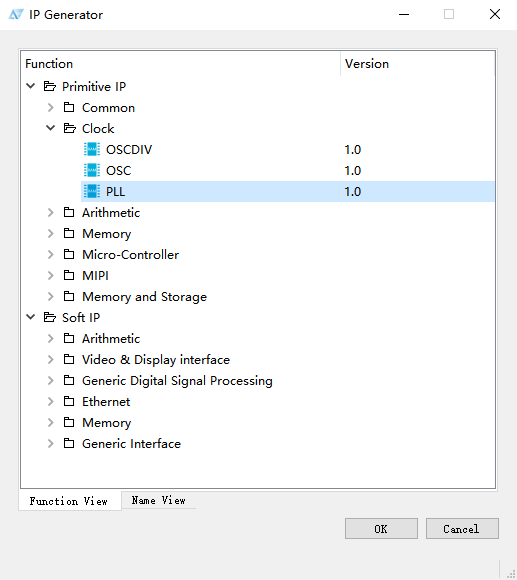

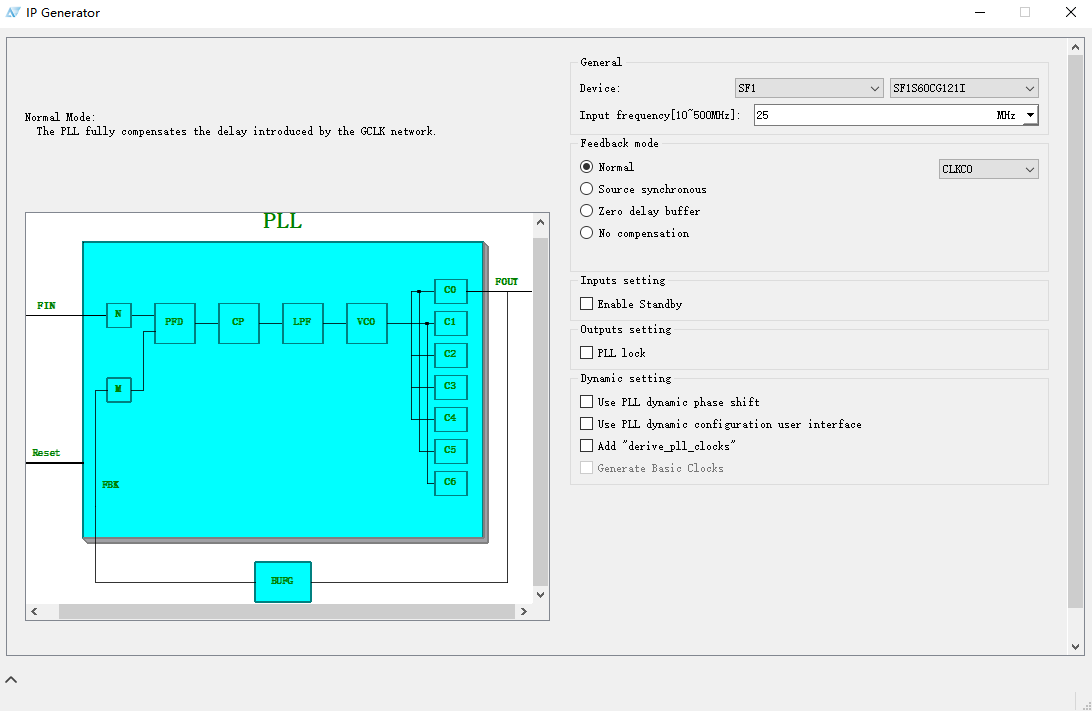

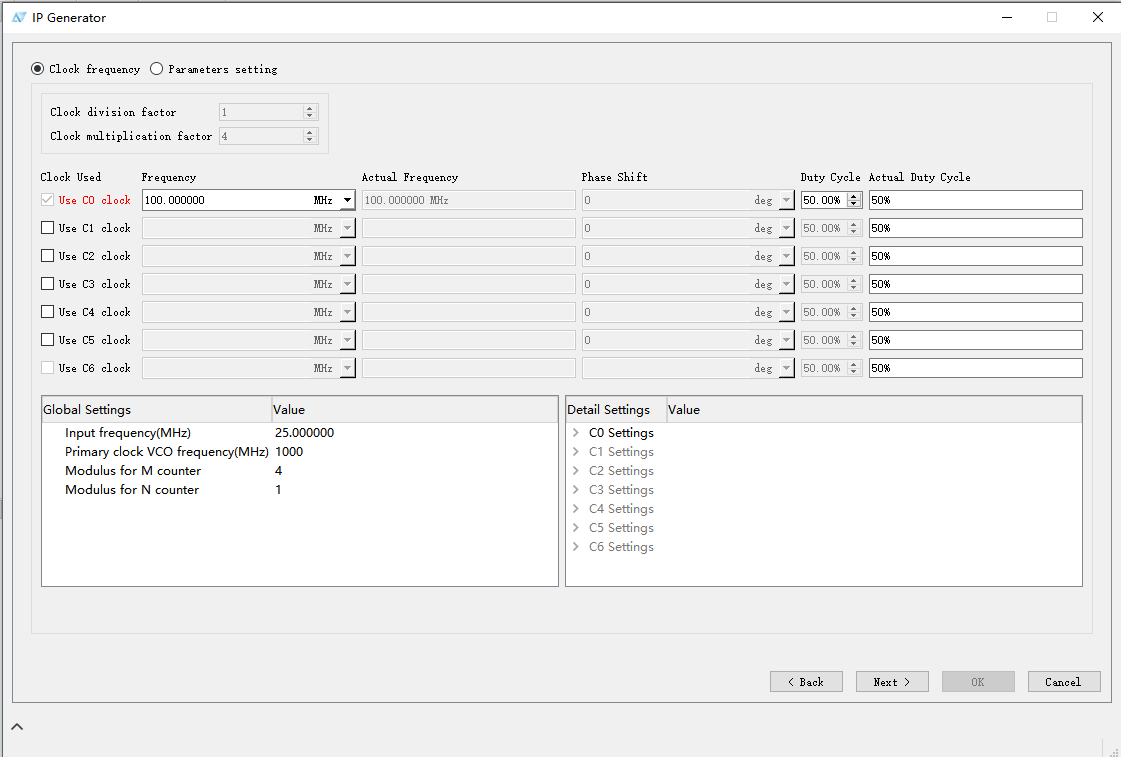

点击Tools->IP Generator,选择Create an IP core,生成RISC-V核SF1_MCU和PLL核sys_pll。

设计GPIO接口电路

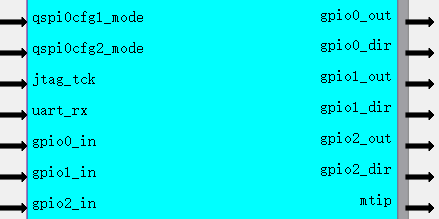

在创建SF1_MCU IP的时候,选中了3个GPIO输出,在左侧的示意图上会出现三组GPIO相关的端口。

每组端口由gpiox_in、gpiox_out、gpiox_dir(x=0,1,2,3….n),与FPGA的物理端口连接需要添加一个控制电路,该控制电路中gpio_dir控制物理端口和gpio0_in还是和gpio0_out相连接。具体代码如下:

设计SOC模块以及使用

结合上述配置好的RISC-V IP核和GPIO接口电路模块,组成一个可以供外部调用的SOC模块,具体代码如下:

在TOP模块中调用,SOC模块和PLL模块

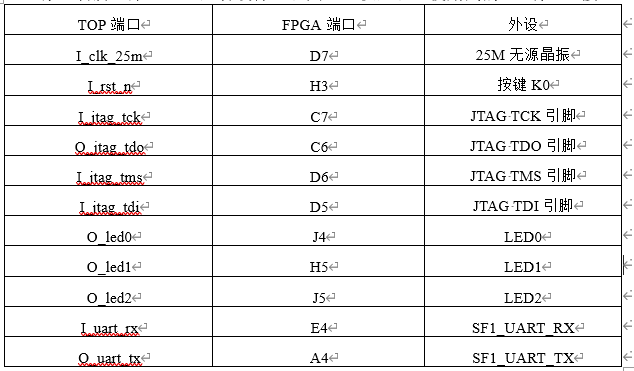

添加管脚约束,通过查看硬件原理图,可以整理出使用到的IO端口连接

添加完成IO约束和时序约束后,就可以生成位流文件,准备接下来的下载了。

RISC-V程序编写

上述过程完成了RISC-V硬核的实现,接下来需要在编写运行在RISC-V处理器上程序。

开发环境准备

SF1上的RISC-V硬核的程序是在Future Dynasty(FD)集成开发环境中进行的,开发工具直接将压缩包解压到硬盘上即可,注意在路径中不要有中文,否则会有乱码、编译器无法执行等问题。

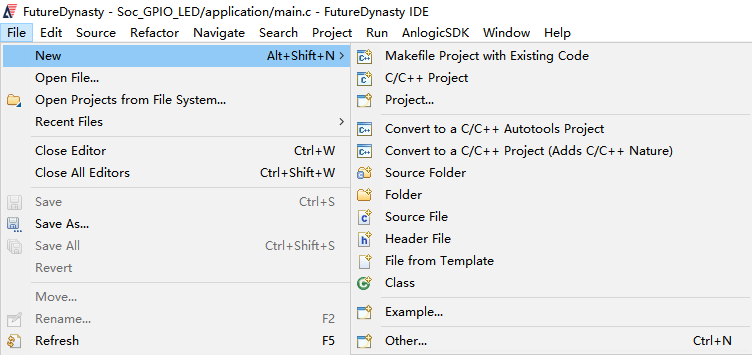

创建工程

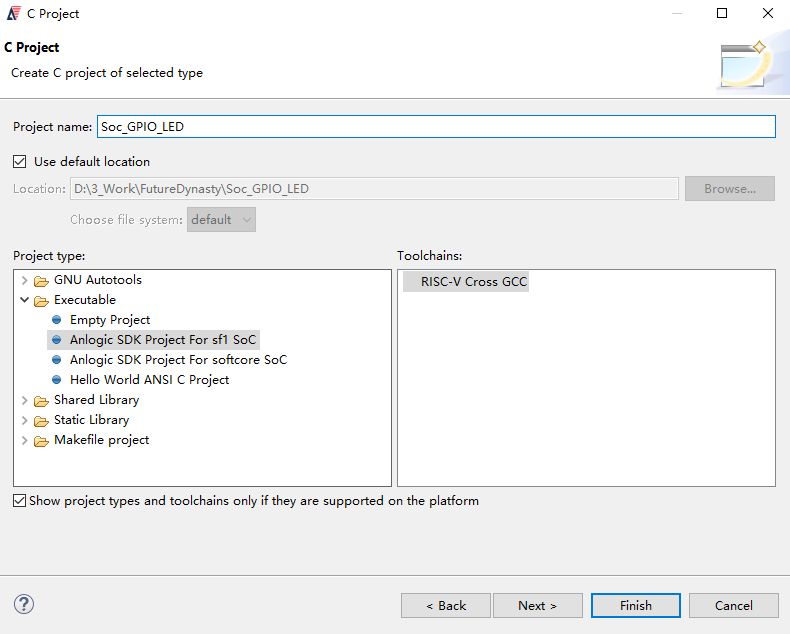

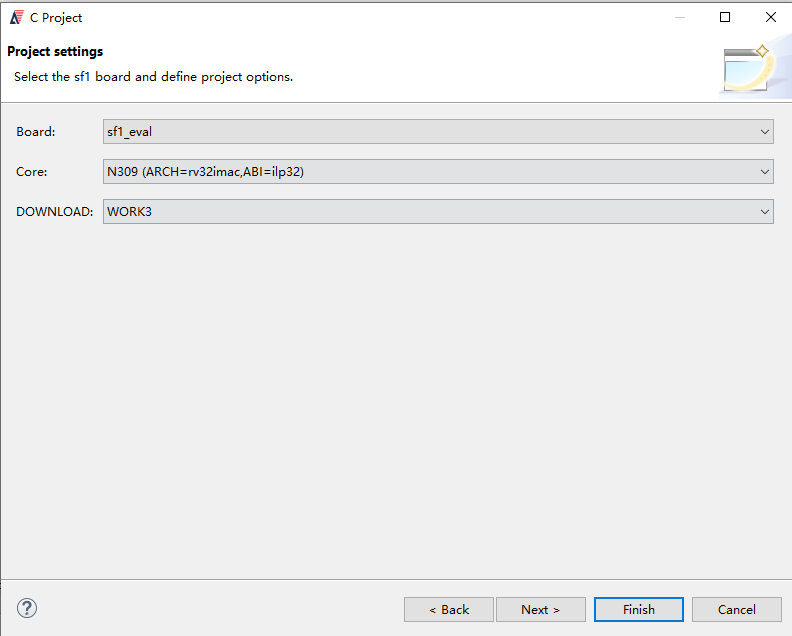

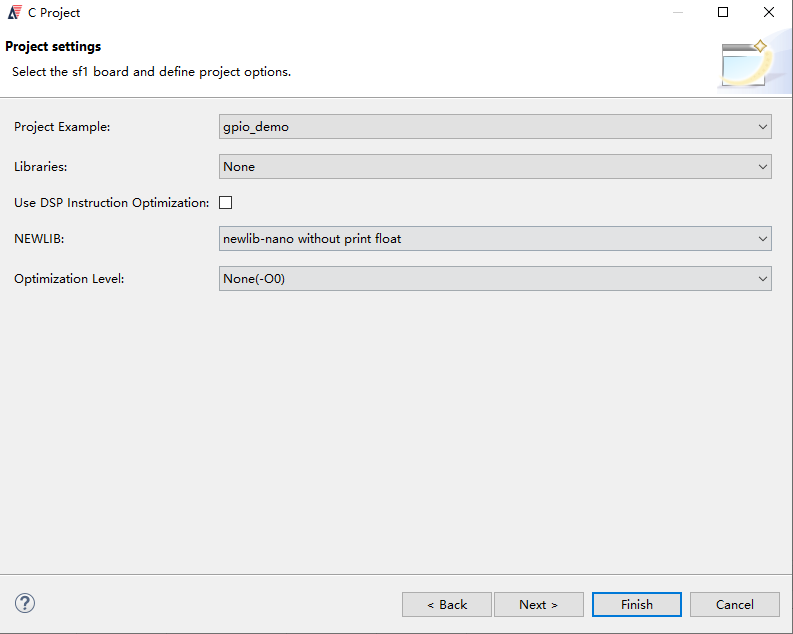

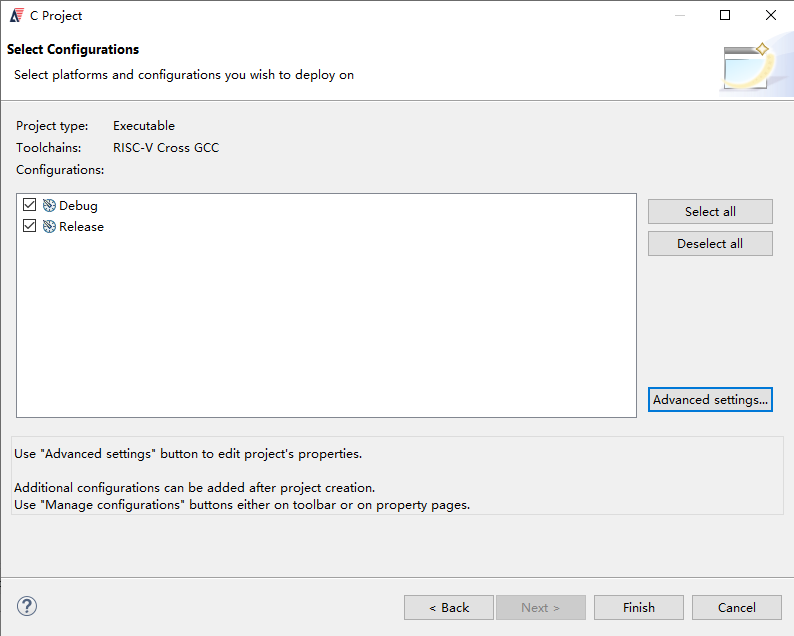

在File->New中选择Project,按下图中所示的流程创建gpio_demo工程。

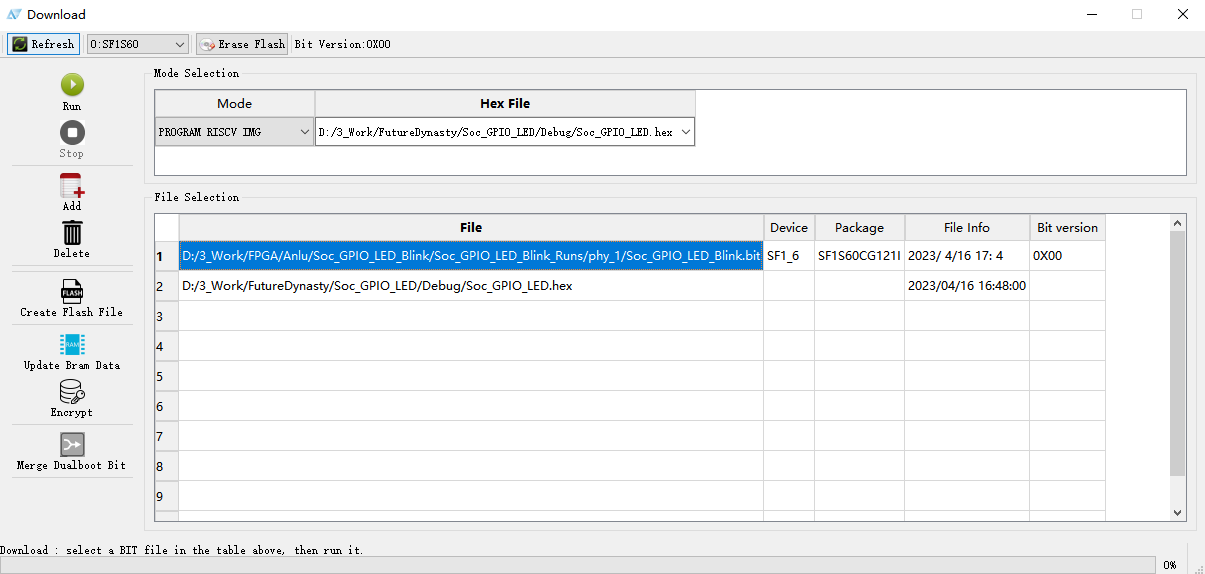

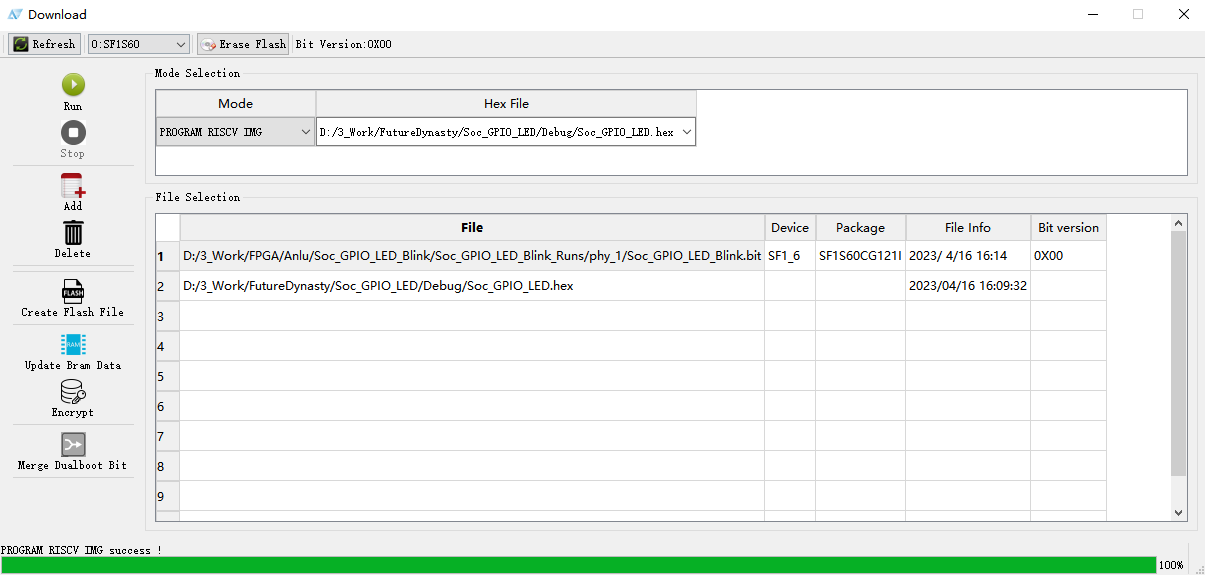

下载工程

创建完成后,无需修改代码,直接编译即可。在工程的Debug文件夹下查看可产生的二进制文件。回到TD软件中,点击工具栏中的Download按钮。在页面中选择FPGA的位留文件和RISC-V工程的Hex文件,下载方式选择PROGRAM RISCV IMG,下载时,记得点击文件列表中的位流文件,这样下载时才不会报错。

运行演示

09演示

|